问题:

Cadence Allegro Entry CIS-Creat Netlist时候出现了以下问题:Netlister failed.

解决办法:

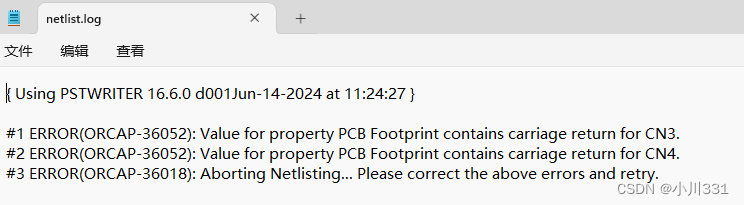

1.记事本打开netlist.log查看错误信息

错误信息指出CN3与CN4的PCB封装出现了回车,需要订正重试。

2.打开Allegro Entry CIS软件:

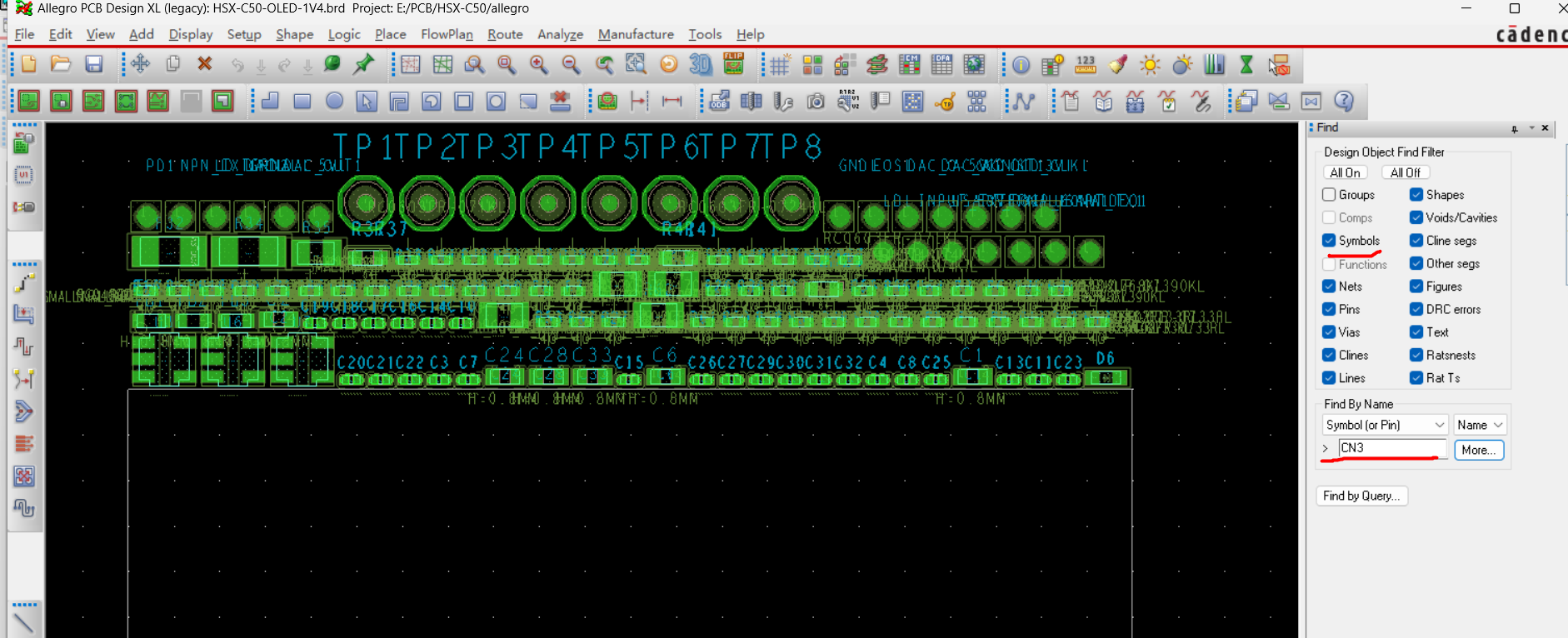

Ctrl+F搜索CN3,

Cadence生成网表时候,出现了PCB封装问题,显示说CN3有空格,后边封装删除,再重新输入修改了之后。再生成网表,依然能够导入PCB封装。但是再Allegro PCB中导入进去之后,搜索果然CN3的封装没有识别到,所以就没有CN3的封装。

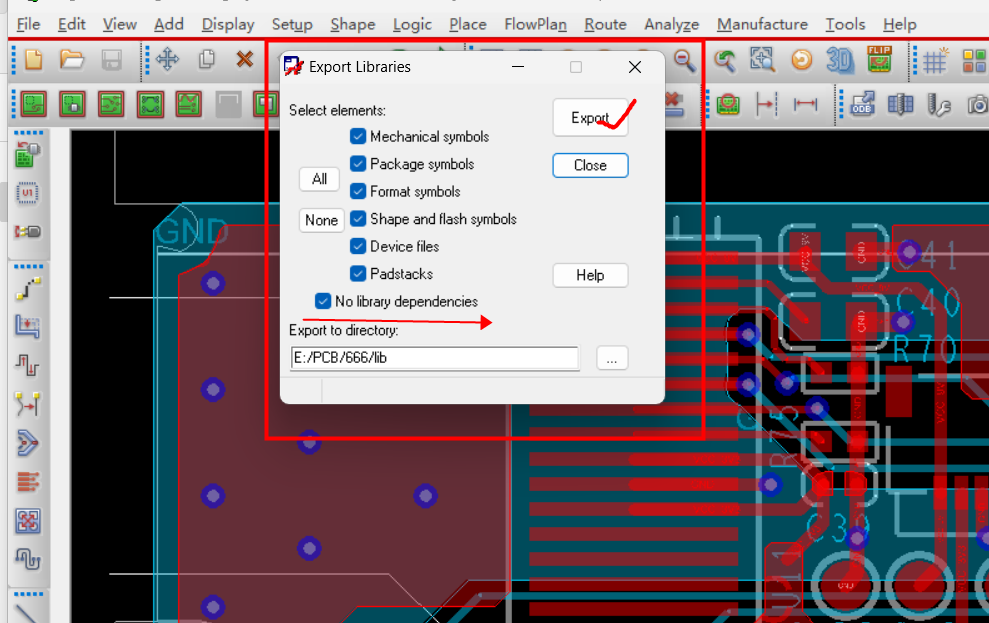

最后,解决的办法是 因为一个原理图,有两个PCB图,导致只导出了一个PCB的封装,另外一个没有导出来,所以重新导出封装后,就可以复用CN3的封装了。

注意的是:

PCB导出封装库时候,记得这个勾选上,否则特殊情况下,可能出现封装不能复用的情况

548

548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?