PL点亮LED灯

LED硬件

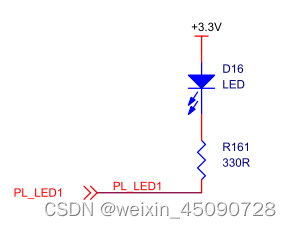

开发板在PL端给了一个LED灯,电压给低的时候才导通,才亮。然后需要看原理图确定具体是用的PL的哪个管脚以便进行控制。

Vivado 工程创建

- 打开

- 创建新工程

- 选择工程名和工程目录(不能有中文路径,也不能太长)

- 选择RTL工程和verilog

- 选器件

编写Verilog HDL文件

右边的add sources进行文件的添加和创建。

IBUFDS原语用于将差分输入信号转化成标准单端信号,且可加入可选延迟。在IBUFDS原语中,输入信号为I、IB,一个为主,一个为从,二者相位相反。

IBUFDS的逻辑真值表所列,其中“-*”表示输出维持上一次的输出值,保持不变。

`timescale 1ns / 1ps

module led(

//Differential system clock

input sys_clk_p,

input sys_clk_n,

input rst_n,

output reg led

);

reg[31:0] timer_cnt;

wire sys_clk ;

// 由于输入时钟为 2 00MHz 的差分时钟,因此需要添加 IBUFDS 原语连接差分信号

IBUFDS IBUFDS_inst (

.O(sys_clk), // Buffer output

.I(sys_clk_p), // Diff_p buffer input (connect directly to top-level port)

.IB(sys_clk_n) // Diff_n buffer input (connect directly to top-level port)

);

always@(posedge sys_clk)

begin

if (!rst_n)

begin

led <= 1'b0 ;

timer_cnt <= 32'd0 ;

end

else if(timer_cnt >= 32'd199_999_999) //1 second counter, 200M-1=199999999

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule

用了一个计数器来控制输出值的高低,到达给定值就进行一次取反。

添加管脚约束

xdc 文件里主要是完成管脚的约束时钟的约束 ,以及组的约束。这里我们需要对led.v 程序中的输入输出端口分配到 FPGA 的真实管脚上。

- Open Elaborated Design

- OK

- Window --> I/O Ports

- 设置管脚的约束

- 保存会自动生成xdc文件

添加时序约束

点击“ Run Synthesis ”综合后,Constraint s Wizard。

生成BIT文件

Generate Bitstream

Vivado仿真

需要编写激励文件,创建仿真文件。

`timescale 1ns / 1ps

//

// Module Name: vtf_led_test

//

module vtf_led_test;

// Inputs

reg sys_clk_p;

reg rst_n ;

wire sys_clk_n;

// Outputs

wire led;

// Instantiate the Unit Under Test (UUT)

led uut (

.sys_clk_p(sys_clk_p),

.sys_clk_n(sys_clk_n),

.rst_n(rst_n),

.led(led)

);

initial

begin

// Initialize Inputs

sys_clk_p = 0;

rst_n = 0;

// Wait for global reset to finish

#1000;

rst_n = 1;

end

//Create clock

always #2.5 sys_clk_p = ~ sys_clk_p;

assign sys_clk_n = ~sys_clk_p ;

endmodule

然后可以选择左边的仿真设置仿真条件后进行仿真。

上板

在线加载即可

在线调试

ILA IP核

Vivado 有内嵌的逻辑分析仪,叫做 ILA ,可以用于在线观察内部信号的变化,对于调试有很大帮助。

设置IP核并实例化。

ila ila_inst(

.clk(sys_clk),

.probe0(timer_cnt),

.probe1(led)

);

MARK DEBUG

在代码中添加综合属性,实现在线调试。

module led(

//Differential system clock

input sys_clk_p,

input sys_clk_n,

input rst_n,

(*MARK_DEBUG="true"*) output reg led

);

(*MARK_DEBUG="true"*) reg[31:0] timer_cnt;

保存,综合,Set Up Debug。

在xdc 文件中即可看到添加的 ila 核约束。

4588

4588

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?