A.18 时序逻辑实例四:状态机(两段式描述-传统公式)

什么叫做两段式描述的状态机?

两段,可以理解为两个always程序块。

(1)第一个always程序块

采用同步时序逻辑电路描述状态转移。

(2)第二个always程序块

采用组合逻辑电路判断状态转移条件并描述状态转移规律,同时组合逻辑输出结果。

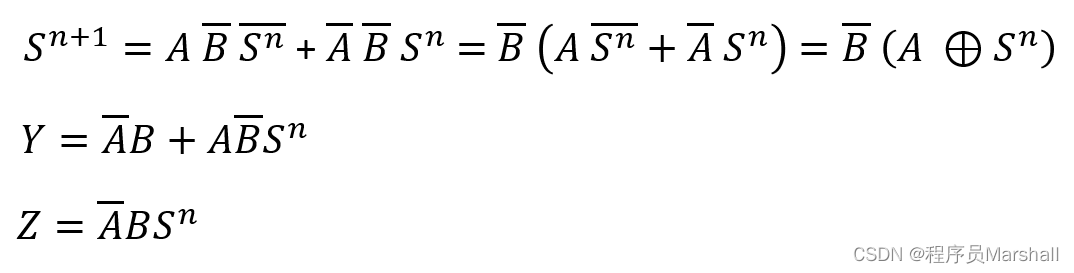

卡诺图化简公式

第二个always程序块中的组合逻辑电路会用到上一章节内容中化简后的公式,所以这里暂且列在这里。

设计模块

//文件路径:a.18/src/sell.v

module sell(clk,rst_n,a,b,y,z);

parameter S0 = 1'b0;

parameter S1 = 1'b1;

input clk;

input rst_n;

input a,b;

output reg y,z;

reg current_state;

reg next_state;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

current_state <= S0;

else

current_state <= next_state;

本文介绍了使用Verilog进行时序逻辑设计的实例——两段式状态机,通过两个always程序块分别描述同步时序逻辑电路和组合逻辑电路。内容包括卡诺图化简公式、设计模块的编写原则以及测试模块中模拟不同场景的仿真结果,验证了状态机的正确性。

本文介绍了使用Verilog进行时序逻辑设计的实例——两段式状态机,通过两个always程序块分别描述同步时序逻辑电路和组合逻辑电路。内容包括卡诺图化简公式、设计模块的编写原则以及测试模块中模拟不同场景的仿真结果,验证了状态机的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

314

314

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?