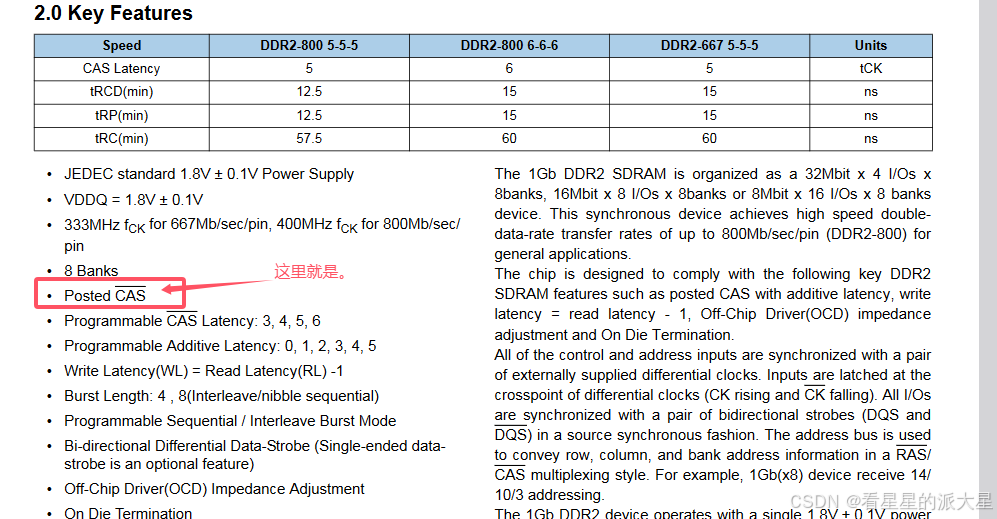

首先是 post CAS 的概念。

1、只看读命令,不看写命令。

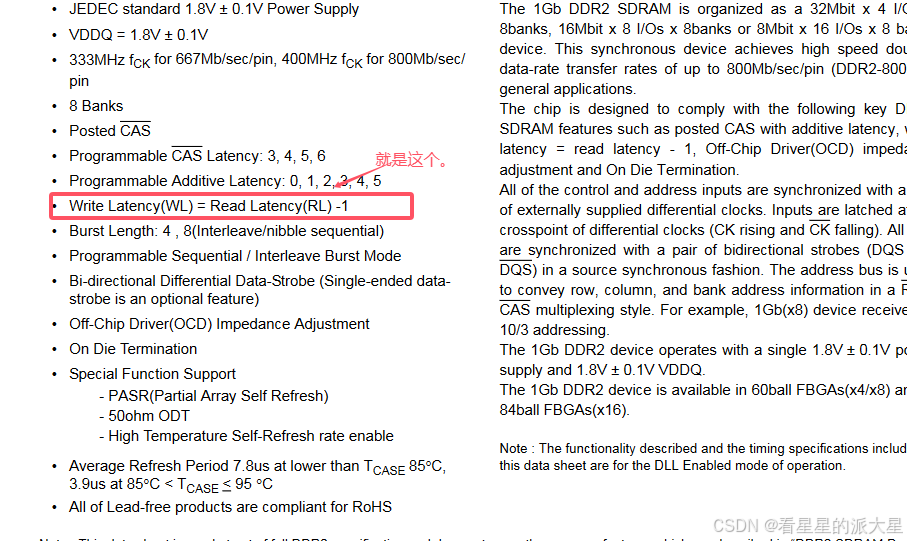

2、在内存的数据手册中也是有写的。

3、正常情况下, 首先发布的是行激活,也叫bank 激活 ,然后同时在地址线上就有了地址,这里地址线 没有画出来,然后 等待 tRCD 的时间,然后开始发送列激活,然后等待 tCAS , 图上是 CL=3,同时在地址线上开始输出列地址。图上的 read a bank 就是 发出列激活的意思。

4、 但是post ,就是 发送完行地址之后,紧接着 就发送列地址,也就是把列地址提前了,但是等的延时还是这些。这就是 Post CAS .

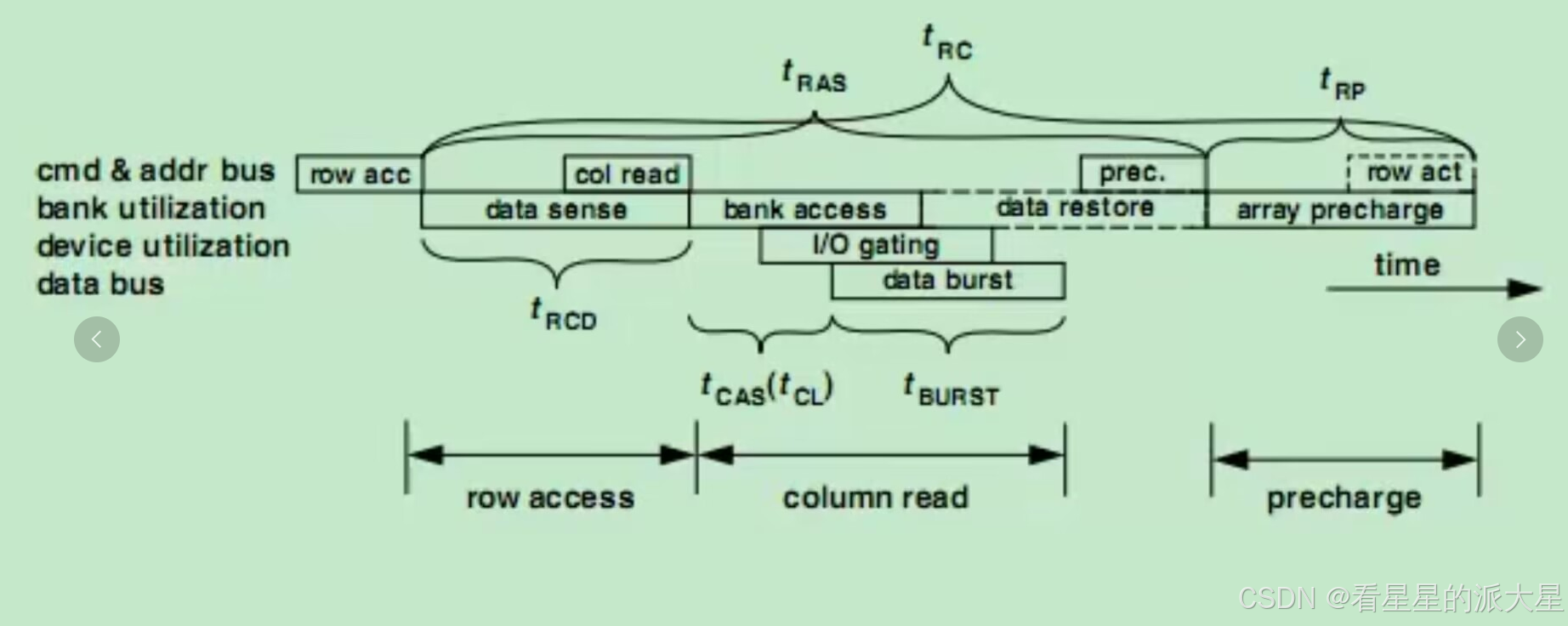

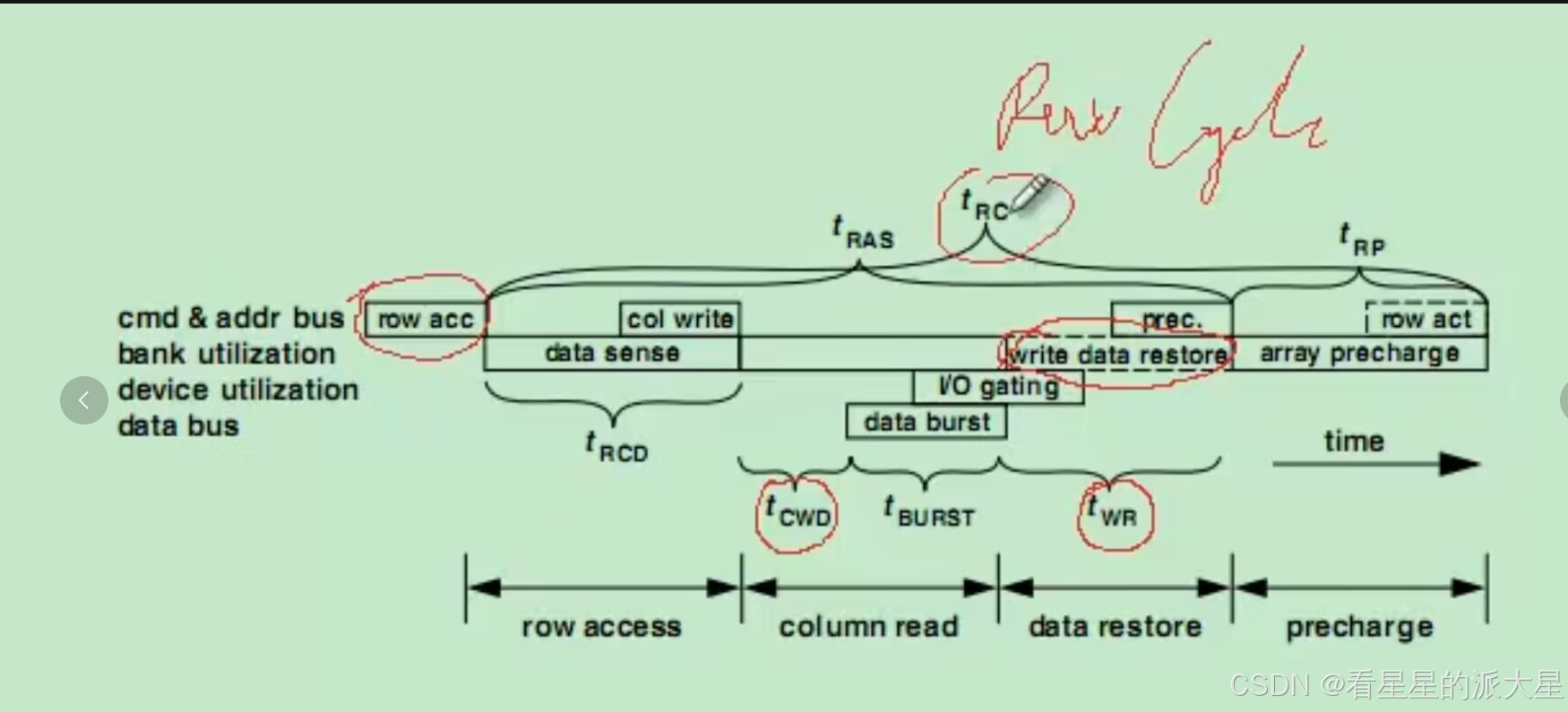

先来分析一下 读的理论过程。

1、row acc 就是行激活。

2、tRCD : row to colum command delay , 就是从行激活,到列激活的时间。

3、 tCAS : collom access stroke. 就是从列激活,到输出数据的时间。

4、 tBURSt ,就是 一下输出4个地址,还是 8个地址。

5、data restore , 就是,在输出完之后, 还要给小电容冲个电。

6、tRP , row precharge , 就是预充电, 将电平 置于 二分之一 VCC。、

7、 tRAS , row access stroke , = tRCD + tCAS + tBURST + data store

8、tRC , row cycle , 就是 tRCD + tCAS + tBURST + data store + tRP

9、 在 post 的模式中,虽然可以将列地址,以及precharge 提前,但是这些延时 该是怎么还是怎样。内存会把这些 命令 保存起来。

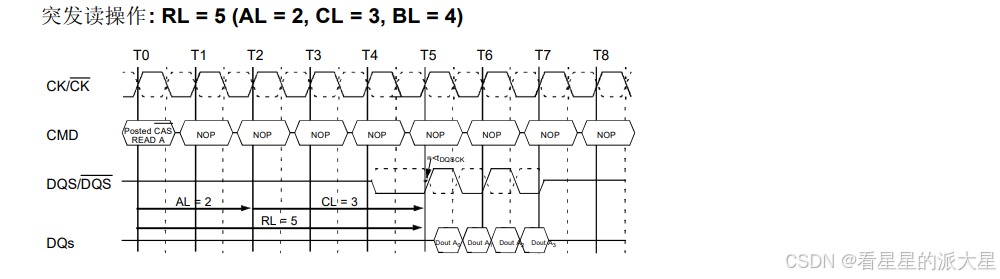

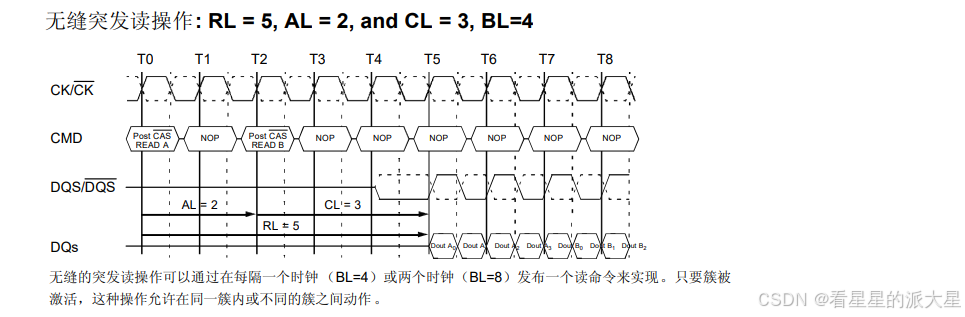

接下来看一下 真正的读时序。

1、RL = 5 (AL = 2, CL = 3, BL = 4) , 这里的 RL就是 tCAS , BL 就是burst . AL 就是附加延时。

2、可以看到 ,首先是 行激活, 然后 经过 AL ,CL的延时,开始输出数据了。

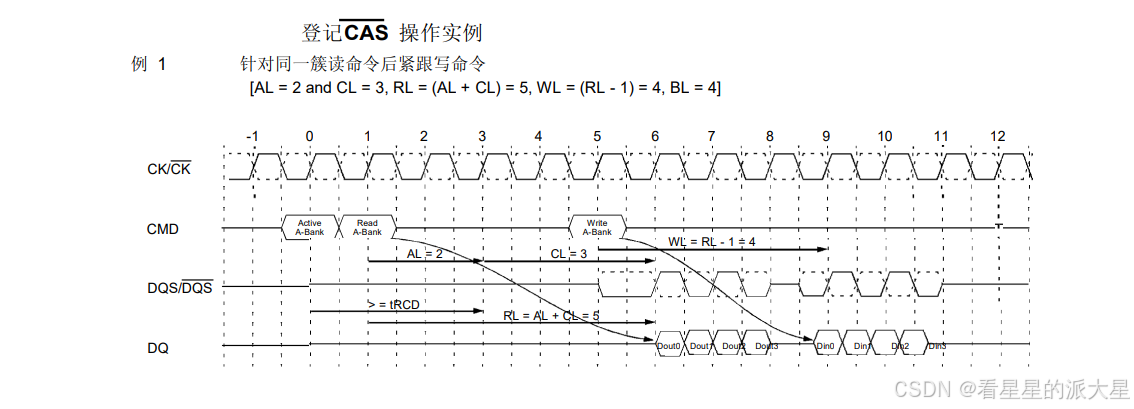

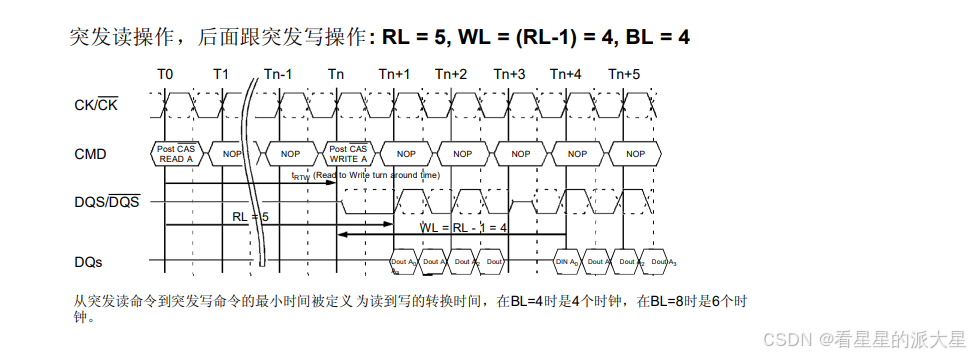

然后再来看一下 读紧跟写操作。

1、 可以看到,首先是 行激活, 然后是经过 RL的延时之后,开始输出数据了,然后 有一个 写操作,然后 经过 WL的延时之后 开始 写数据。

2、 这里 写的延时 是 读的延时 减一 ,这在数据手册中有说明。

然后来看一下 连续读的时序。

1、 可以看到第二个 读命令 就没有 延时了。

然后来看一下 写的时序。

然后来看一下写的理论时序。

1、首先是 行激活,

2、 然后是经过 tRCD , 在输出一个 列写命令

3、 tCWD ,就是 从DMC 发出写命令 到在数据线上发出数据的延迟。

4、tBURST ,就是, 数据总线上 开始有数据的 延迟。

5、 tWR , write recovery , 就是 从总线上有数据,到内存往小电容 写完数据的延迟。

6、 预充电是一样的。

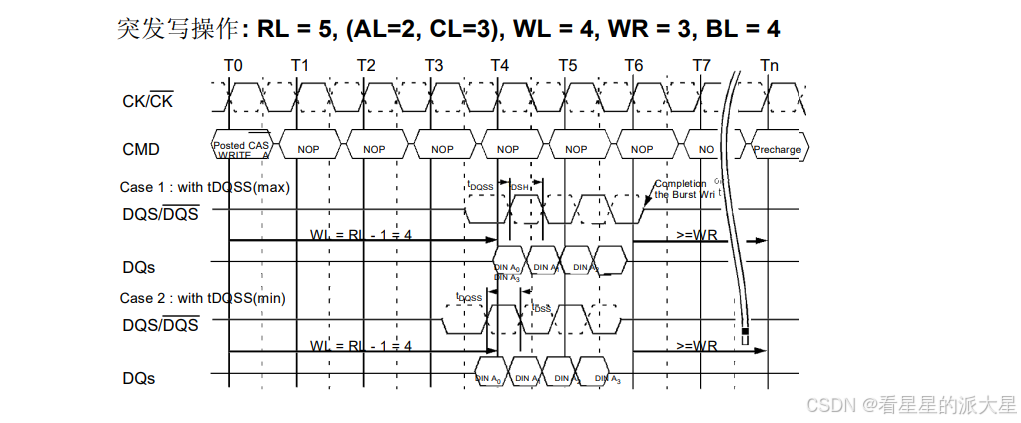

然后来一下 真正的 写的时序。

1、这里从 发布写命令开始的。

2、然后经过 WL(write latency)也就是4个时钟周期,开始在数据总线上有数据了。

3、然后经过 WR(write recovery)的延时, 数据保存到电容中了。

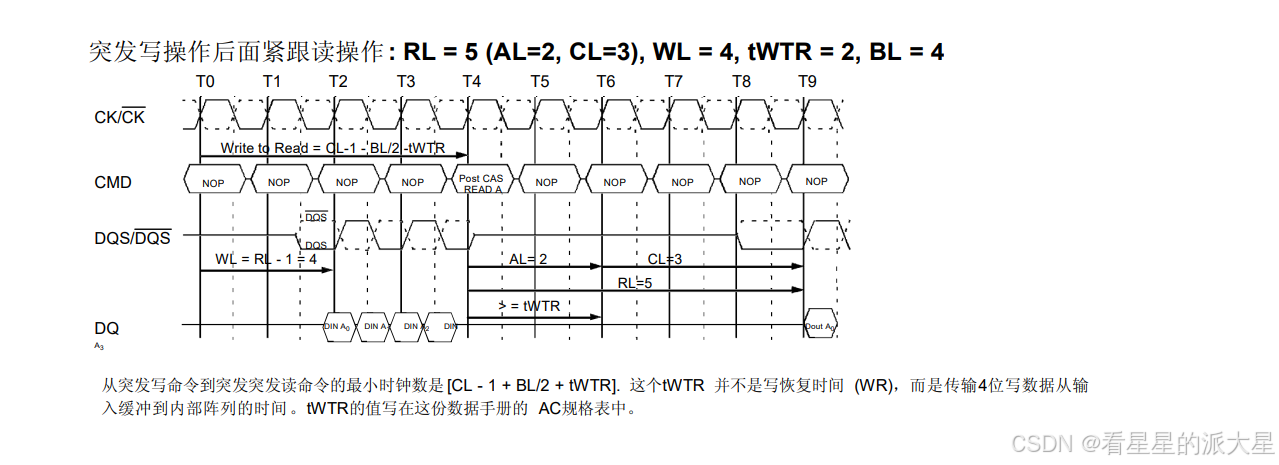

然后是 写紧跟读操作。

1、 这里主要就是 tWTR 的时间,就是 write to read , 可以看到,虽然 读命令 提前发布了,但是 在芯片内部,必须要过 WTR 的时间之后,芯片才可以 执行读命令。

疑问: 可以看到,怎么没有了 WR的时间了呢?

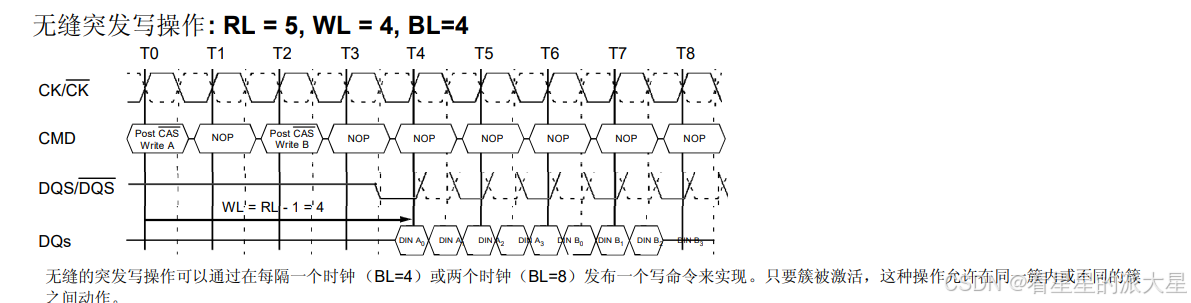

然后是连续的突发写的操作。

1、 根连续的读 是一样的。

2、 第二个 读 是没有 WL的延时的。

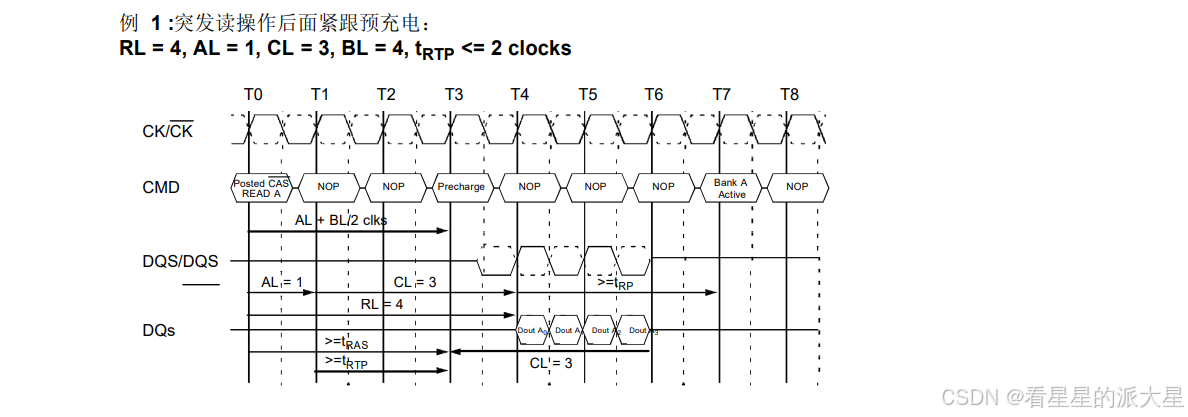

然后来看一下 读 后面 跟预充电的图:

1、 可以看到 从发布 precharge 命令开始 ,往前数, 要大于 tRTP .

2、 tRTP : read to precharge .

3、 从发布下一个 激活指令开始,往前数,到这个 precharge 最少要 经过 tRP 的时间。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?