参考资料:

Xilinx官方参考文档:PG021_axi_dma、UG585_zynq_7000_TRM等

AXI DMA开发 http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html

黑金教程 course_s2_ALINX ZYNQ开发平台SDK应用教程V2.02.pdf

米联客教程 S03_CH01_AXI_DMA_LOOP(视频) https://v.qq.com/x/page/e0349oqwa27.html

本文介绍在进行AXI_DMA_LOOP测试时遇到的问题和走的弯路,记录下。

-

前言

之前一直做FPGA开发,在网络方向的,主要是二层、三层交换方向,采用的硬件架构也是分离式的CPU+FPGA的架构。想想zynq也出了好久了,一直想研究的,无奈工作太忙加上自己太懒一直耽搁了,既然有时间,说搞就搞。想想之前项目的应用环境,FPGA与CPU间是通过以太网通信。ZYNQ里集成了ARM,于是便先搞清楚FPGA与ARM间的通信方式。

PS(ARM)与PL(FPGA逻辑)间采用比较多的通信方式就是通过AXI总线方式进行通信,具体AXI协议不做介绍,网上资料很多。

-

AXI4-Lite有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit),主要用于访问一些低速外设和外设的控制。

-

AXI4接口和AXI-Lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。也就是说具有数据读写的burst 功能。

-

AXI4-Stream是一种连续流接口,不需要地址线(类似FIFO),对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO没有地址线),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。AXI4-Stream本质都是针对数据流构建的数据通路。

AXI4-Lite和AXI4均采用内存映射控制方式,即ARM将用户自定义IP编入某一地址空间进行访问,读写时就像在读写自己的片内RAM,编程也方便,开发难度较低。代价就是资源占用过多,需要额外的读写地址线、读写数据线以及应答信号等。

AXI4-Stream是一种连续流接口,不需要地址线(类似FIFO),对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO没有地址线),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。AXI4-Stream本质都是针对数据流构建的数据通路。

因为以前做的二层、三层交换也是数据流驱动架构,并且原来做以太网的接口方式也是AXI4-Stream方式,对AXI4-Stream比较熟悉,因此先研究AXI4-Stream接口。

几个常用的AXI_stream接口的IP介绍:

- AXI-DMA:实现从PS内存到PL高速传输高速通道AXI-HP<---->AXI-Stream的转换

- AXI-FIFO-MM2S:实现从PS内存到PL通用传输通道AXI-GP<----->AXI-Stream的转换

- AXI-Datamover:实现从PS内存到PL高速传输高速通道AXI-HP<---->AXI-Stream的转换,只不过这次是完全由PL控制的,PS是完全被动的。

- AXI-VDMA:实现从PS内存到PL高速传输高速通道AXI-HP<---->AXI-Stream的转换,只不过是专门针对视频、图像等二维数据的。

做嵌入式驱动的经常会用到DMA,先从DMA入手吧。

简单介绍zynq的AXI_DMA模块,该模块用到了三种总线,AXI4_Lite用于对寄存器进行配置(这个地方之前没了解清楚,吃了亏,后面介绍弯路),AXI4 Memory Map用于与内存交互,在此模块又分立出了AXI4 Memory Map Read和AXI4 Memory Map Write两个接口,又分别叫做M_AXI_MM2S和M_AXI_S2MM。AXI4_Stream接口用于对用户逻辑进行通信,其中AXI4 Stream Master(MM2S)是PS to PL方向,AMI4 Stream Slave(S2MM)是PL to PS方向。

下面实例学习:开发环境 vivado 2017.4 SDK 2017.4

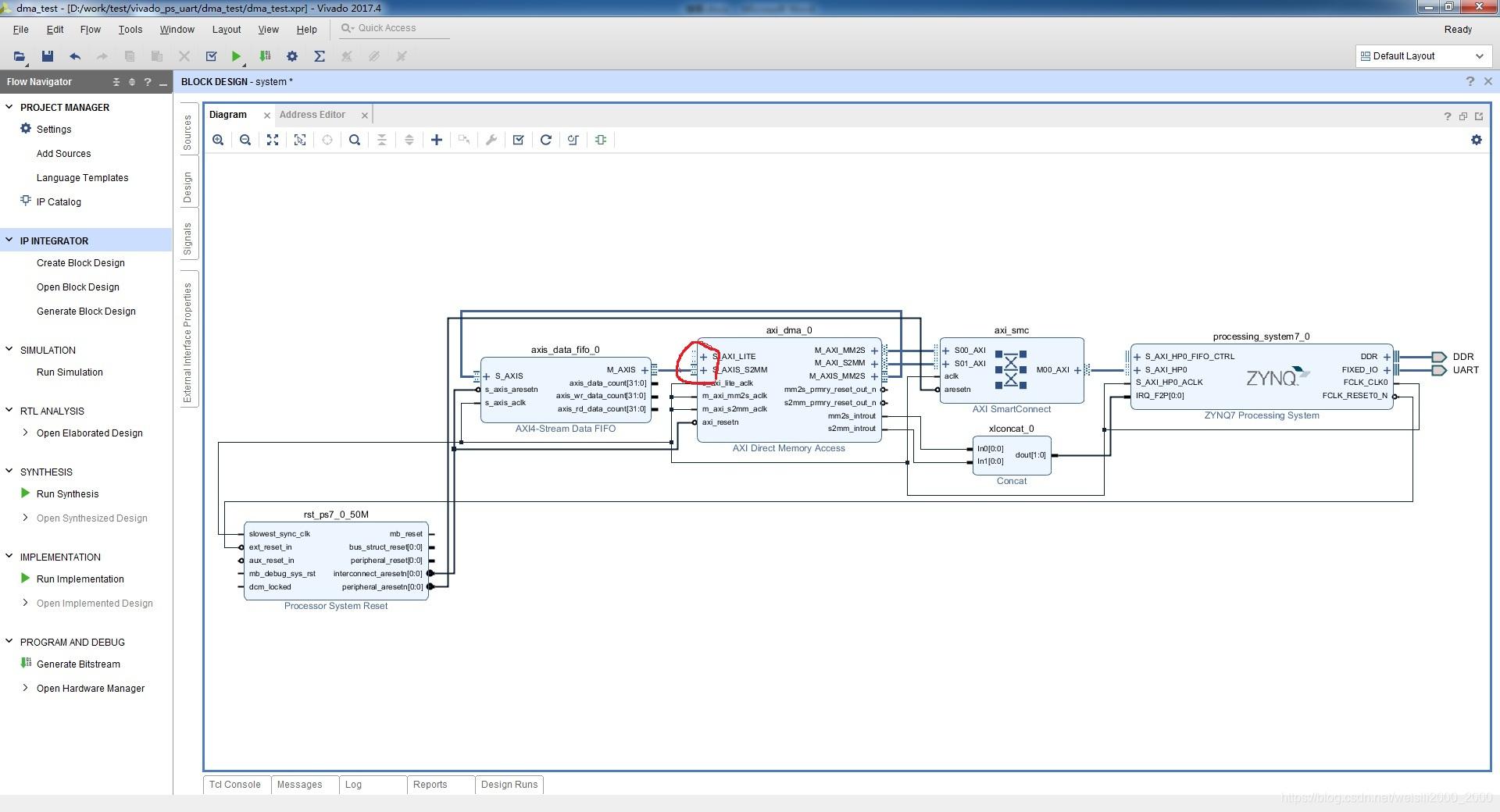

AXI_DMA_LOOP的硬件框图:

这里为了与以前的项目对应,FIFO的宽度定义为8bit(vivado 2017.4版本AXI DMA有个BUG后面介绍),采取中断触发方式。在vivado中建立系统block(方法网上自查)

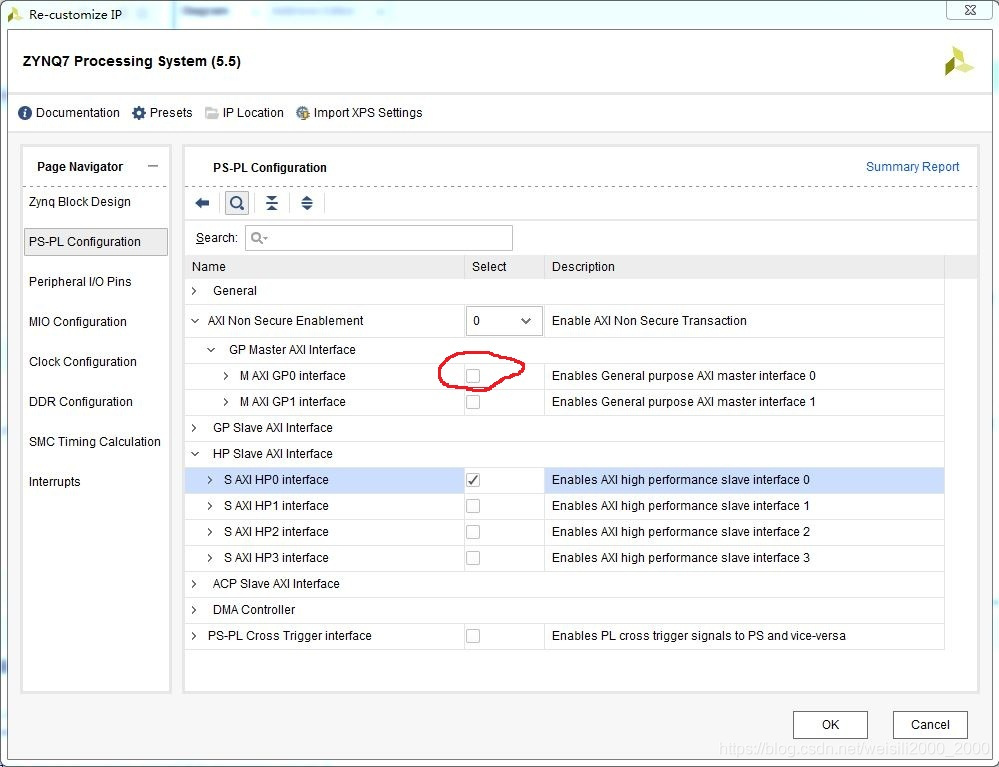

- 错误案例一

认为DMA只用AXI-HP接口,擅自去掉了zynq的AXI-GP接口,导致生成系统的AXI_DMA 的S_AXI_Lite接口没有连接,最后生成bit文件后导入SDK后peripheral里没有axidma的驱动示例,只有dmaps的驱动示例;以及生成案例的BSP没有axidma的相关.h和.c。

Zynq定制出现错误

结果生成硬件系统如下:

导入SDK后发现(只有dmaps驱动示例,没有axidm

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?