Xilinx官方参考文档:ug994-vivado-ip-subsystems.pdf

黑金教程:

cource_s1_ALINX_ZYNQ(AX7010_AX7020)开发平台基础教程V1.06(第十一章)

course_s2_ALINX ZYNQ开发平台SDK应用教程V2.02.pdf(第十章)

前面介绍了PS与PL通过DMA通信的基本测试,但是之前用的都是xilinx的官方的IP核,接口都是做好的,我们直接例化就好。而在实际应用中,我们更加关心用户逻辑怎么与PS间进行数据通信。下面就介绍在BD中添加用户逻辑的方式,以及在其过程中所遇到的问题。

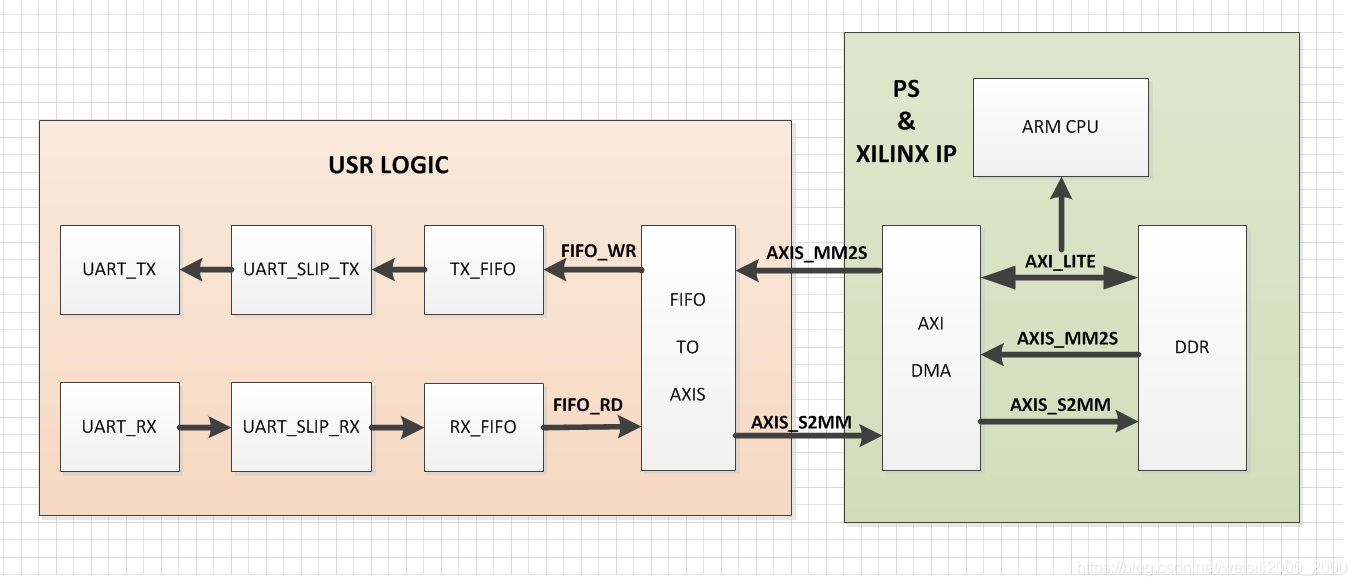

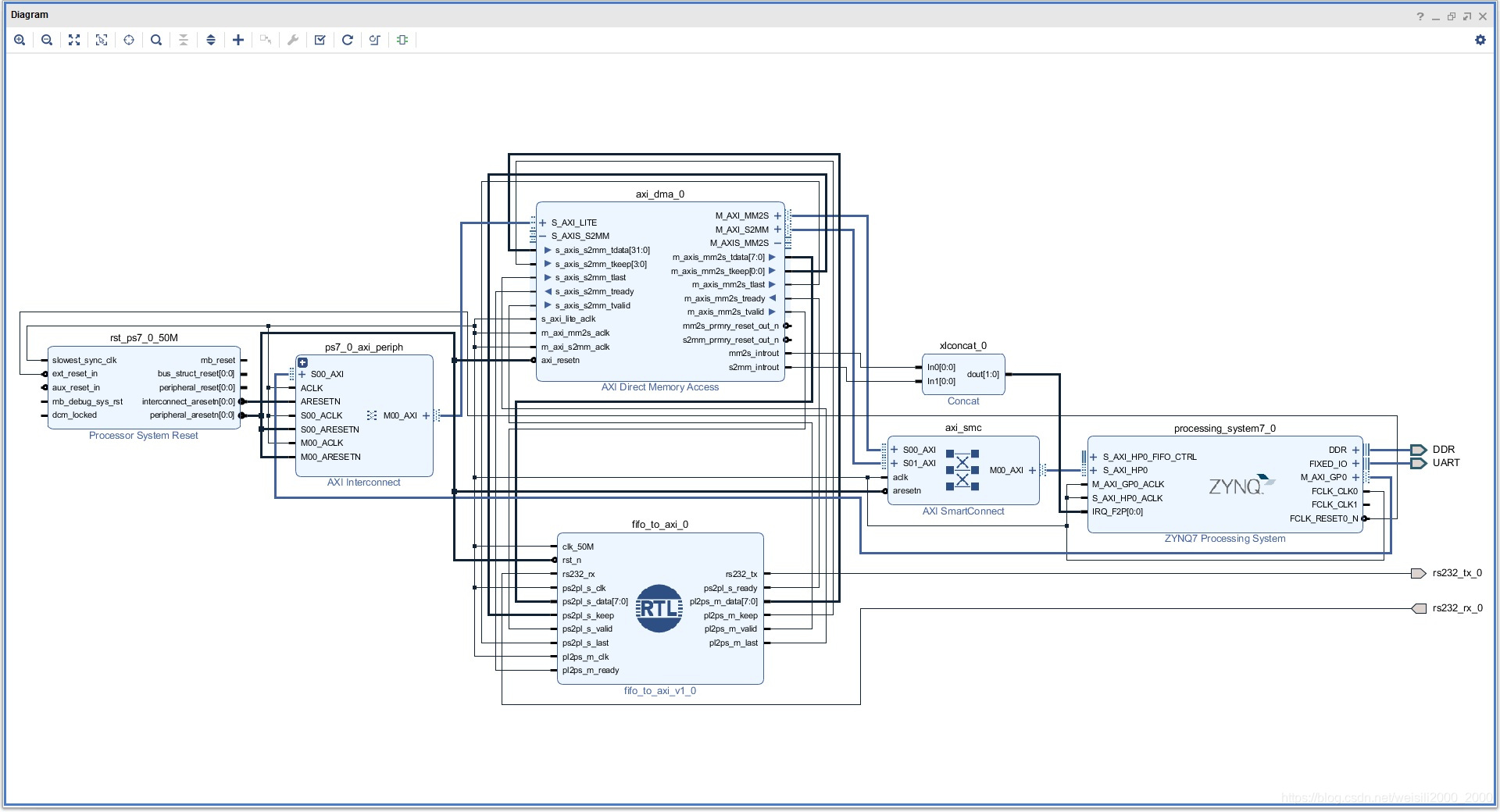

这里我们用户逻辑以UART接口为代表设计。PL端实现UART功能,在SDK里发送数据通过DMA给PL端的UART发送出去。在外部将UART的收发回环,将发送出去的数据再收回来,通过DMA在给PS。此外我们在PL的uart上封装层slip协议,用来实现在uart上进行帧操作。测试硬件框图如下:

就是在之前的测试环境中将AXIS_DATA_FIFO换成了我们用户逻辑UART部分,其中FIFO_to_AXIS是用来实现FIFO接口与AXIS接口的转换模块。

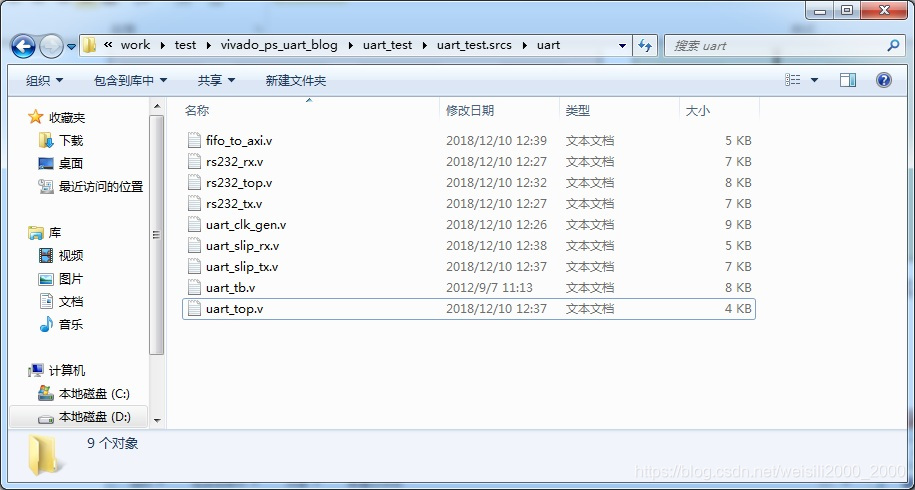

建立相应的vivado工程,并添加用户逻辑代码(模块不一一分析了):

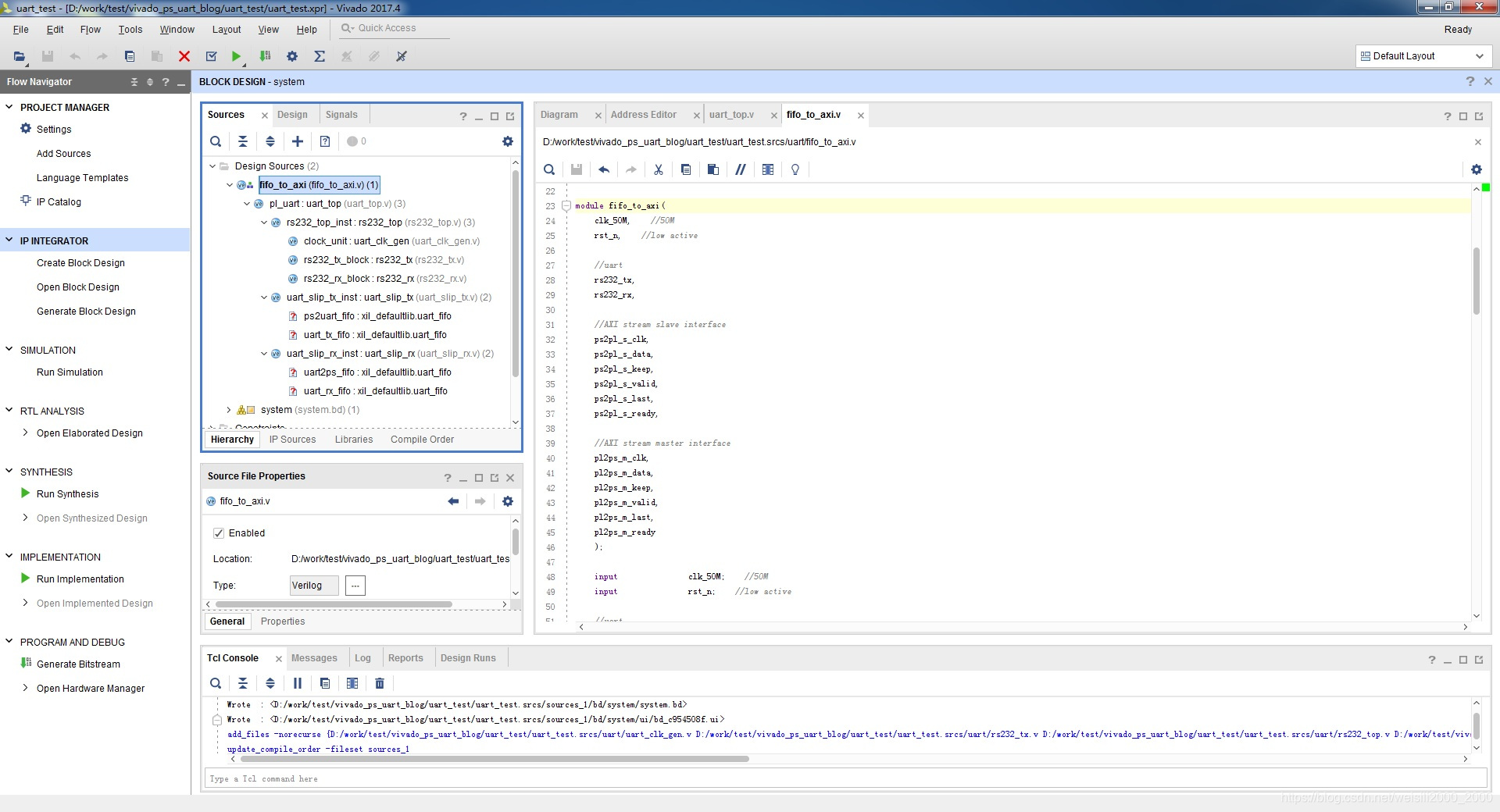

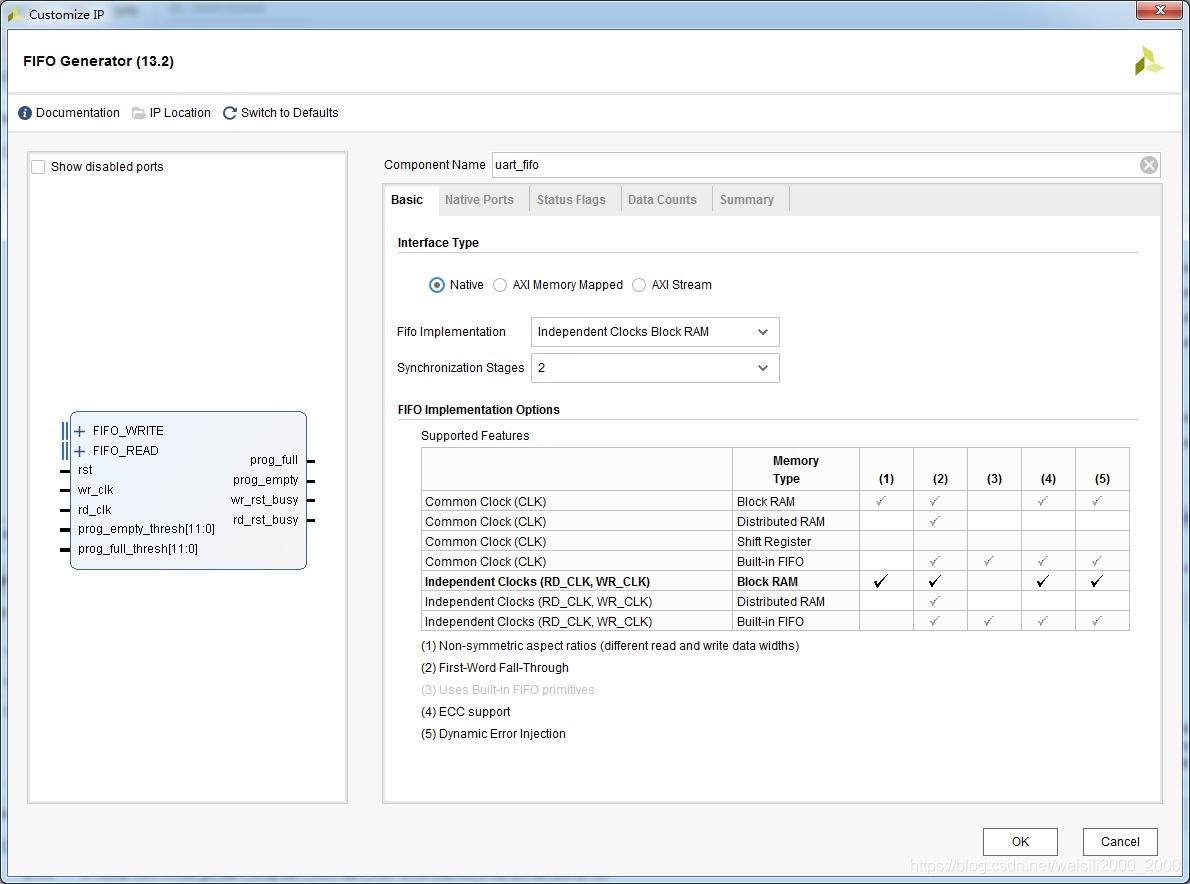

此时我们发现在用户逻辑部分还缺少FIFO IP核,我们用IP catalog增加相应的IP核,具体IP核的参数根据自己的需要进行定制。

在BD当中可以通过add IP和add module的方式来增加用户逻辑,两者稍微有点区别。

Add IP需要将用户逻辑提前封装好成IP核,然后通过IP Catalog来添加;而Add module可直接Diagram里添加。不过我在用Add module时遇到一些问题还没解决,可能BD并不认可我们写的fifo_to_axis的AXIS接口(其实在Add ip方式下我们并没有更改fifo_to_axis的逻辑,待定位问题)。

Add module方式:

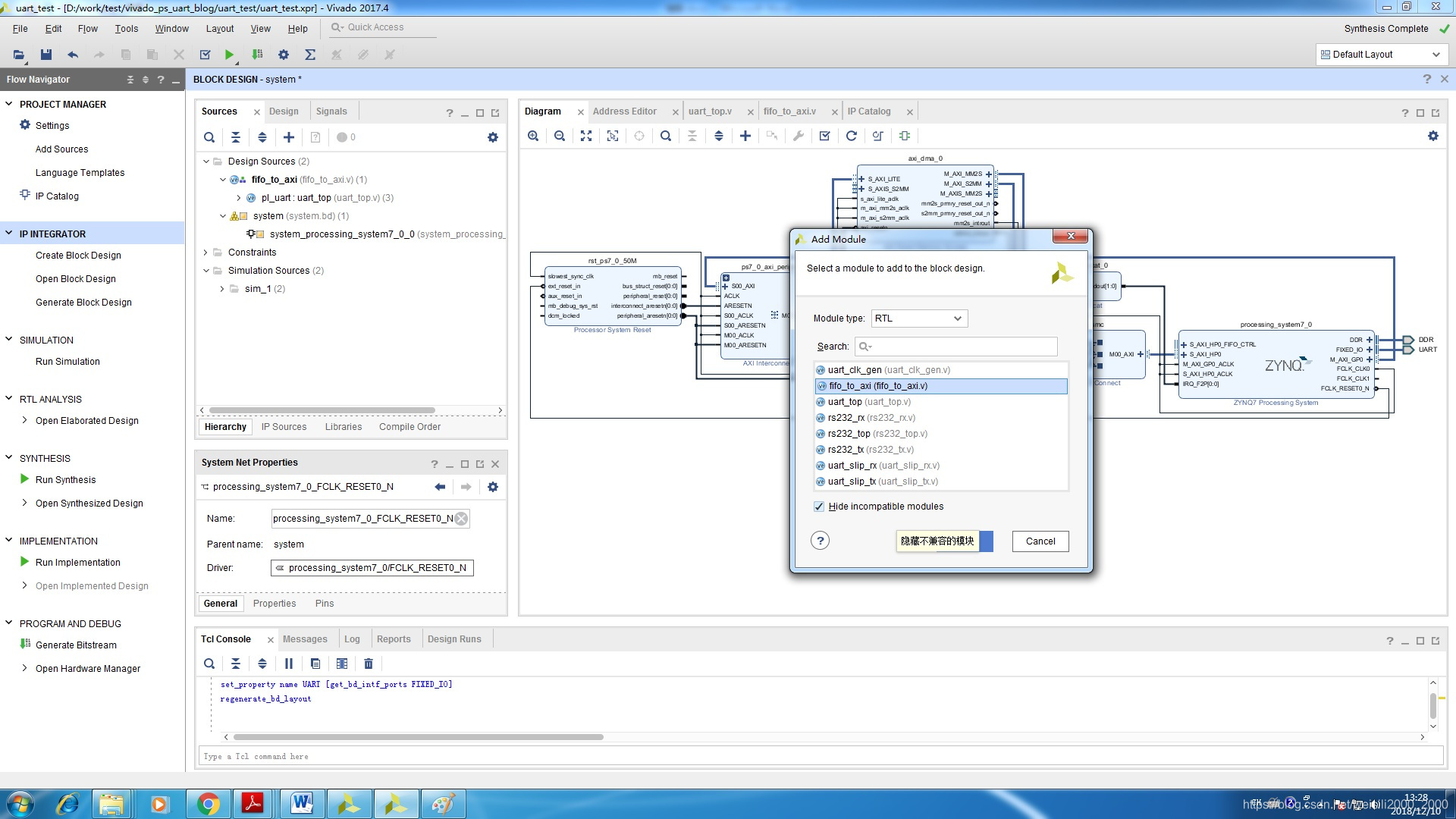

在Diagram里右键,选add module,在弹出的对话框选择你添加模块的顶层文件:

添加后模块上会显示RTL的标志,然后手动连线:

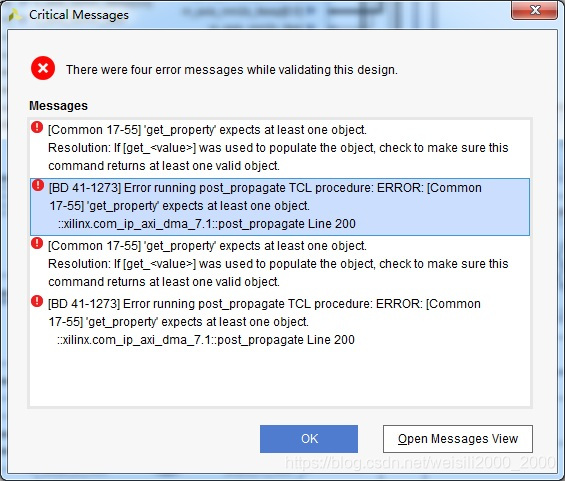

连线完成后,进行validate时报如下错误:

然后尝试定位问题,不过目前还没定位到地方,带我稍微再研究研究看看,我们先采用Add IP的方式。

Add IP:

首先我们需要将用户逻辑封装成AXIS4接口IP,步骤可参考相关教程,不细说,只介绍和教程有区别的地方。

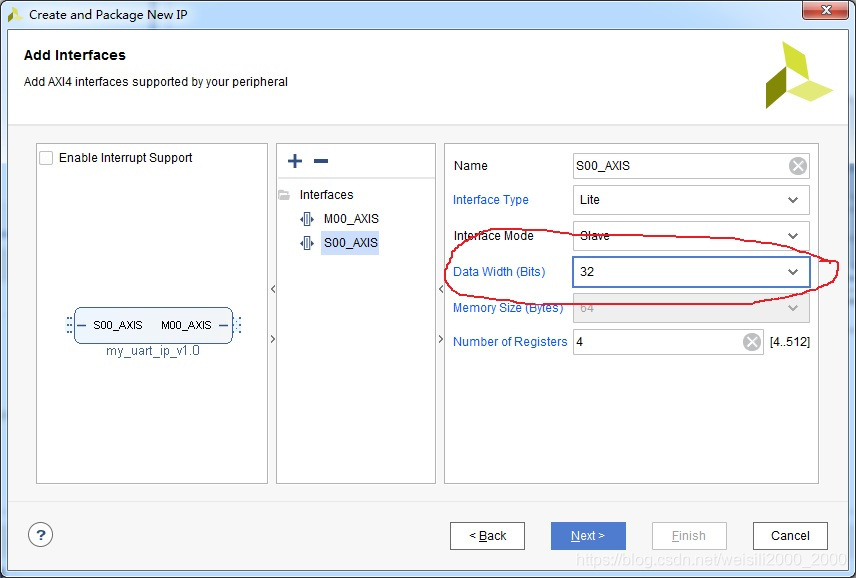

新建一个New IP,取名my_uart_ip。这里我们选2个AXIS接口,一主一从,然后位宽是32位(其实我们需要8位,但这里改不了,我们先不用管)

然后我们Edit in IP Packager,添加所需的用户逻辑代码:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

689

689