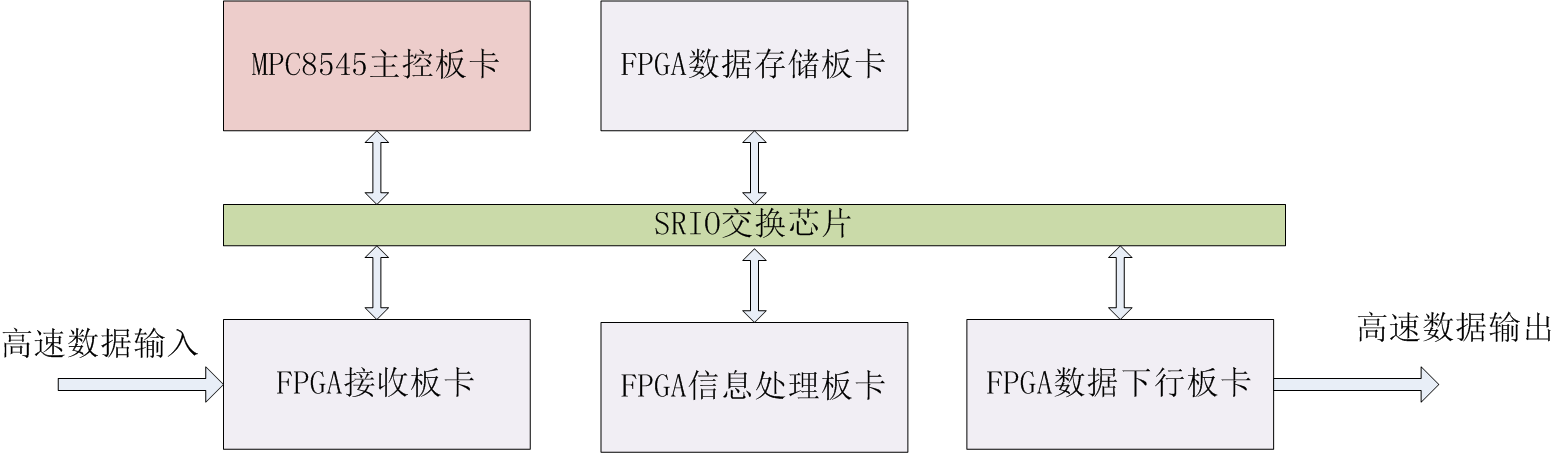

Rapid IO协议由于无主机,且各设备之间可以并行交换信息,所以广泛应用于对交换速率要求高,且交互复杂的应用中。

Xilinx现在有支持Serial RapidIO Gen2的核,可以应用在此场景中,但Xilinx 的 Rapid IO 核对外接口仅有 AXI 流接口 ,且对各类数据流的处理需要外部单独设计,不能方便的对消息、门铃、数据进行读写传输。本文介绍了将RapidIO核出来的接口转换到AXI总线上AXI-SRIO核的设计,以及Xilinx RapidIO核的典型配置。

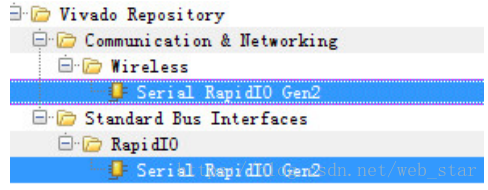

1. Xilinx IP核配置

Rapid IO 物理层在 Vivado 的 IP 列表中可以找到。

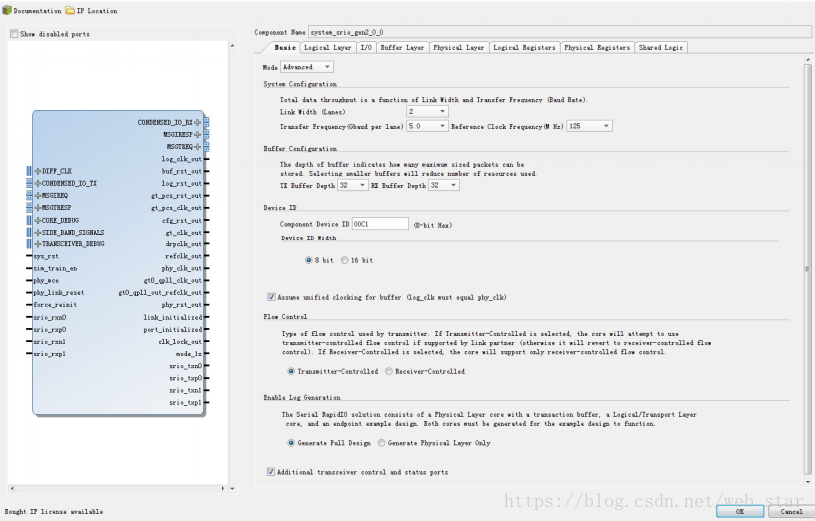

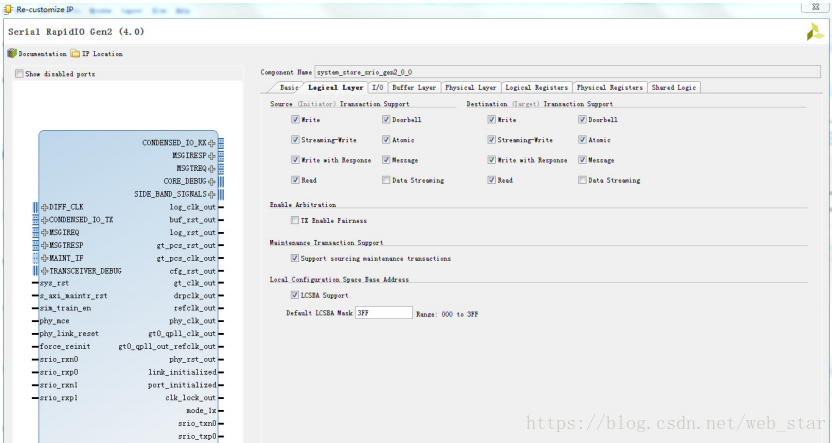

第一个配置界面中选择基本配置或者高级配置, 我们的设计均按照高级配置进行设置; 在系统配置选项, 选择 link width 位宽、 Gbaud速率、 ref_clk 频率; 在 Device ID 框中配置设备 ID; 因为核需要知道设备 ID, 选择附加控制和状态接口 , 其它设置默认。

逻辑层设置页面, 选择支持维护, 其它按照默认设置即可。

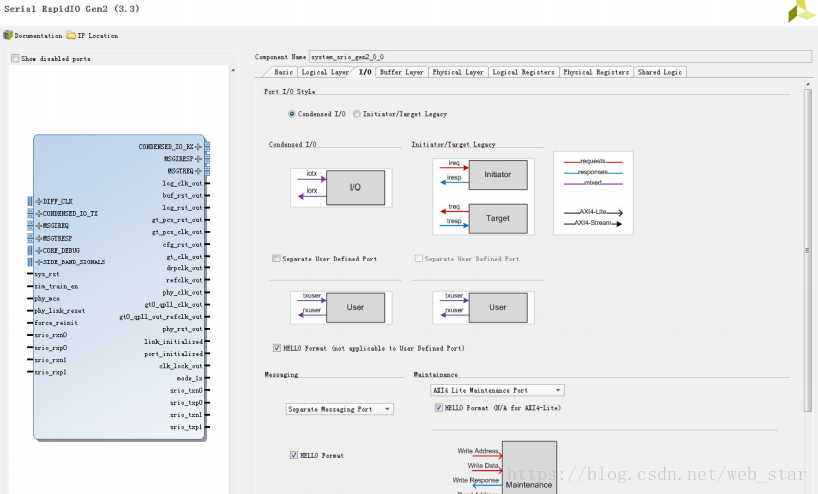

IO 设置页面, IO 端口设置为 Condensed I/O, Messaging 端口设置为 Separate Messaging port, 均选择 HELLO format。

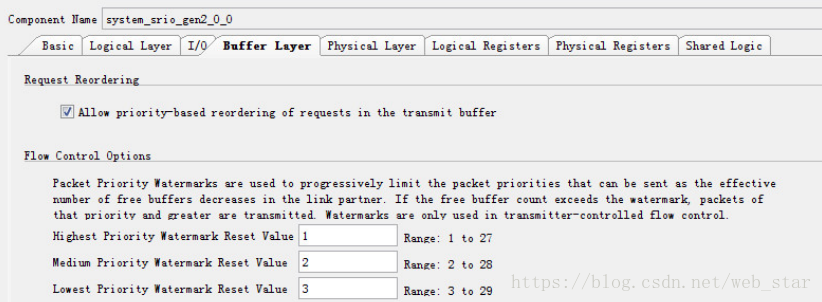

缓冲层页面按照默认设置即可。

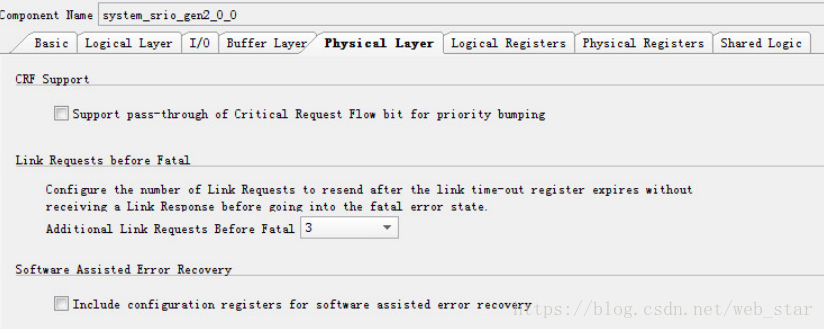

物理层页面按照默认设置即可。

逻辑寄存器 页面 可以自定义 设置 Assembly CAR, Processing Element Feature CAR 选择 Memory 类型。

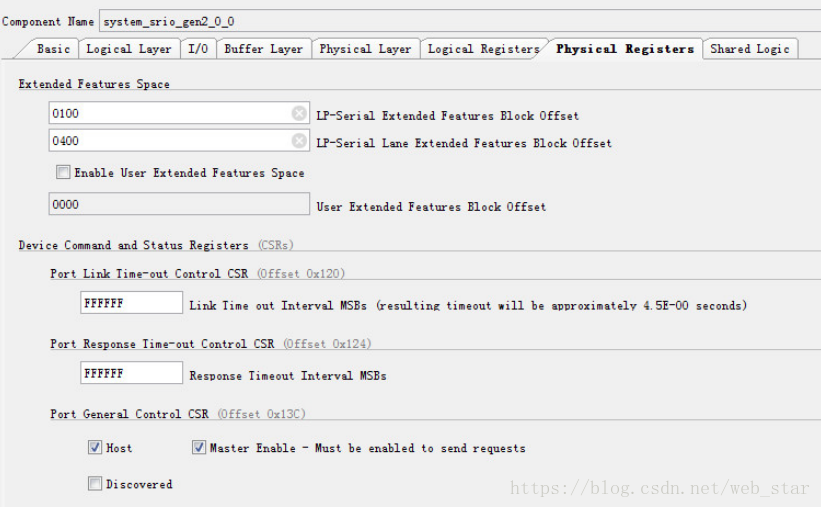

物理寄存器页面按照默认设置即可。

逻辑共享页面设置为在核内包含共享逻辑。

2. AXI转SRIO核设计

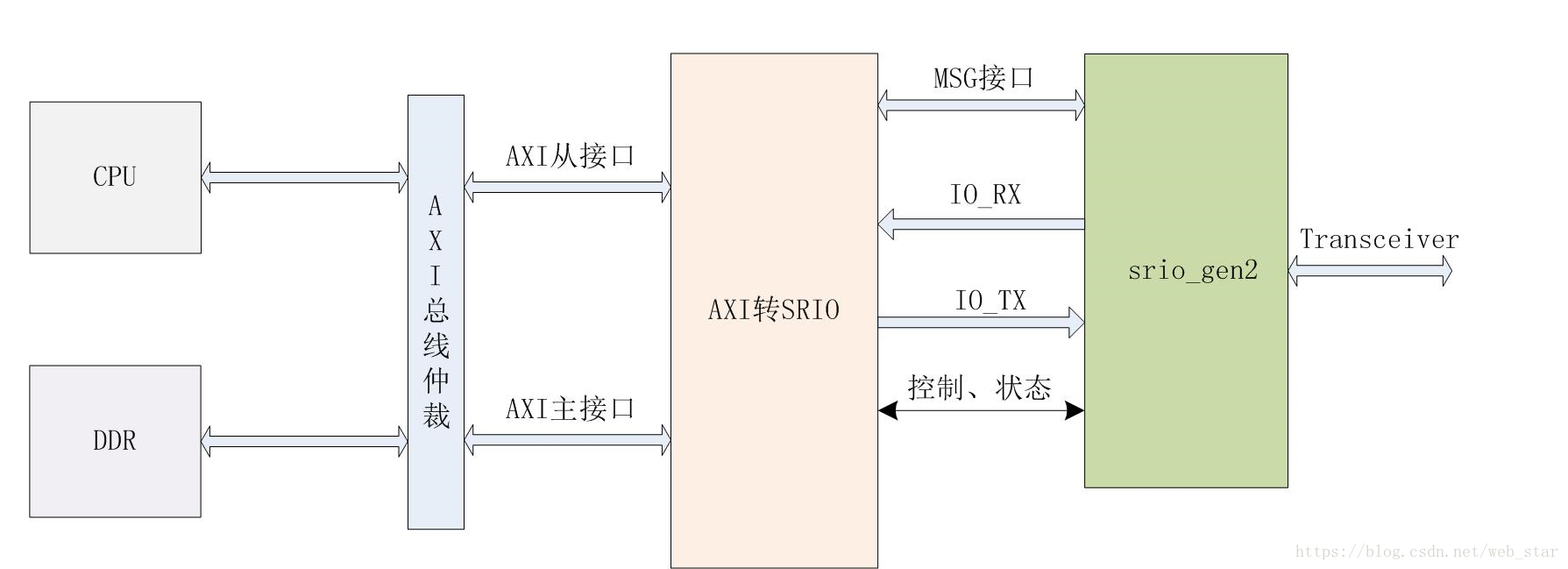

本模块实现Xilinx Rapid IO核和AXI总线之间的桥接,实现对Xilinx核的数据流信息进行处理,并映射到CPU的寄存器,用于以Rapid IO作为交换的高速数据传输应用。

CPU通过AXI从接口接收和发送消息、门铃,大块数据传输,通过AXI主接口写入和读出DDR,然后通过IO_RX、IO_TX接口发往srio_gen2核。

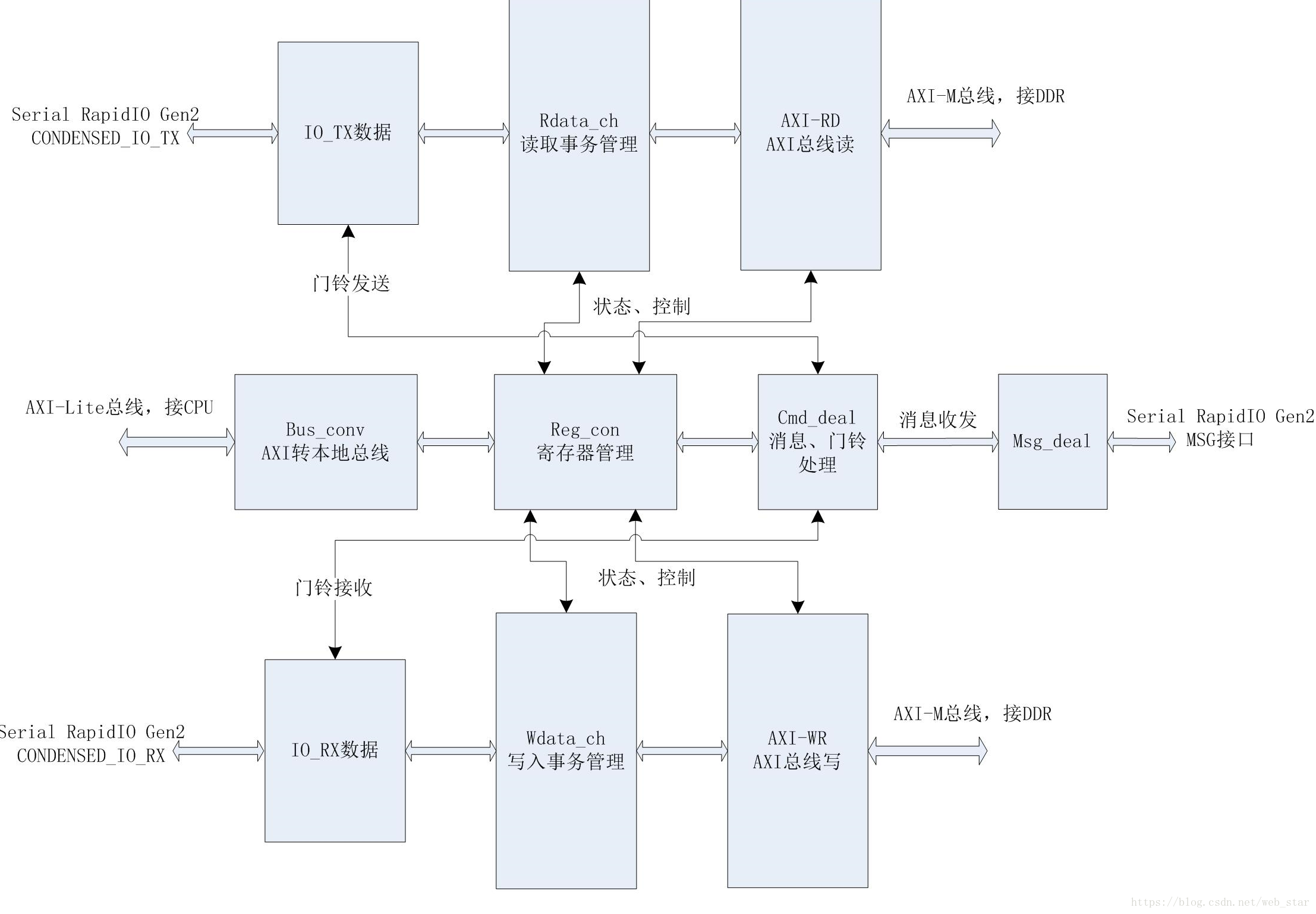

AXI转SRIO核内部构造如图所示。

IO_RX接口接收的大块数据,通过Wdata_ch写入事务管理器,再经过AXI-M总线,写入DDR缓存;需要发送出去的大块数据,通过AXI-M总线,从DDR缓存读出,经过Rdata_ch读事务管理器,发往IO_TX接口。

IO_RX和IO_TX的门铃,以及MSG的消息,传输到门铃、消息事务处理模块,然后送往CPU。

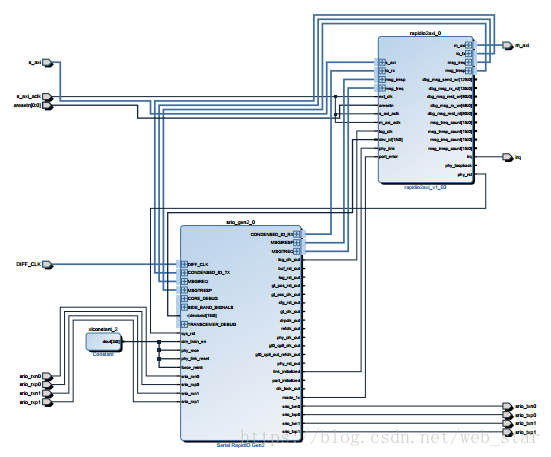

在Vivado工程设计中的连接图(清晰PDF版本https://download.youkuaiyun.com/download/web_star/10310707)。

通过AXI转SRIO模块,大大简化了设计,且可以通过CPU发送消息、门铃,且可以发起和接收高速大量DMA数据。

3. 其它

我公司设计的AXI转SRIO核接口模块,已经成功应用于多个项目,有源代码和网表多种形式销售,有需要购买的,请发邮件到wby010@qq.com联系。

本文介绍了一种Xilinx RapidIO核与AXI总线间的桥接设计方案,该方案支持高速数据传输应用,包括消息、门铃及大块数据的处理。通过AXI转SRIO核,可以显著简化设计流程,并利用CPU进行高效的数据传输。

本文介绍了一种Xilinx RapidIO核与AXI总线间的桥接设计方案,该方案支持高速数据传输应用,包括消息、门铃及大块数据的处理。通过AXI转SRIO核,可以显著简化设计流程,并利用CPU进行高效的数据传输。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?