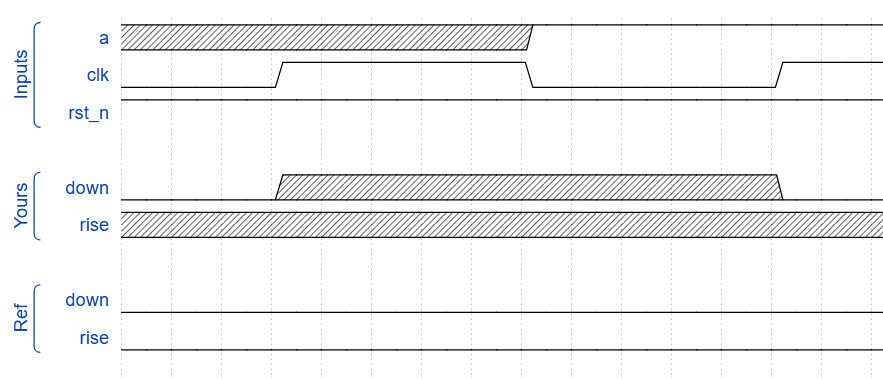

VL24 边沿检测

预备知识:

1.非时钟信号的边沿检测方法:

reg data_dly;

always @(posedge clk) begin

data_pre <= data; //当前的data存储起来

end

wire data_rising_edge = data & ~data_pre; //当前的1、上一拍的0

wire data_falling_edge = ~data & data_pre;

2.对时钟信号本身做边沿检测

直接使用 posedge clk 或 negedge clk 。

题目要求

思路一:

`timescale 1ns/1ns

module edge_detect(

input clk,

input rst_n,

input a,

output reg rise,

output reg down

);

reg a_pre;

always @(posedge clk ) begin

a_pre <= a;

end

always @(posedge clk , negedge rst_n)

begin

if(!rst_n) begin

rise <= 0;

down <= 0;

end

else

begin

if(a & ~a_pre) begin

rise <= 1;

down <= 0; end

else if(a_pre & ~a)

begin

rise <= 0;

down <= 1; end

else

begin

rise <= 0;

down <= 0; end

end

end

endmodule

思路二:

`timescale 1ns/1ns

module edge_detect(

input clk,

input rst_n,

input a,

output reg rise,

output reg down

);

reg a_pre;

always @(posedge clk , negedge rst_n)

begin

if(!rst_n) begin

rise <= 0;

down <= 0;

a_pre <= 0;

end

else

begin

a_pre <= a;

rise <= (a & ~a_pre) ? 1:0 ;

down <= (a_pre & ~a )? 1:0 ;

end

end

endmodule

思路二报错:

大佬可否给个提示?为啥会错呢?感觉思路一和思路二没区别啊

298

298

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?