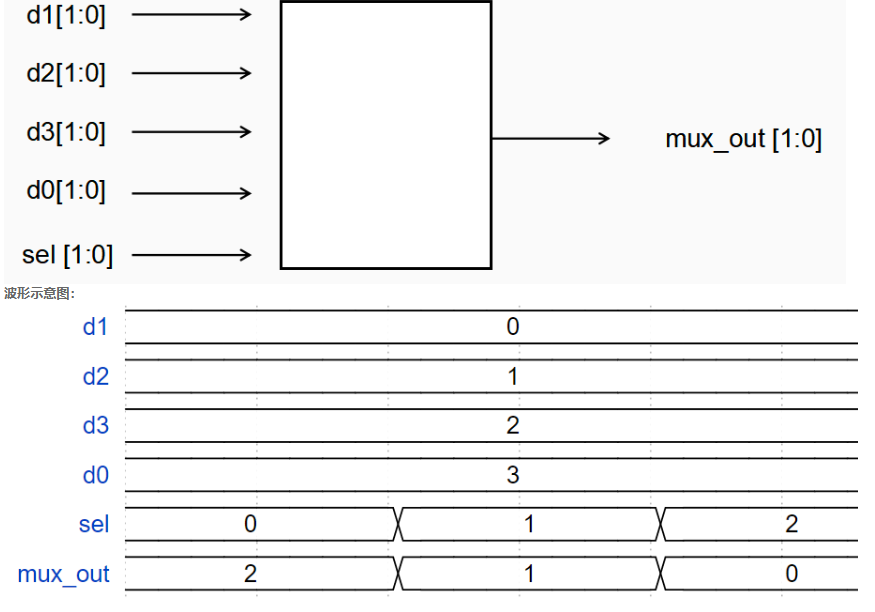

VL1 四选一多路器

思路一:组合逻辑

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

//*************code***********//

assign mux_out = (sel == 2'b00) ? d3 :(sel == 2'b01) ? d2 : (sel == 2'b10) ? d1 :d0 ;

//*************code***********//

endmodule

思路二:时序逻辑

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output reg [1:0]mux_out

);

//*************code***********//

always @(*) begin

case(sel)

2'b00 : mux_out = d3;

2'b01 : mux_out = d2;

2'b10 : mux_out = d1;

2'b11 : mux_out = d0;

default :mux_out = 2'b00;

endcase

end

//*************code***********//

endmodule

需要注意的是:wire类型不能在always块里赋值,所以思路二要将mux_out改为reg类型

1857

1857

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?