一,在XIINX FPGA中有支持三种AXI总线,有三种AXI协议接口,全局时钟,复位低有效分别是

AXI4:面向高性能地址映射通信需求,是面向地址映射的接口,最大允许256次的数据突发传输;

AXI4-Lite:是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

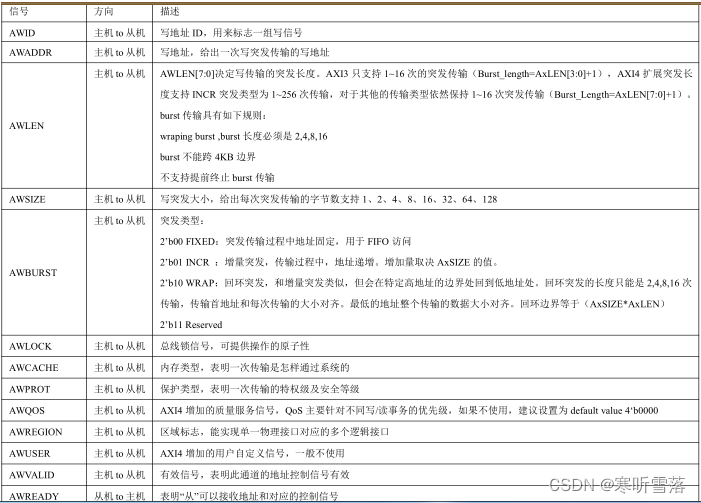

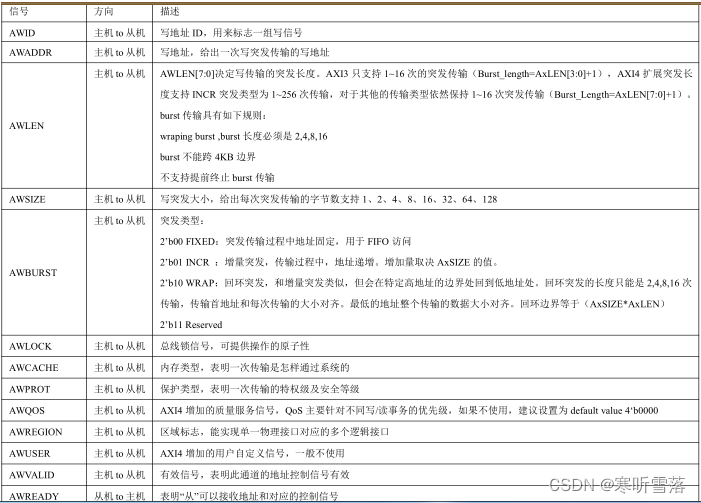

1,写地址通道

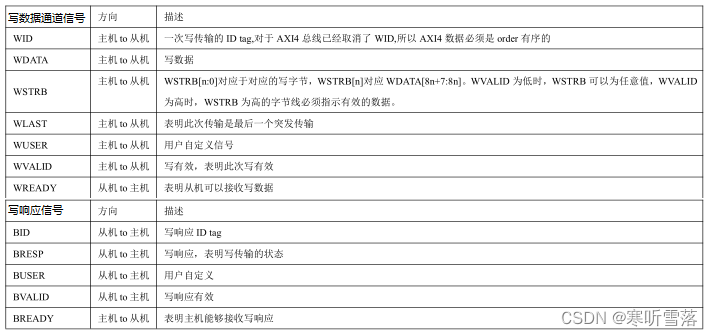

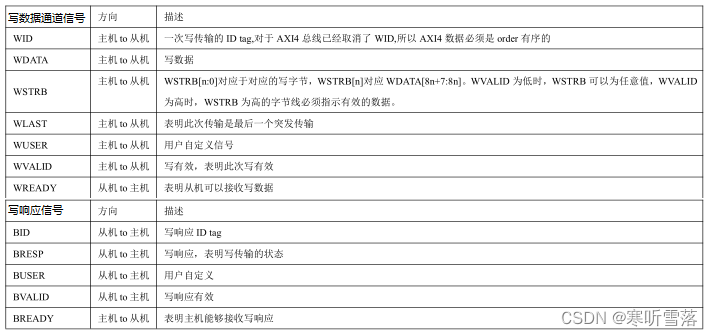

2,写数据通道信号和写响应数据信号

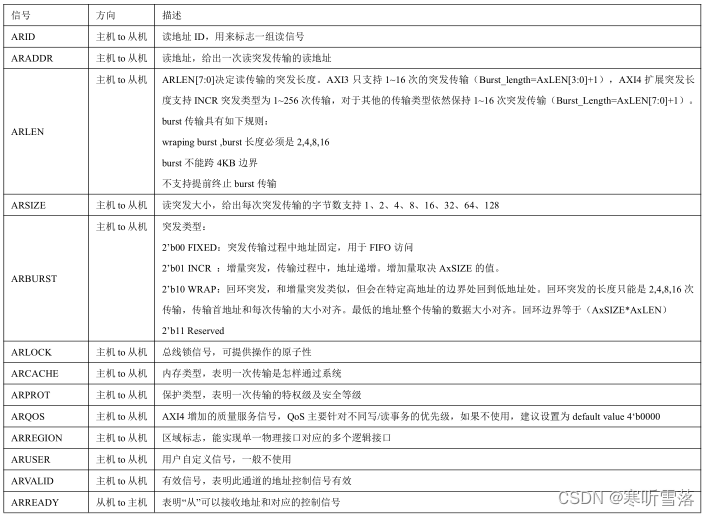

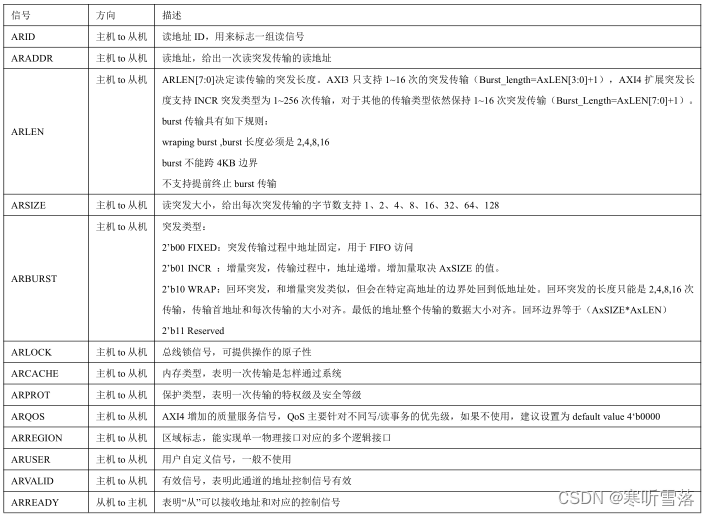

3,读地址通道

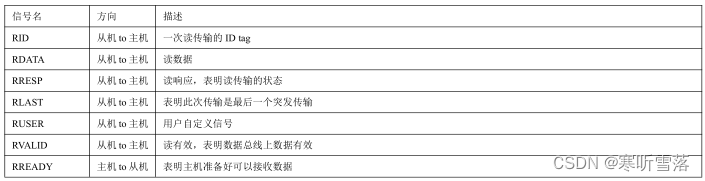

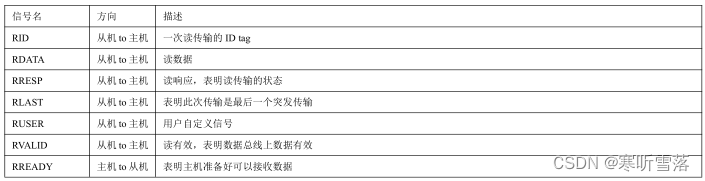

4,读数据通道

二, ax

本文介绍了Xilinx FPGA中AXI4、AXI4-Lite和AXI4-Stream三种总线协议接口,并详细阐述了如何在Vivado 2017.4中搭建axi4-full-master和slave总线,包括IP创建、验证过程以及axi_slave的信号分析,如awaddr、awready、wready、bvalid等,涉及burst模式和数据传输细节。

本文介绍了Xilinx FPGA中AXI4、AXI4-Lite和AXI4-Stream三种总线协议接口,并详细阐述了如何在Vivado 2017.4中搭建axi4-full-master和slave总线,包括IP创建、验证过程以及axi_slave的信号分析,如awaddr、awready、wready、bvalid等,涉及burst模式和数据传输细节。

一,在XIINX FPGA中有支持三种AXI总线,有三种AXI协议接口,全局时钟,复位低有效分别是

AXI4:面向高性能地址映射通信需求,是面向地址映射的接口,最大允许256次的数据突发传输;

AXI4-Lite:是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

1,写地址通道

2,写数据通道信号和写响应数据信号

3,读地址通道

4,读数据通道

二, ax

2833

2833

688

688

1237

1237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?