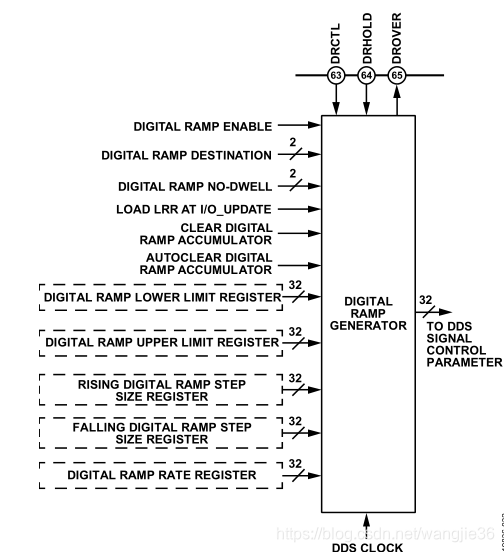

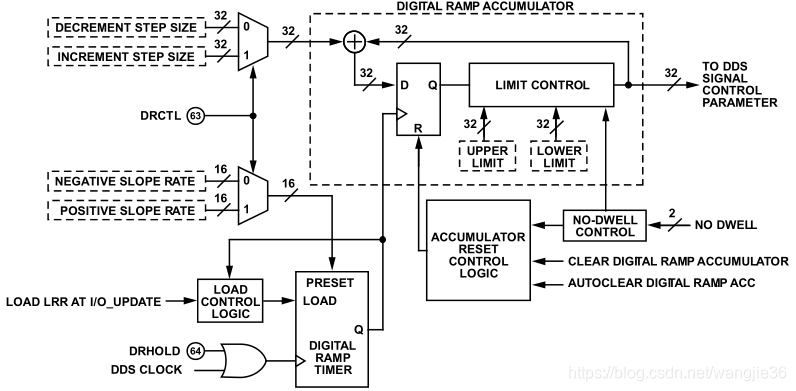

在数字斜坡调制模式中,调制的DDS信号控制参数由数字斜坡发生器(DRG)直接提供。

1,通过控制斜坡发生参数,用户可以控制斜坡的上升和下降斜率。

,

,

2,DRG的斜坡特性参数可完全编程。包括:可以通过编程实现控制斜坡的上限值,下限值,,正/负斜率斜坡的步长和步率单独控制。斜坡方向由DRCTL引脚控制。此引脚上逻辑0可使DRG生成负斜率斜坡,逻辑1产生正斜率斜坡。另外,DRG还支持由DRHOLD引脚控制的保持功能。当此引脚设为逻辑1时,DRG停留在最后的状态中;否则,DRG会正常工作。非DRG目的位定义的DDS信号控制参数取自有效profle。

3,斜坡方向(上升或下降)通过DRCTL引脚外部控制。

用户使 用DRHOLD附加引脚还能保持斜坡发生器的当前状态。

幅度控制必须通过CFR1寄存器中的OSK使能位开启。

直接数字频率合成器(DDS)模块产生参考信号(正弦或余弦 取决于使能正弦输出位0x00[16])。

本文详细介绍了AD9914数字斜坡调制模式的使用,包括通过编程控制斜坡的上升和下降斜率,DRG的完全可编程特性,如斜坡的上限值、下限值、步长和步率。还讨论了DRCTL和DRHOLD引脚的功能,以及DRG的保持和方向控制。此外,内容涵盖了DDS信号的相位和幅度控制,以及数字斜坡使能位对DRG的影响。最后,提到了非驻留斜坡发生模式,增强了DRG的灵活性。

本文详细介绍了AD9914数字斜坡调制模式的使用,包括通过编程控制斜坡的上升和下降斜率,DRG的完全可编程特性,如斜坡的上限值、下限值、步长和步率。还讨论了DRCTL和DRHOLD引脚的功能,以及DRG的保持和方向控制。此外,内容涵盖了DDS信号的相位和幅度控制,以及数字斜坡使能位对DRG的影响。最后,提到了非驻留斜坡发生模式,增强了DRG的灵活性。

订阅专栏 解锁全文

订阅专栏 解锁全文

3645

3645

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?