串行模式下需要使用引脚为

DO: /CS D1:SCLK D2:SDIO D3:SDO

D4: RESET

F0-F3:模式选择 F3:F0 0001

IO_UPDATE 上升沿跟新

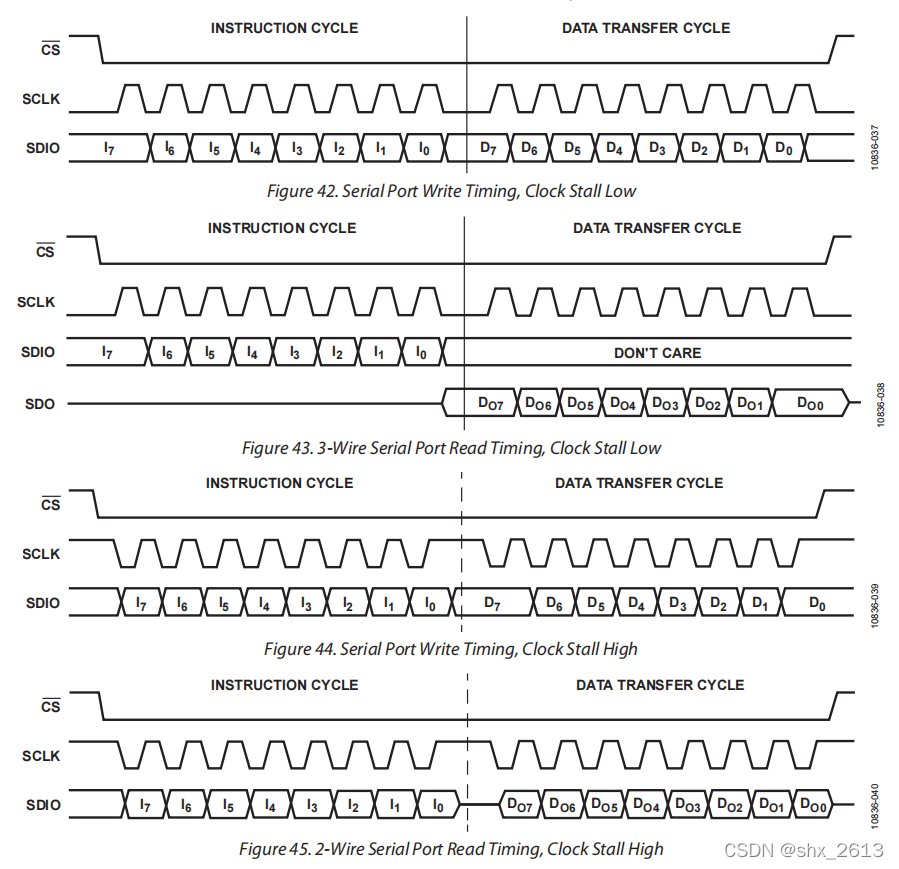

其时序图如下:

注意其 /CS 和 SCLK 的不同 可导致回送数据线的不同

其INSTRUCTION CYCLE 结构为 I7:I1 R/w|x|A5:A0

其 DATA CYCLE 根据寄存器的不同而有不同长度

寄存器描述:

CRF1 0x00 功能控制寄存器,包含 OSK VCO cal 等功能开关

频率控制关系到3个寄存器 0x04 05 06 = FTW B A

Fo = Fs(FTW + A/B)/2^32

Fo < 1/2 Fs

FTW<2^31

A<B

计算 A B FTW 寄存器值的过程,

Fs 为系统工作频率是确定的。

Fo/Fs = M/N, 具体方法为 GCD(Fo/Fs) ,然后除一下。

FTW = M*2^32/N 取整数;

计算中间值 Y = 2^32*M - FTW*N

A/B = Y/N(再次用最大公约数去约一下)

本文详细介绍了微控制器在串行模式下的引脚配置,包括DO、CS、SCLK、SDIOD、SDO和RESET等。同时,讲解了INSTRUCTIONCYCLE和DATACYCLE的时序,以及寄存器CRF10x00的功能。重点阐述了频率控制关系,涉及到的0x040506三个寄存器的FTW、A和B计算方法,用于设置系统工作频率Fo与系统频率Fs的比例。此外,还提到了最大公约数在计算过程中的应用。

本文详细介绍了微控制器在串行模式下的引脚配置,包括DO、CS、SCLK、SDIOD、SDO和RESET等。同时,讲解了INSTRUCTIONCYCLE和DATACYCLE的时序,以及寄存器CRF10x00的功能。重点阐述了频率控制关系,涉及到的0x040506三个寄存器的FTW、A和B计算方法,用于设置系统工作频率Fo与系统频率Fs的比例。此外,还提到了最大公约数在计算过程中的应用。

7395

7395

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?