IC设计的开发阶段

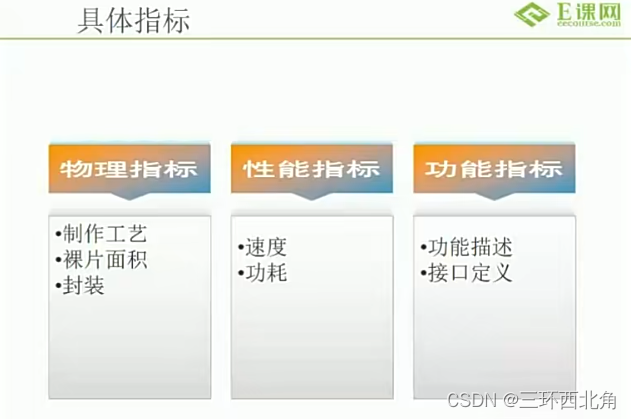

需求分析

和软件开发的需求其实差不多:

功能、性能、物理指标(这个是软件没有的)

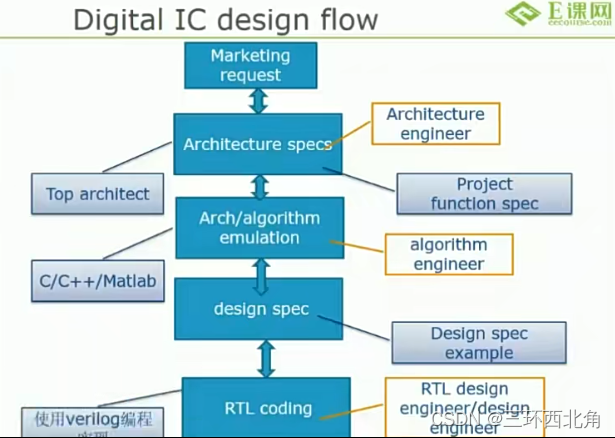

系统架构设计阶段

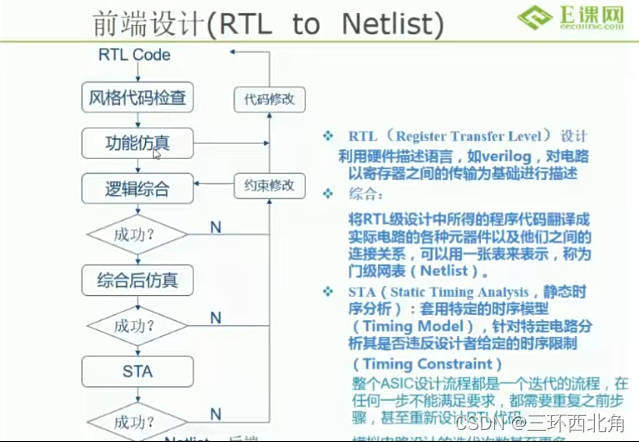

系统架构设计阶段首先使用高级语言进行验证,完成验证后的程序使用verilog或VHDL语言转换为RTL级代码

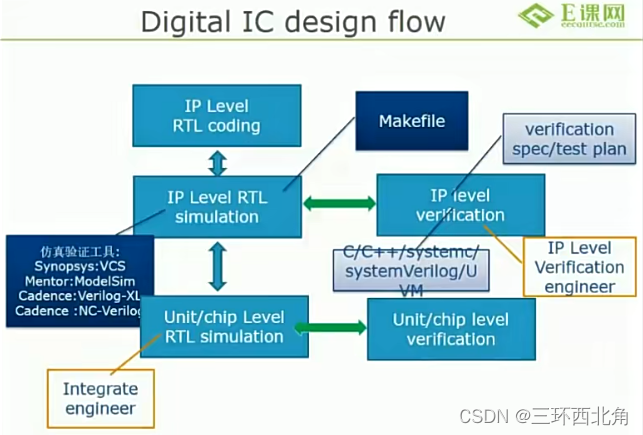

功能仿真与集成阶段

IP级别的代码被拆分成一个个小的功能单元进行开发,完成开发进行集成测试,在完成单元测试后进行集成,并使用集成工具进行测试。

仿真验证工具有:

synopsys:VCS

mentor:modelsim

cadence:verilog-XL

candece:NC-verilog

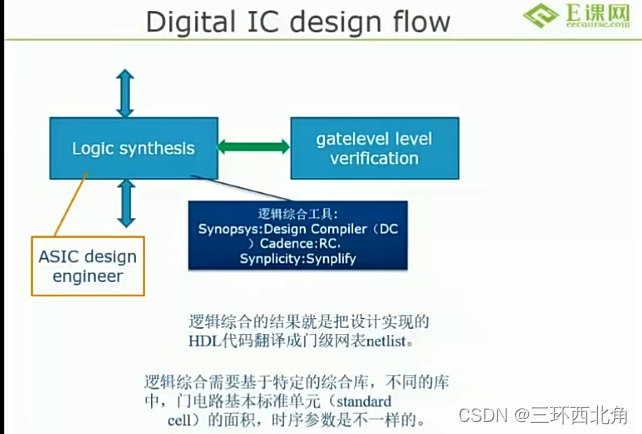

逻辑综合

完成功能仿真后的模块进行逻辑综合,即将RTL级别的代码转换为门级网表netlist。

用到的工具有:

synopsys:Design compiler(DC)

Cadence:RC

Synplicity:Synplify

同时还要从晶圆代工企业导入工艺库,共同进行综合。

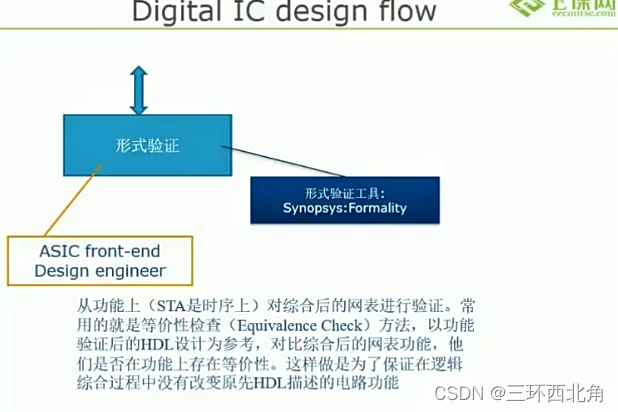

形式验证

以HDL的设计为参考,对比综合后的网表功能,判断是否在功能上存在等价性,确保逻辑综合过程中没有改变显现HDL描述的电路功能。形式验证工具:

synopsys:Formality

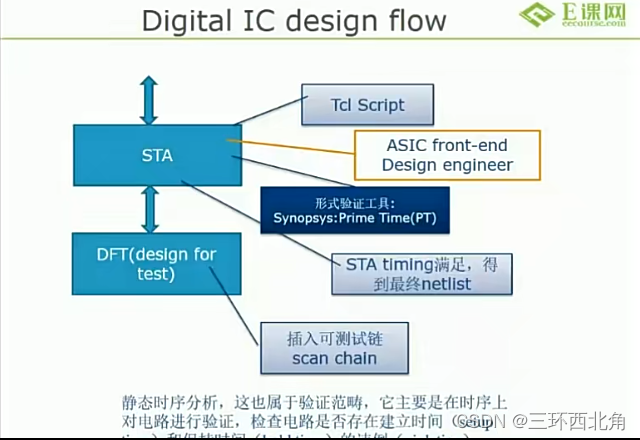

静态时序分析

验证建立时间和保持时间是否存在违例。

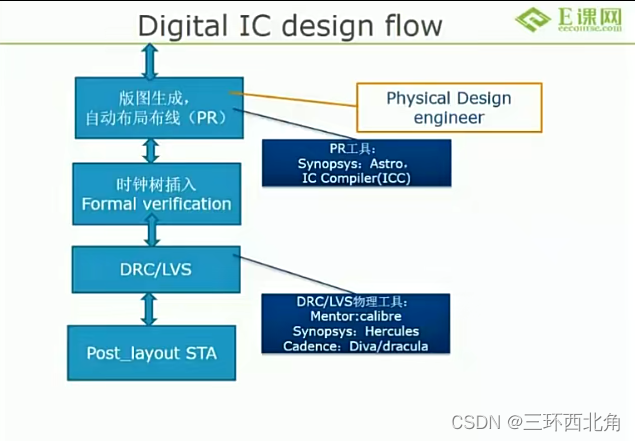

PR/PV

生成后的网表进行版图的自动生成、时钟插入和DRC检查。

前后端阶段划分

前端设计

前端设计从RTL编码开始,直到静态时序检查通过

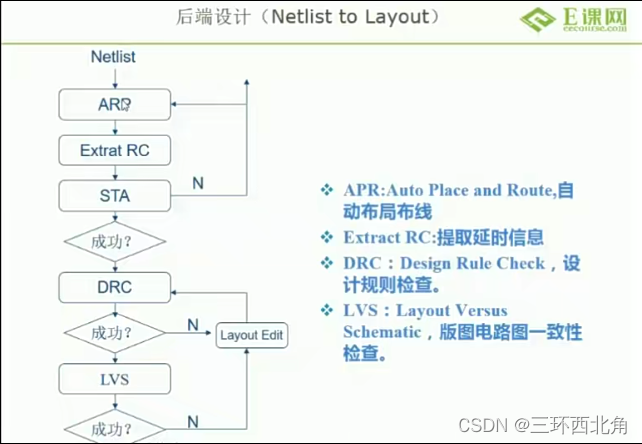

后端设计

后端设计从自动布局布线开始,到版图电路一致性检查结束。

本文详细介绍了IC设计开发过程中的各个阶段,包括需求分析、系统架构设计(高级语言到RTL代码转换)、功能仿真与集成(IP单元开发与测试)、逻辑综合(门级网表生成)、形式验证、静态时序分析以及前后端设计划分,强调了各阶段使用的工具和技术如Verilog和VHDL,以及synopsys和Cadence等在其中的关键作用。

本文详细介绍了IC设计开发过程中的各个阶段,包括需求分析、系统架构设计(高级语言到RTL代码转换)、功能仿真与集成(IP单元开发与测试)、逻辑综合(门级网表生成)、形式验证、静态时序分析以及前后端设计划分,强调了各阶段使用的工具和技术如Verilog和VHDL,以及synopsys和Cadence等在其中的关键作用。

6995

6995

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?