文章目录

数字IC设计流程

数字IC设计流程如下:

需求->芯片定义specification->算法描述(一般用C++)->RTL级描述(Verilog)->HDL功能仿真->逻辑综合(DC)->门级仿真(仿真网表)->形式化验证>物理设计(floor plan,place,cts,route等)->签核(chip finish,StarRC提取寄生RC,PT时序分析,DRC&LVS等)

前端设计

RTL编写和HDL仿真

用Verilog实现芯片各个模块的功能,如写一个四位乘法器multipleir.v和它的测试文件tb_multiplier.v并使用VCS编译并仿真,使用Verdi查看波形,通过RTL功能验证。

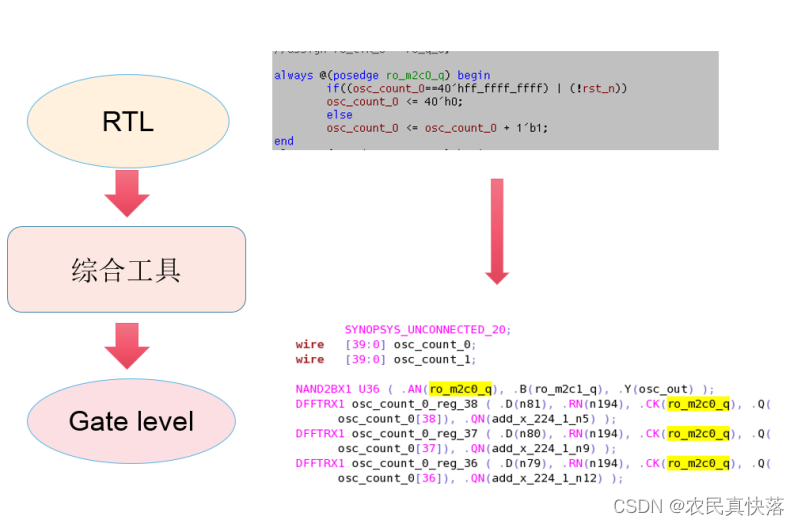

逻辑综合

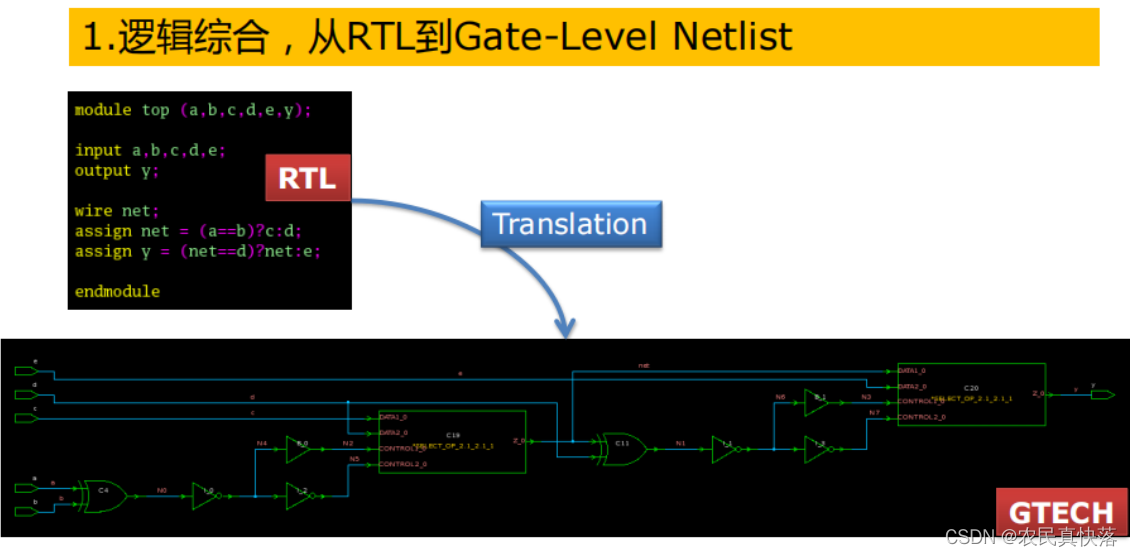

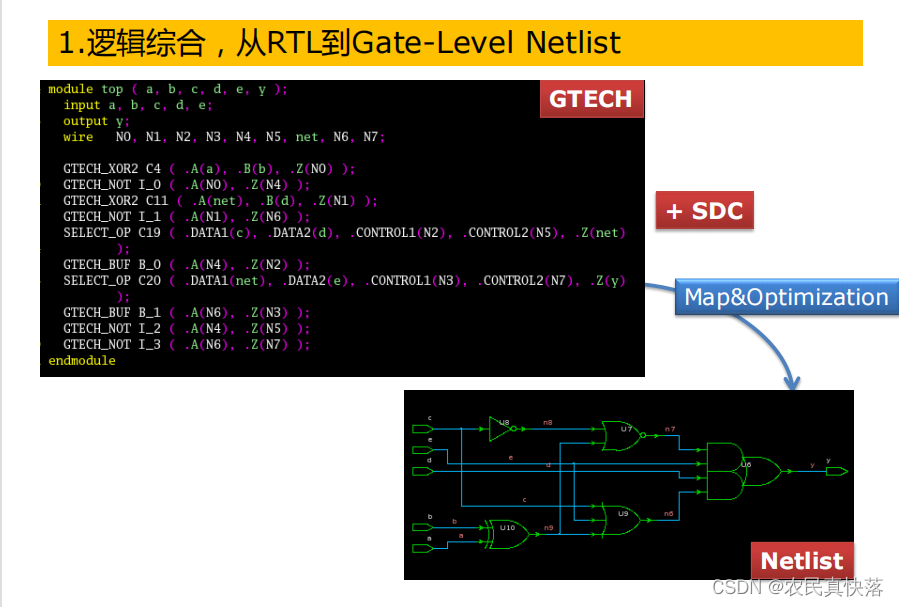

使用DC(Design Compiler)综合RTL代码,生成门级网表(Gate-Level Netlist)。

具体来说,DC实际上将RTL先翻译成 了内部可识别的GTECH形式的中间代码,然后再根据所提供的目标库和设计约束来映射和优化出最终的网表文件netlist.v。

在使用Synopsys DC进行逻辑综合时,基本可以分为四步:

- 预综合过程(设置目标库、链接库等)

- 施加设计约束(如信号从0到1需要的transition time)

- 设计综合(指使用compile命令后进行编译的过程)

- 后综合过程(如将网表文件从内存写出为netlist.v)

门级仿真

使用VCS编译dc生成的网表文件和tb文件,对门级网表进行仿真,进行该仿真的原因是dc设置了时序约束,该仿真会比HDL仿真更加真实。

形式化验证

使用formality进行形式化验证,是对网表文件和RTL代码之间映射的检验,在数学上验证该网表能实现对应RTL的功能。

后端设计

后端工作的输入是前端生成的网表文件和sdc约束文件

后端工作的输出的是GDS(Geometry Data Standard)版图,GDS是描述电路版图的格式,包含制造一颗芯片所需的全部信息,芯片制造商(fab)只需要IC设计公司提交GDS用于芯片生产。

后端工作的目标是生成符合要求的GDS版图,理想的GDS版图要求包括:

- 功能上和RTL一样

- 物理规则上,fab能拿它正常制造

- PPA,即性能,功耗,面积尽可能达到最优

后端设计的**基本流程(basic flow)**如下图所示:

本文详细介绍了数字IC设计的全过程,从前端的RTL编写和HDL仿真,经过逻辑综合和门级仿真,到后端的形式化验证,物理设计包括floorplan、placement、CTS、route等步骤,以及签核阶段的DRC和LVS验证。文章强调了每个阶段的关键任务和常用工具,为读者提供了全面的技术指导。

本文详细介绍了数字IC设计的全过程,从前端的RTL编写和HDL仿真,经过逻辑综合和门级仿真,到后端的形式化验证,物理设计包括floorplan、placement、CTS、route等步骤,以及签核阶段的DRC和LVS验证。文章强调了每个阶段的关键任务和常用工具,为读者提供了全面的技术指导。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?