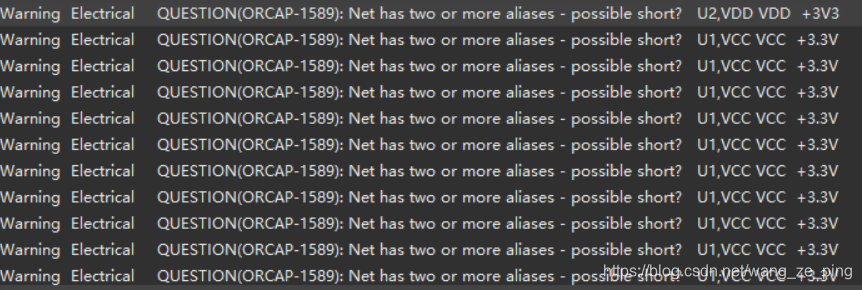

在进行DRC检查时,出现很多如下警告:

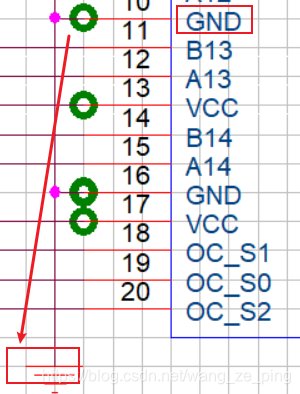

双击警告回到原理图,

出现上述警告的原因时网络名称与标号不相同(aliase本身的意思时别名),但是这并不影响原理图的绘制,解决办法,可以将接地的符号命名为GND等操作

Orcad Capture进行DRC检查出现 Net has two or more aliases

最新推荐文章于 2025-02-07 15:15:35 发布

本文介绍了在进行DRC检查时遇到的网络名称与标号不符警告问题,解释了原因,并提供了通过修改接地符号名(如GND)来消除此类警告的方法,确保原理图绘制的准确性。

本文介绍了在进行DRC检查时遇到的网络名称与标号不符警告问题,解释了原因,并提供了通过修改接地符号名(如GND)来消除此类警告的方法,确保原理图绘制的准确性。

5472

5472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?