注:本文为“CMOS | 时序逻辑单元 / 触发器 ”相关合辑。

图片清晰度受引文原图所限。

略作重排,如有内容异常,请看原文。

从 CMOS 到触发器(一)

posted on 2017-02-25 11:10 IC_learner

本文将探讨基本器件——CMOS 器件及其电路,后文将进一步讨论锁存器和触发器。

本文主要内容如下:

- MOS 晶体管结构与工作原理简述

- CMOS 单元电路与版图

- CMOS 门电路

- CMOS 的功耗表示

CMOS 内容偏重于微电子器件,该领域具有一定难度。本文将聚焦数字设计中可能需要了解的相关知识(若有必要,后续会补充更多内容)。

1、MOS 晶体管结构与工作原理简述

晶体管在数字电路中的核心作用是作为电子开关,通过电压或电流控制其导通与关断。晶体管主要分为两类:双极性晶体管(BJT,bipolar junction transistor)和金属 - 氧化物 - 半导体场效应晶体管(MOSFET 或 MOS,metal - oxide - semiconductor field effect transistor)。本文重点讨论 MOS 晶体管,因 BJT 已非当前数字 IC 设计的主流工艺。

① MOS 晶体管分为 PMOS 和 NMOS,其类型由衬底和掺杂浓度决定。关于其形成过程较为复杂,此处不做赘述,直接介绍其截面结构及工作原理(以下以 NMOS 为例)。

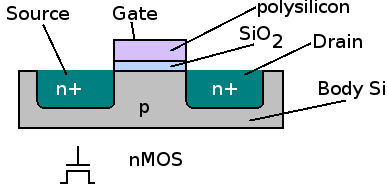

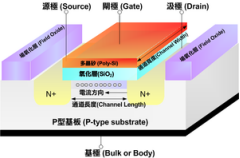

NMOS 晶体管的横截面结构如下所示:

最底层为硅晶圆衬底(substrate)(图中 Body Si 处),顶部为导电的栅极(gate),中间是二氧化硅构成的绝缘层。早期栅极由金属制成,故得名金属 - 氧化物 - 半导体,目前栅极多采用多晶硅(poly)。MOS 结构中,金属(多晶硅)与半导体衬底之间的二氧化硅会形成电容。

需要重点记住的是,NMOS 晶体管的衬底为 P 型,衬底上有两个 n 型掺杂区域,分别称为源极(Source)和漏极(Drain)(由于器件对称性,源极和漏极可互换定义,在连接电源和地后才被明确区分),顶部中间为栅极(Gate),这构成了 NMOS 的三个电极(实际 MOS 为四端器件,衬底亦为一端)。

NMOS 晶体管的工作原理如下:

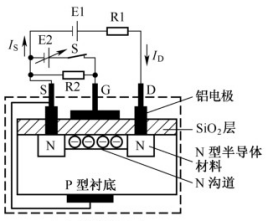

如左图所示,施加电压后,源极可视为电子的源头,漏极可视为电子流出的开口,栅极则像控制开关:当栅极施加高电平电压时,源漏之间形成沟道,电子通过沟道从源极流向漏极,电流方向为从漏极到源极,此时“开关”导通(因形成N沟道,由电子导电,故称为 N 型 MOS);当栅极施加低电平电压时,沟道关断,源漏之间断开,“开关”截止。

PMOS 的工作原理与之相反:栅极施加低电平电压时导通,施加高电平电压时关断。

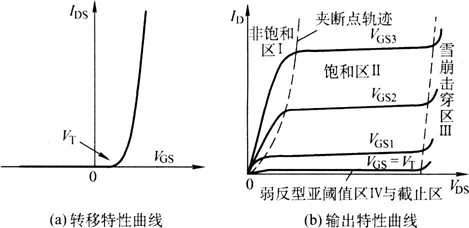

注意:栅极电压需达到特定值时沟道才会形成,该电压称为阈值电压( V th V_{\text{th}} Vth)。

② 下面介绍 MOS 晶体管的

I

I

I -

V

V

V 特性曲线(包括转移特性曲线和输出特性曲线):

对于 NMOS,工作时源极(S)接地,漏极(D)接数字电源, V ds V_{\text{ds}} Vds 通常保持不变,栅极(G)电压决定沟道是否导通。工作时, V g V_{\text{g}} Vg(输入信号电压)为定值,非高即低。由此可知,NMOS 工作时存在从电源( V DD V_{\text{DD}} VDD)到地(GND)的电流(从 D 到 S)。

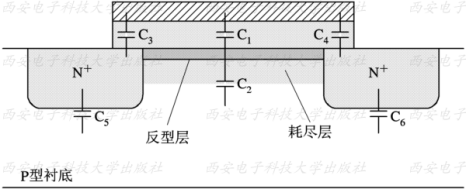

③ MOS 晶体管内部存在寄生电容,如图所示:

主要包括:

- 栅和沟道之间的氧化层电容 C 1 C_1 C1;

- 衬底和沟道之间的耗尽层电容 C 2 C_2 C2;

- 多晶硅栅与源极、漏极交叠产生的电容 C 3 C_3 C3 和 C 4 C_4 C4;

- 源/漏区与衬底之间的结电容 C 5 C_5 C5 与 C 6 C_6 C6。

2、CMOS 单元电路与版图

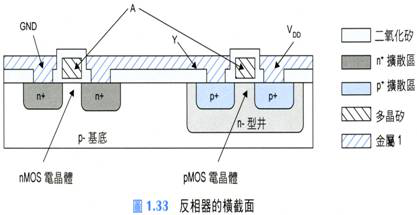

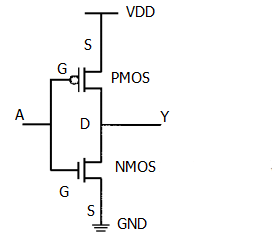

当前主流工艺为 CMOS(互补型半导体,Complementary MOS)工艺,该工艺将 PMOS 和 NMOS 晶体管构成一个单元,称为 CMOS 单元或反相器单元。其结构是将 PMOS 和 NMOS 集成在同一晶圆上,栅极相连,漏极相连,结构图如下(电路符号和功能后续介绍):

上图中,左侧为 NMOS,右侧为 PMOS。 A A A 为共连栅极输入, Y Y Y 为共连漏极输出, V DD V_{\text{DD}} VDD 连接 PMOS 的源极,GND 连接 NMOS 的源极。

CMOS 反相器对应的电路符号图如下:

下面通过分析 CMOS 反相器的工作原理,说明其成为主流工艺的原因:

- 当输入信号 A = 1 A = 1 A=1 时,PMOS 关断,NMOS 导通,输出信号 Y Y Y 的电压等同于 GND 电压,即 Y = 0 Y = 0 Y=0;此时 V DD V_{\text{DD}} VDD 到 GND 的供电回路未导通,理论上无电流流过,功耗为 0。

- 当输入信号 A = 0 A = 0 A=0 时,PMOS 导通,NMOS 关断,输出信号 Y = V DD = 1 Y = V_{\text{DD}} = 1 Y=VDD=1;此时 V DD V_{\text{DD}} VDD 到 GND 的供电回路同样未导通,理论上无电流流过,功耗为 0。

因此,理论上反相器传输信号时功耗极低,这是 CMOS 工艺成为主流的重要原因。

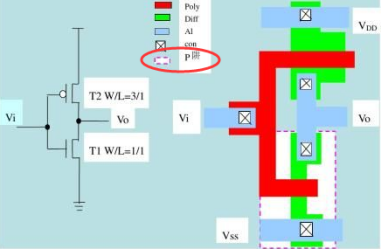

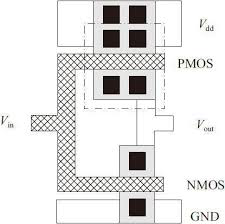

CMOS 单元的版图如下:

左图为 CMOS 电路符号,右图为版图(示意)。该版图基于 p 阱 CMOS 工艺:从下往上看,金属(蓝色)连接至数字地( V ss V_{\text{ss}} Vss);白色背景红色虚线边框的 P 阱区域中,下方绿色掺杂区域形成 NMOS,上方绿色掺杂区域形成 PMOS;绿色掺杂区域分布在红色多晶硅附近,多晶硅相连(即 PMOS 和 NMOS 的栅极相连),通过金属引出(X 表示通孔)作为输入 V i V_i Vi;NMOS 的源极通过通孔与金属连接;NMOS 和 PMOS 的漏极通过通孔连接至同一金属,作为输出;PMOS 的源极通过通孔连接至金属,再连接到数字电源。

右图中展示了左图的宽长比:NMOS 的沟道宽长比为 1 : 1 1:1 1:1,PMOS 的宽长比为 3 : 1 3:1 3:1(可通过栅与有源掺杂区的重叠部分理解器件宽长比,栅的宽度大致为沟道长度)。手绘版图时需注意区域覆盖顺序:基本衬底在最底层,依次为阱衬底、有源掺杂区、栅,最上层为金属和通孔。

更抽象的 N 阱 CMOS 工艺版图如下:

版图的详细知识可参考专业书籍。

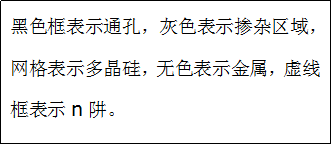

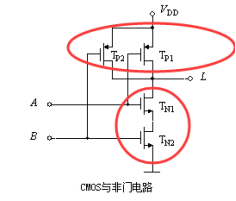

3、CMOS 门电路

① CMOS 非门:上述 CMOS 单元即实现非门功能,也称为反相器,其电路结构为反相器电路结构。

② (二输入)CMOS 与非门(NAND):

电路符号结构如下:

(PMOS 电路符号栅极处的小圈圈表示低电平有效)

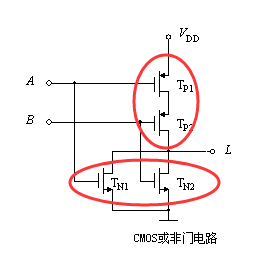

③ (二输入)CMOS 或非门(NOR)的电路符号和工作原理如下:

(PMOS 电路符号栅极处的小圈圈表示低电平有效)

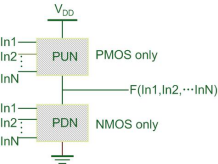

数字逻辑电路均可由上述三种电路化简构成。反相逻辑门的通用结构如下:

可观察到:实现“与”功能时,NMOS 网络为串联;实现“或”功能时,NMOS 网络为并联。记忆方法:NMOS 全部导通才能实现“与”功能,任意一个导通即可实现“或”功能,可根据 NMOS 的串并结构判断逻辑关系。

设计多输入门电路时,将对应数量的 NMOS 进行串/并联,PMOS 则采用并/串联结构。

4、CMOS 的功耗表示

功耗是单位时间内消耗的能量,数字系统中的功耗主要包括静态功耗和动态功耗,下面从 CMOS 电路角度进行介绍。

CMOS 静态功耗:指 CMOS 电路不翻转/不工作时的功耗。当 CMOS 电路不工作(晶体管均处于截止状态)时,

V

DD

V_{\text{DD}}

VDD 到 GND 仍存在微弱电流,即静态电流

I

dd

I_{\text{dd}}

Idd(电源与地之间的漏电流,与器件相关)。根据

P

=

U

I

P = UI

P=UI,静态功耗表示为:

P

s

=

I

dd

⋅

V

dd

P_{\text{s}} = I_{\text{dd}} \cdot V_{\text{dd}}

Ps=Idd⋅Vdd

CMOS 动态功耗:指信号在 0 和 1 之间变化时,电容充放电所消耗的功耗。除 CMOS 器件的寄生电容外,导线间也存在电容。将电容 C C C 充电至电压 V dd V_{\text{dd}} Vdd 所需能量为 C V dd 2 CV_{\text{dd}}^2 CVdd2。若电容每秒切换 f f f 次(即切换频率为 f f f,每秒内充电 f / 2 f/2 f/2 次,放电 f / 2 f/2 f/2 次),由于放电无需从电源获取能量,动态功耗表示为:

P d = 1 2 ⋅ C ⋅ V dd 2 ⋅ f P_{\text{d}} = \frac{1}{2} \cdot C \cdot V_{\text{dd}}^2 \cdot f Pd=21⋅C⋅Vdd2⋅f

注:动态功耗还包括栅极信号翻转时 PMOS 和 NMOS 同时导通引起的短路功耗等,本文主要关注上述两种功耗,低功耗设计相关内容将在后续详述。

本文图片主要来自 Google 网络,部分来自《数字 IC 系统设计》。

从 CMOS 到触发器(二)

posted on 2017-02-26 03:17 IC_learner

前文介绍了 CMOS 器件,本文将继续探讨锁存器和触发器,主要内容如下:

- 双稳态器件

- 锁存器常见结构

- 锁存器的应用

- 触发器

- 触发器的建立时间和保持时间

1、双稳态器件

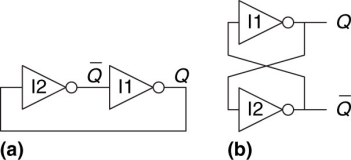

双稳态器件是指具有两种稳定状态(0 和 1)的器件,是存储器件的基本模块,其一种电路结构为交叉耦合反相器结构,如下图所示:

两个反相器相连构成双稳态器件,分析如下:

假设第一个反相器 I 1 I_1 I1 的输出为 1(即 Q = 1 Q = 1 Q=1),则第二个反相器 I 2 I_2 I2 的输入为 1,输出 Q ′ = 0 Q' = 0 Q′=0,该输出反馈至 I 1 I_1 I1 的输入,使 Q Q Q 稳定为 1,此为一种稳定状态。

假设 I 1 I_1 I1 的输出为 0(即 Q = 0 Q = 0 Q=0),则 I 2 I_2 I2 的输入为 0,输出 Q ′ = 1 Q' = 1 Q′=1,反馈至 I 1 I_1 I1 的输入,使 Q Q Q 稳定为 0,此为另一种稳定状态。

因此,交叉耦合反相器结构为双稳态器件。但电路可能存在第三种状态——亚稳态(非稳定状态),后续将详细介绍。

双稳态器件是锁存器、寄存器等存储器件的基础,因其具有两种稳定状态,可用于存储数据。

2、常见的锁存器结构

交叉耦合反相器无输入,无法存储输入数据,因此需要具有输入的双稳态电路,即锁存器。最基本的锁存器为 S-R 锁存器,常用的为 D 锁存器,下面分别介绍。

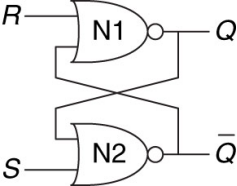

① SR 锁存器

SR 锁存器是最简单的时序单元,由一对交叉耦合的或非门构成,如下所示:

其功能通过输入

S

S

S、

R

R

R 端控制

Q

Q

Q 的置位(set)和复位(reset)。

或非门的功能为:只要有一个输入为 1,输出就为 0。

下面分析输入

R

S

RS

RS 的 4 种组合对输出

Q

Q

Q 的影响:

-

输入 R = 0 R = 0 R=0, S = 0 S =0 S=0 时:

对于或非门 N 1 N_1 N1,输入为 0 0 0 和 Q ′ Q' Q′;对于或非门 N 2 N_2 N2,输入为 0 0 0 和 Q Q Q。

通过假设初始状态可知:

若原状态 Q = 0 Q = 0 Q=0,则 Q ′ = 1 Q' = 1 Q′=1,反馈后状态保持稳定;

若原状态 Q = 1 Q = 1 Q=1,则 Q ′ = 0 Q' = 0 Q′=0,反馈后状态同样保持稳定。

因此, S R = 00 SR = 00 SR=00 时,输出保持原状态。 -

输入 S = 1 S = 1 S=1, R = 0 R = 0 R=0 时:

或非门 N 2 N_2 N2 因 S = 1 S = 1 S=1 输出 Q ′ = 0 Q' = 0 Q′=0;

或非门 N 1 N_1 N1 输入为 0 0 0 和 0 0 0,输出 Q = 1 Q = 1 Q=1,反馈后状态稳定。

此时输出 Q = 1 Q = 1 Q=1,实现置位功能。 -

输入 S = 0 S = 0 S=0, R = 1 R = 1 R=1 时:

与 S R = 10 SR = 10 SR=10 类似,输出 Q = 0 Q = 0 Q=0,实现复位功能。 -

输入 S = 1 S = 1 S=1, R = 1 R = 1 R=1 时:

或非门 N 1 N_1 N1 和 N 2 N_2 N2 输出均为 0 0 0,即 Q = Q ′ = 0 Q = Q' = 0 Q=Q′=0,与输出逻辑定义冲突,为错误输出。

实际应用中需避免 S S S 和 R R R 同时有效。

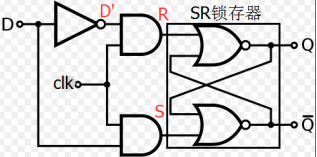

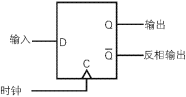

② D 锁存器

SR 锁存器存在 S S S 和 R R R 同时有效导致输出错误的问题,且数据存储与时间关联不明确,因此衍生出 D 锁存器。其结构和电路符号如下:

D 锁存器由前级门电路(2 个与门和 1 个非门)和后级 SR 锁存器(2 个或非门)组成,共含 22 个晶体管。输入为 C l k Clk Clk 和 D D D,功能分析如下:

-

当 c l k = 0 clk = 0 clk=0 时:

S = 0 S = 0 S=0 且 R = 0 R = 0 R=0,SR 锁存器输入为 00 00 00,输出 Q Q Q 和 Q ′ Q' Q′ 保持原状态,即输出不随 D D D 变化。 -

当 c l k = 1 clk = 1 clk=1 时:

R = D ′ R = D' R=D′ 且 S = D S = D S=D,SR 锁存器输入互补(无同时有效情况)。

若 D = 1 D = 1 D=1,则 S = 1 S = 1 S=1 实现置位, Q = 1 Q = 1 Q=1;

若 D = 0 D = 0 D=0,则 R = 1 R = 1 R=1 实现复位, Q = 0 Q = 0 Q=0。

此时输出 Q = D Q = D Q=D,输入数据直达输出。

综上,该 D 锁存器为高电平敏感锁存器: c l k = 1 clk = 1 clk=1 时输出随输入 D D D 变化(数据透明传输); c l k = 0 clk = 0 clk=0 时输出保持原状态(锁存数据),故也称为透明锁存器。

3、D 锁存器的应用

① 防电路毛刺:常用于门控时钟电路,通过锁存功能过滤信号中的毛刺干扰(详见相关门控电路文档)。

② 构造触发器:是构成触发器的基础模块,后续将详细介绍。

③ 锁定锁存器(lockup latch):用于修复扫描链插入时的时钟偏移问题,解决保持时间违规。

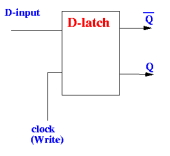

4、D 触发器

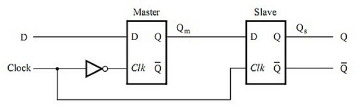

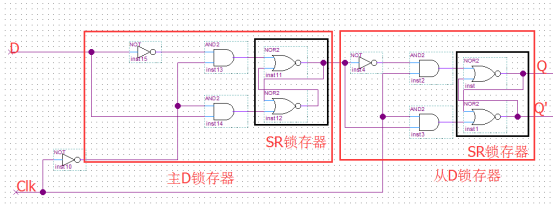

触发器有 J-K、T、D 等类型,其中 D 触发器最为简单,由两个 D 锁存器(主锁存器和从锁存器)构成,驱动时钟相位相反,共含 46 个晶体管。其结构和电路符号如下:

功能分析如下:

-

当 c l k = 0 clk = 0 clk=0 时:主锁存器导通,输入数据 D D D 传输至主锁存器输出 Q m Q_m Qm;从锁存器截止,输出 Q s Q_s Qs 保持原状态。

-

当 c l k clk clk 从 0 → 1 0 \to 1 0→1(上升沿)时:主锁存器截止, Q m Q_m Qm 保持当前值;从锁存器导通, Q s = Q m Q_s = Q_m Qs=Qm,即输出锁存上升沿时刻的数据。

-

当 c l k = 1 clk = 1 clk=1 时:主锁存器截止, Q m Q_m Qm 不变;从锁存器导通, Q s Q_s Qs 保持 Q m Q_m Qm 的值。

-

当 c l k clk clk 从 1 → 0 1 \to 0 1→0 时:主锁存器准备导通以传输新数据;从锁存器截止, Q s Q_s Qs 保持原锁存值。

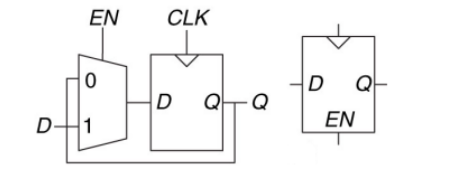

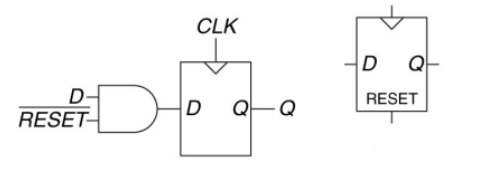

这种在时钟上升沿锁存数据的触发器称为正边沿触发器,另有负边沿触发器(下降沿锁存),原理类似。由 D 触发器可扩展出寄存器(多 bit 存储)、带使能/复位的触发器等,例如:

(带使能的触发器)

(带复位的触发器)

5、D 触发器的建立时间和保持时间

定义

-

建立时间( T setup T_{\text{setup}} Tsetup 或 T su T_{\text{su}} Tsu):时钟有效沿到来前,数据必须稳定的最短时间。若数据到达时间晚于该值,触发器无法正确锁存数据。

-

保持时间( T hold T_{\text{hold}} Thold 或 T h T_{\text{h}} Th):时钟有效沿到来后,数据必须稳定的最短时间。若数据提前变化,触发器同样无法正确锁存数据。

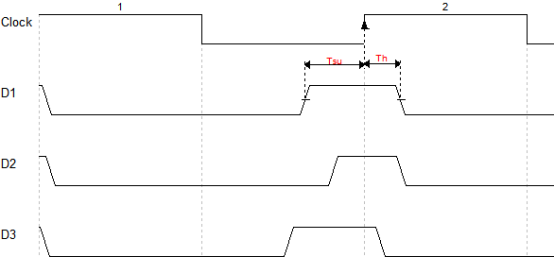

示意图

图中 D 1 D_1 D1 满足建立时间和保持时间,可被正确锁存; D 2 D_2 D2 建立时间不足, D 3 D_3 D3 保持时间不足,均无法正确锁存。

物理原因

以 D 触发器的门级结构为例(如图所示):

-

建立时间:时钟上升沿( 0 → 1 0 \to 1 0→1)时,主锁存器需完成数据锁存。若数据到达过晚(建立时间不足),无法在时钟信号稳定前传输至主锁存器的关键节点,导致锁存错误。

-

保持时间:时钟上升沿后,主锁存器需维持锁存数据直至从锁存器稳定。若数据提前变化(保持时间不足),新数据可能干扰主锁存器的稳定状态,导致从锁存器获取错误值。

结论:建立时间和保持时间由器件延迟(门延时、线延时)决定,是保证触发器正确工作的时序约束。通常保持时间小于建立时间,具体值与工艺和器件结构相关。

via:

- 从CMOS到触发器(一) - IC_learner - 博客园

https://www.cnblogs.com/IClearner/p/6441265.html- 关于 CMOS 工艺中阱的问题,可参考:

CMOS 工艺阱的选择 - 道客巴巴

https://www.doc88.com/p-065160919221.html

- 关于 CMOS 工艺中阱的问题,可参考:

- 从CMOS到触发器(二) - IC_learner - 博客园

https://www.cnblogs.com/IClearner/p/6443539.html

934

934