注:本文为芯片设计、制造等相关文章的几篇合辑。

文中部分插图受原文图源所限不清晰,如有其他图片因 csdn “过敏” 不显示,可到文末看原文链接。

半导体知识及芯片发展史

半导体材料与工艺 2024 年 01 月 11 日 20:46 江苏

1、重温半导体飞速发展的半个世纪

什么是半导体?

半导体是导电性介于导体和绝缘体中间的一类物质。与导体和绝缘体相比,半导体材料的发现是最晚的,直到 20 世纪 30 年代,当材料的提纯技术改进以后,半导体的存在才真正被学术界认可。

半导体主要由四个组成部分组成:集成电路、光电器件、分立器件、传感器,由于集成电路又占了器件 80% 以上的份额,因此通常将半导体和集成电路等价。

集成电路按照产品种类又主要分为四大类:微处理器,存储器,逻辑器件,模拟器件。通常我们统称他们为芯片。

提起芯片,很多人可能见过,就是一块黑色类似于小盒子的东西,它是由晶体管组成的。

什么是晶体管呢?

严格意义上讲,晶体管泛指一切以半导体材料为基础的单一元件,包括各种半导体材料制成的二极管、三极管、场效应管、可控硅等。晶体管有时多指晶体三极管。

所以我们可以知道:由半导体材料制造出了晶体管,由晶体管组成了芯片。

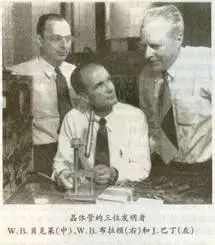

2、晶体管的诞生

晶体管的发明,最早可以追溯到 1929 年,当时工程师利莲费尔德就已经取得一种晶体管的专利。但是,限于当时的技术水平,制造晶体管的材料达不到足够的纯度,而使其无法制造出来。

1947 年 12 月,美国贝尔实验室的肖克利、巴丁和布拉顿组成的研究小组,研制出一种点接触型的锗晶体管。

1956 年,肖克利、巴丁、布拉顿三人,因发明晶体管同时荣获诺贝尔物理学奖。肖克利也被誉为晶体管之父。

芯片有如此强大的功能,为什么晶体管可以胜任呢?

我们知道对于数字电路来讲,逻辑是其精髓所在,所有的功能归根结底,都可以说是逻辑功能。而逻辑的基本构成元素是逻辑 0 和逻辑 1。

而晶体管恰好具备这种功能 – 通过电信号来控制自身开合,以开关的断开和闭合来代表 0 和 1。

3、历史中的八卦

当然,一味的讲原理或者讲历史就没意思了,我们来挖掘半导体发展过程中的八卦。

前面有提到过,被誉为「晶体管之父」的肖克利,出生于伦敦,三岁时随父母漂洋过海来到加州。受父母对他科学思想的灌输,考入 MIT,随后获得固体物理学博士,留校任教。

后来,被位于新泽西州的贝尔实验室副主任凯利来麻省「挖墙角」,将肖克利挖走了。当晶体管发明成功后,肖克利并不满足,他依然进行着不断地尝试,希望发明性能更好的晶体管,并将其商品化。

与此同时,高纯硅的工业提炼技术已成熟,用硅晶片生产的晶体管收音机也问世。在贝尔实验室工作的肖克利坐不住了,他看到了未来的商机,而现在只能看着贝尔实验室拿他的发明赚钱,并且晶体管的性能不稳定有损个人声誉。

最后,矛盾爆发了!当然最终还是因为利益。

4、硅谷诞生

1955 年,肖克利回到了自己的家乡圣克拉拉(Santa Clara)谷,并得到了贝克曼的支持,创办了自己的公司。

圣克拉拉位于旧金山湾区南部,地理位置优越环境优美,气候清新宜人,交通便利。从此,这一片狭长的山谷举世闻名。

肖克利在创办了自己的公司后,依靠自身的威望,很快招到了一批学识渊博,技术过硬的人才。此时,我们仿佛看到一家半导体商业巨头正要崛起,屹立于世界之巅,但是,总有意外发生。

硅谷八叛将。

肖克利虽然是一个聪明绝顶的天才,但却不是一个好的管理者。在公司发展方向上,几乎由他一人掌控,专横独裁,而且他不知道自身的缺陷,也不接受同事的合理化建议,最终导致公司在很长一段时间里都没有产品做出来。

在同事关系上,他忽略了最重要的两点 – 尊重与信任,肖克利通过各种办法,牢牢的将技术专利掌握在自己的手中,这种自私自利的管理方式,终将会让公司走向没落。

1957 年 9 月 18 日,以诺伊斯为首的八位年轻人愤然提出离职,肖克利得知后勃然大怒,骂其曰「八叛逆」(Traitorous Eight)。

硅谷八叛将分别为:诺依斯(N. Noyce)、摩尔(R.Moore)、布兰克(J.Blank)、克莱尔(E.Kliner)、赫尔尼(J.Hoerni)、拉斯特(J.Last)、罗伯茨(S.Boberts)和格里尼克(V.Grinich)

5、传奇的仙童

很快,这八个人就拿到了一笔风险投资,投资人是具有远见卓识的谢尔曼・菲尔柴尔德,成立了仙童半导体(Fairchild),公司是以投资人命名。

公司由谢尔曼・菲尔柴尔德控股,管理人为诺伊斯。在新型的管理模式下,仙童半导体快速发展,不到半年的时间里就已经开始盈利。

与此同时,仙童的两项发名专利,更使其立于世界的半导体之:一,是平面工艺,是一种制造半导体电路的工艺方法,发明人为约翰・霍尔尼(Jean Hoerni)。

另一个发明专利便是集成电路。

顾名思义,集成电路就是用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上。

1958 - 1959 年,来自仙童的罗伯特・诺伊斯(Robert Noyce)发明了硅集成电路。事实上,在早些时候,来自德州仪器的杰克・基尔比(Jack Kilby)发明了锗集成电路。由于两人在同一年独立且不知情的情况下分别发明了集成电路,所以两人共享集成电路发明者的荣誉。

现在,在我们眼里看来,把多个电路集成到一起而减少面积是个自然而然的事情,然后这个简单的想法,却改变了我们的世界。很多伟大的发明,往往源自一个很简单的想法。也许,即使没有这两位,依然有人会想到这个点子,但是历史只会记住最先吃螃蟹的人。

此时的仙童半导体公司风光无限,而半导体行业在那时宛若一个巨大的金矿,任凭仙童肆意挖掘。而仙童的股权大部分都在投资人谢尔曼・菲尔柴尔德的手里,与此同时,仙童半导体公司的利润被不断转移到东海岸,去支持 Fairchild 摄影器材公司,此时仙童的员工开始坐不住了,开始了新一轮的离职创业潮。

6、花开遍地

1968 年,诺依斯(N. Noyce)和摩尔(R.Moore)从仙童离职后创办了我们所熟知的英特尔(Intel),这里的摩尔就是我们所熟知的摩尔定律的提出者。摩尔定律:集成电路芯片上所集成的晶体管数目,每隔 18 个月就翻一倍。

1969 年,杰里・桑德斯(J. Sanders)当时在仙童担任销售部的主任,带着 7 位仙童员工创办 AMD。

还有许多我们所熟知的公司,比如美国国家半导体(现已被 TI 收购),Altera(现已被英特尔收购)等的创始人都出自仙童半导体公司。

正如江湖流传的苹果公司乔布斯形象比喻的那样:「仙童半导体公司就像个成熟了的蒲公英,你一吹它,这种创业精神的种子就随风四处飘扬了。」

随后,英特尔, TI,三星等巨头开始在世界的舞台大放异彩!

在处理器(CPU)领域,英特尔的发展史代表了处理器的发展史。

1971 年,英特尔推出了它的第一款处理器:4004,这是一款 4 位的处理器,仅包含 2300 个晶体管,现在来看,这款处理器简直就是个小弱,但它的诞生意义重大,实现了从 0 到 1 的突破。

1978 年,英特尔推出了一款 16 位的处理器:i8086。

1979 年,英特尔又推出了 8088,8088 是第一个成功应用于个人电脑的 CPU。

1982 到 1989 年,期间又陆续推出了 80286、80386、80486 微处理器。

1993 年奔腾处理器横空出世,2005 年酷睿走进大众的视野,酷睿 i3、i5、i7 成为 PC 的主流。

英特尔,AMD 主要做 PC,服务器的芯片。对于现在炙手可热的智能手机,处理器的竞争则更为激烈。苹果、三星、高通一直占领着高端机的市场,国内近几年半导体业强势崛起,海思,展讯可谓国内的代表。

纵观过去的半个世纪,半导体的迅猛发展为我们的科技爆炸提供了基础。当 10 nm 的芯片已经商用,7nm、5nm 制程已经接近极限的情况下,摩尔定律似乎已经开始走向终点,半导体下一个转折点在哪里,我们还不能确定,但目前量子技术的发展似乎给我们指明了方向。

随着量子通信,量子纠缠等新鲜词语开始出现在我们的视野中,量子芯片也横空出世,与传统芯片用 0 和 1 进行运算处理不同,量子芯片具备多个量子位,而不是再只有 0 和 1 两种逻辑状态,这样使得芯片的运算能力成指数增长,从而突破摩尔定律的限制。

回顾半导体发展的辉煌历史,也在一定程度上代表了人类的文明史。如果说机械的发展解放了人类的劳动力,那么半导体的发展则解放了人类的计算力。而且半导体的发展势头绝不会就此停歇,必将随着科技的发展大放异彩,对我们每个人来讲,未来的半导体,未来的世界,值得我们期待。

7、中国的芯片制造究竟处在什么水平?

总结几个关键词:发展很快,落后两代,技术受限,产品低端。

总的来说,中国的芯片制造技术在快速发展,同时存在工艺落后、产能不足、人才紧缺等问题。

中国集成电路行业共分芯片封装、设计、制造三部分,总体呈现高速增长状态。2004 年至 2017 年,年均增长率接近 20%。2010 至 2017 年间,年均复合增长率达 20.82%,同期全球仅为 3% - 5%。

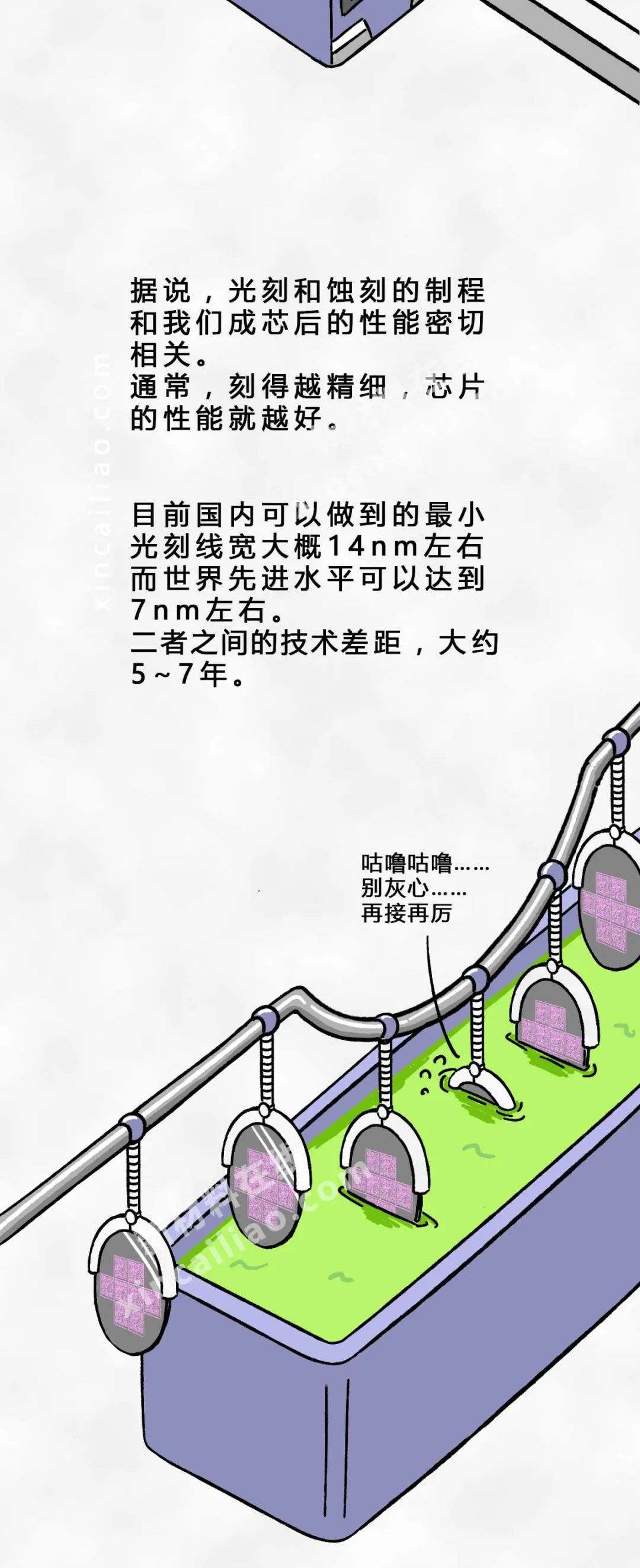

但是另一方面,中国集成电路制造工艺落后国际同行两代,预计现在中国可完成 14 nm 级产品制造,同期国外可完成 7 nm 级产品制造。

高端芯片产能严重不足,50% 的芯片依赖进口,同时中国的产能和需求之间结构失配,实际能够生产的产品,与市场需求不匹配,长期的代工模式导致设计能力和制造能力失配、核心技术缺失。

投资混乱、研发投入和人才不足等问题,导致中国集成电路产业目前总体还处于「核心技术受制于人、产品处于中低端」的状态,并且在很长的一段时间内无法根本改变。

再具体一点的,数字电路部分的芯片设计我们还可以赶上来,但是在模拟电路部分,我们的晶振、AD 采集卡等产品的精度还不够高,积累得还不够,核心技术还没有把握到手里。

8、国内缺少关键节点的关键技术

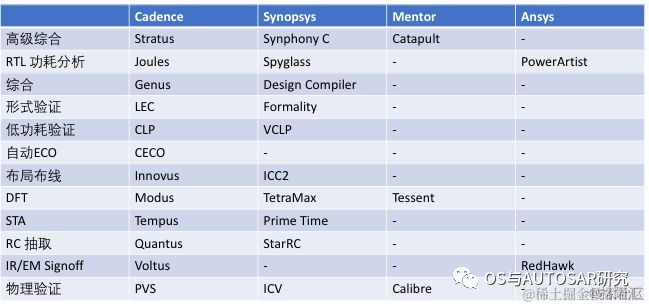

有三大主要关键技术或者说流程上有三大节点,「EDA、芯片设计、芯片制造」,最后才是封装测试。

这三个关键节点,缺一不可并且每一个环节都是被卡脖子的对象,我们先看一下三个领域里的公司分布。

EDA(Electronics Design Automation),是集成电路产业的基础,处于芯片产业链上游的子行业。它就相当于设计房子时所用到的 CAD 软件,有了 EDA 才能对芯片进行设计,举个例子,如果你想写字 EDA 就如同一支笔。

全球著名的 EDA 厂商有:

-

美国的新思科技(Synopsys);

-

美国的楷登电子科技(Cadence);

-

2016 年,被德国西门子收购的明导国际(Mentor Graphics)。

这三家公司是业内主流,并瓜分了 70% 以上的市场份额。

9、芯片设计

1. 华为海思

毫无疑问海思已经是芯片巨头。犹记得曾经在海思办公室呆了一段时间,印象深刻。

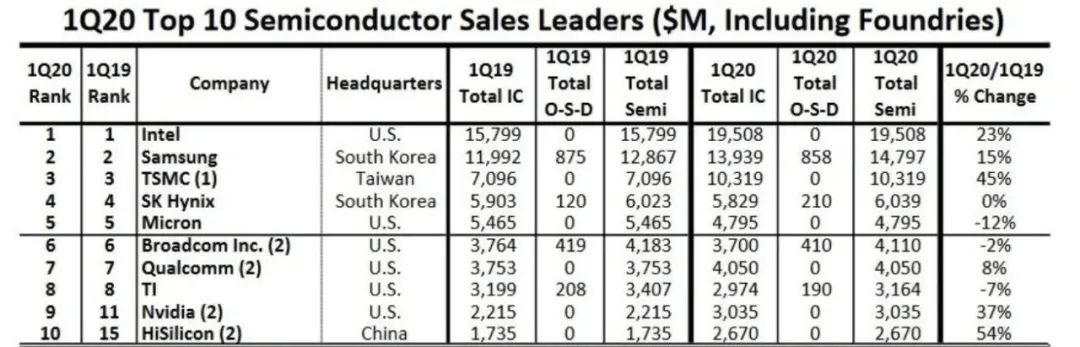

在 2020 年 Q1 的全球半导体 TOP10 榜单出现了两个「新面孔」,分别是华为海思(HiSilicon)和英伟达(Nvidia)。但是海思 90% 以上销售额都来自母公司华为的内部采购,应用到了自家的产品上。

而麒麟 9000 系列处理器和高通骁龙 865 比起来也不遑多让。当然,台积电无法为海思代工对其打击巨大。

2. 紫光展锐

紫光展锐是有展讯和锐迪科合并而来,隶属于紫光集团。

紫光展锐是我国集成电路设计产业的龙头企业,最近公司进军 5G 和 AI 领域,拥有超过超过 3700 个专利,每年出货芯片量超 15 亿颗。目前看起来展锐紧跟时代方向,但成为巨头还有很长的一段路要走。

3. 中兴微电子

中兴微电子在全球设有多个研发机构,研发人员超过 2000 人。经过十多年的发展,中兴微电子掌握了国际一流的 IC 设计与验证技术,拥有先进的 EDA 设计平台、COT 设计服务、开发流程和规范。

目前中兴微电子已申请的芯片专利超过 4000 件,其中 PCT 国际专利超过 1800 件,5G 芯片专利超过 200 件。

4. 联发科 MTK

联发科总部位于台湾,在上海北京苏州等多地有分公司,主要产品包含手机 CPU,无线通信以及多媒体等芯片。因为其 CPU 主打中低端市场,基本用在 2000 元以下的手机上。

5. 寒武纪

寒武纪是国内 AI 芯片第一股,颇受资本青睐,已经完成了 5 轮融资,海思和展锐也是其客户。

7. 平头哥

平头哥是阿里巴巴收购中天微后成立的半导体公司,2019 年 7 月 25 日,发布了第一个成果,基于 RISC-V 的处理器 IP 核玄铁 910,其可用于设计制造高性能端上芯片,应用于 5G、人工智能以及自动驾驶等领域。

其余行业内比较优秀的公司还有,华大半导体,豪威科技,比特大陆,澜起科技,长江存储,大唐微电子,海康威视等,都发展的不错。

10、芯片制造

1. 台积电

台积电就不多说了,妥妥的巨头。

2. SMIC

SMIC 第一代 14 nm FinFET 技术取得了突破性进展,并于 2019 年第四季度进入量产,代表了中国大陆自主研发集成电路的最先进水平。当然和第一梯队的台积电,三星和 Intel 有一定的差距,但是 14nm 也足够优秀了。

3. 三星

三星同样是世界级的芯片制造商,和台积电二者几乎垄断了高端芯片制造市场。

所以从以上分析来看,芯片的几大环节,EDA - 芯片设计 - 芯片制造,到封测与国际水平对比,差距最小的是封测,其次是设计。

差距最大的是芯片制造和 EDA,目前三星、台积电商用芯片 7nm 已经投入使用, 5 nm 正在路上。而 EDA 也基本被 Synopsys,Cadence,Mentor 三家垄断。

对于华为而言,只是拥有了设计能力,这也是被卡脖子的原因,简单理解就是,华为目前拥有世界顶级的芯片设计能力,但没法生产,就像建筑师拥有一套非常厉害的设计图纸,但没办法盖房子一样。

了解这些,可以帮助我们进一步了解,华为在自动驾驶系统推出后,为什么还会有巨大风险的原因。

国内芯片发展自主之路,任重而道远

从岁月里出发

探寻中國芯史

2022

TIME JOURNEY

岁月它静默不语

却将先辈足迹留存

有志青年何惧前途漫漫

投身于中国芯产业新征程

一起创造奋斗的精彩与回忆

响应时代呼唤

时机正好

时不我待

来源:资本市场那些事儿

了解半导体的历史、应用、未来

中国科学院半导体研究所 2018 年 10 月 08 日 12:31 北京

半导体发展历史

1 半导体是信息化的基础

上个世纪半导体大规模集成电路、半导体激光器、以及各种半导体器件的发明,对现代信息技术革命起了至关重要的作用,引发了一场新的全球性产业革命。

信息化是当今世界经济和社会发展的大趋势,信息化水平已成为衡量一个国家和地区现代化的重要标志。

进入 21 世纪,全世界都在加快信息化建设步伐。

源于信息技术革命的需要,半导体物理、材料、器件将有新的更快的发展。

集成电路的尺寸将越来越小,将出现新的量子效应器件;宽禁带半导体代表了一个新的方向,将在短波长激光器、白光发光管、高频大功率器件等方面有广阔的应用;纳米电子器件有可能作为下一代的半导体微电子和光电子器件;利用单电子、单光子和自旋器件作为量子调控,将在量子计算和量子通信的实用化中起关键作用。

2 晶体管的发明

1945 年二次大战结束时,美国贝尔实验室总裁巴克莱为了适应该室从战时转向和平时期的工作需要,决定成立固体物理组,由肖克莱负责半导体物理小组,成员有巴丁、布拉顿、吉布尼、穆尔等人。

肖克莱和巴丁是理论物理学家,布拉顿是实验物理学家,吉布尼是物理化学家,穆尔是电路学家,这种专业人才的搭配对于半导体物理研究和晶体管的发明是个黄金搭配,精干而高效。他们根据各自在 30 年代中期以后的经验和后来的考虑,从刚开始成立时,就把重点放在半导体材料硅和锗的研究上。

第二次世界大战期间,英国用雷达侦察到了德国的轰炸机。雷达的核心就是真空电子管,它能够将微弱电流放大。肖克莱早在 1939 年就准备制作能够将电流放大的固体器件,以便取代真空电子管。1947 年 12 月,巴丁和布拉顿制成了世界上第一个锗点接触型三极管,具有电流放大作用。

巴丁和布拉顿的结果在 1948 年 6 月发表。点接触晶体管的发明虽然揭开了晶体管大发展的序幕,但由于它的结构复杂,性能差,体积大和难以制造等缺点,没有得到工业界的推广和应用,在社会上引起的反响不够强烈。

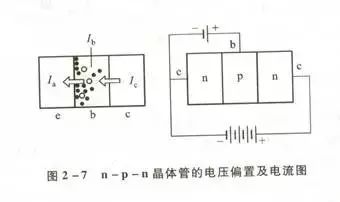

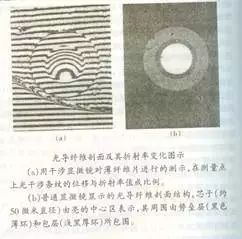

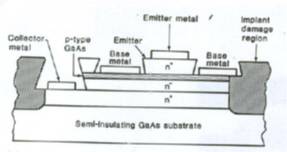

1948 年 1 月肖克莱在自己研究 p-n 结理论的基础上发明了另一种面结型晶体管,并于 1948 年 6 月取得了专利。面结型晶体管又称场效应晶体管,它是平面状的(见图 3),可以通过一些平面工艺(如扩散、掩膜等)进行大规模生产。因此只有在面结型晶体管发明以后,晶体管的优越性才很好地被人认识,逐渐取代了真空电子管。

由于巴丁、布拉顿和肖克莱在晶体管和结型晶体管发明上的贡献,在 1956 年获得了诺贝尔物理奖。作为半导体晶体管的第一个应用就是索尼公司的便携式收音机,风靡全球,赚了大钱。

3 集成电路的发明

晶体管收音机比电子管收音机小多了,可以随身携带。但它是由晶体管、电阻、电容、磁性天线焊在一块电路板上,相互之间由导线相连。体积还比较大,装配工艺复杂。

1958 年美国政府设立了晶体管电路小型化基金,以便适应美国为赶超前苏联发射的第一颗人造卫星的需要。那时,德克萨斯公司的基尔比承担了这一任务,试图制造将晶体管、电阻器和电容器等包装在一起的小型化电路。

1958 年 9 月基尔比制成了世界上第一个集成电路振荡器,这一切都记载在他当天的笔记中。基尔比发明的集成电路在 1959 年 2 月取得了专利权,名称为 “小型化电子电路”。

与此同时,美国加州菲切尔德(仙童)半导体公司的诺伊斯提出了用铝连接晶体管的想法。在基尔比发明集成电路 5 个月以后,即 1959 年 2 月,他采用霍尔尼提出的平面晶体管方法,在整个硅片上生成 SiO2 掩膜,应用光刻技术按模板刻成窗口和引线通路,通过窗口扩散杂质,构成基极、发射极和集电极,将金或铝蒸发,因而制成集成电路。1959 年 7 月诺伊斯的集成电路取得了专利权,名称为 “半导体器件与引线结构”。从此集成电路走上了大规模发展的新时期。

4 太阳能电池的发明

为了人造卫星的需要,1954 年皮尔森和富勒利用磷和硼的扩散技术制成了大面积的硅 p-n 结太阳能电池,光电转换效率达 6% 以上,超过了过去最好的太阳能转换效率的 15 倍。它的制作成本低廉,可以批量生产,因此很快得到了大规模的应用。

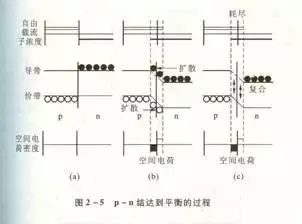

太阳能电池的工作原理是光生伏特效应。当光照射在半导体上时,在半导体中产生电子-空穴对。如果接通外电路,就会有电流通过,这就是光生伏特效应。

太阳能电池的商业应用开始于 1958 年,它被选用为美国第一个人造卫星 Vanguard I 的无线电发射机的电源。当前能源危机下,太阳能电池作为一种再生和无污染电源引起了人们极大的注意。

5 半导体激光器的发明

半导体发光管和激光器的工作原理和太阳能电池正好相反:太阳能电池是用光产生电,而发光管、激光器则用电产生光。用电流将电子和空穴分别引入半导体的导带和价带。电子和空穴复合,产生光子。

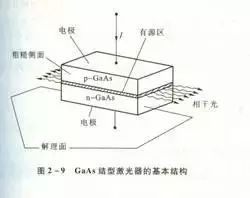

1962 年美国霍尔用 p-n 同质结制成了第一个半导体激光器。产生激光必须满足 3 个条件:粒子数的反转分布、谐振腔和电流超过一定阈值。

1963 年美国的克勒默和苏联的阿尔费罗夫各自独立地制成了异质结激光器,也就是在图 8 中,结区用一种禁带宽度小的材料,如 GaAs;两边的 p 区和 n 区用另一种禁带宽度大的材料,如 AlxGa1-xAs。这样,发光区域被限制在窄小结区中。

因此大大提高了发光效率,降低了激光器的阈值电流。1970 年苏联的约飞研究所和美国的贝尔实验室分别制成了室温下连续工作的双异质结激光器,从而使半导体激光器在光通信中得到了广泛的应用。

由于克勒默和阿尔费罗夫在发展半导体激光器方面的重要贡献,他们在 2000 年和集成电路发明者基尔比一起获得了诺贝尔物理奖。硅大规模集成电路和半导体激光器的发明使得世界进入了一个以微电子和光电子技术为基础的信息时代,大大促进了社会和经济的发展。

6 分子束外延技术的发明

制造双异质结激光器的一个关键技术是分子束外延。1968 年贝尔实验室的卓以和发现,在超高真空容器中通过精细控制束流的大小和时间,能够按照需要生长不同层数、不同种类的半导体材料,因而发明了分子束外延技术。分子束外延设备的示意图见图 11。

装置内部处于超高真空条件下(10-10torr),蒸发炉内装有原材料元素(如 Ga、As、Al 等)的源。前面是可以控制的挡板,打开挡板,将被蒸发的源原子直射至加热的衬底上进行外延生长。目前用这种技术已经能做到单原子层的生长。装置周围是一些检测仪器,用以监控生长过程。

半导体技术的应用

1 大规模集成电路和计算机

大规模集成电路为计算机、网络的发展打下了基础。按照摩尔定律,集成电路的集成度以每 18 个月翻一番的速度发展,最近它的线度已达到几十纳米(毫米、微米、纳米),每一个芯片上包含了上百亿个元件。

计算机科学已经发展到很高水平,无论是计算机的硬件还是软件都已十分成熟,每秒万亿次甚至更高速度的计算机(天河:2000 万亿次,世界第二)都已问世,这为各种高速运算、海量信息处理和转换提供了有力的工具。

自从 1943 年计算机诞生以来,由于集成电路的发明,计算机向着高运算速度、体积小型化方向飞速发展。目前世界主要发达国家和中国都已拥有百万亿次以上浮点运算的大型计算机。中国制造和拥有这种超级计算机的数量在世界上据第二位,仅次于美国。

这种超级计算机能用于分析蛋白质、开发新药等,在军事上可用于模拟核爆炸、解密码等。需要说明的是制造这种计算机所需的大规模集成电路中国还很落后,大部分还需进口。

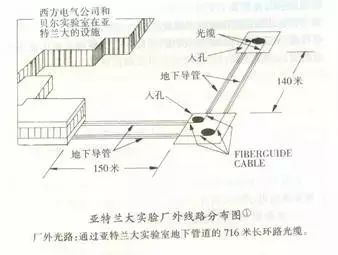

2 光通信技术

以前长距离通信靠长途电话或电报。因为通话数目少,价钱很贵。1966 年英国标准通信实验室的高锟(K. C. Kao)提出用无杂质高透明度的玻璃纤维传输激光信号。如果它的损耗能低到 20 分贝 / 公里,则就能实现长距离光通信。

1970 年纽约康宁玻璃厂的毛瑞尔(R. D. Maurer)等用 “淀积工艺” 将四氯化硅蒸气经过火焰水解,制成密实的玻璃管,再加热后通过模子拉制成细的玻璃纤维。低损耗的玻璃纤维的诞生是光通信技术的里程碑进展。

1976 年美国贝尔实验室在亚特兰大进行了第一次光通信实地实验,取得了很好的效果。光纤的平均功率损耗为 6 分贝 / 公里,无差错传输信息超过 10.9 公里,相当于通过光纤环路 17 周。1976 年 12 月贝尔实验室宣布:光波通信通过了它的首次检验,光波通信的可能性已经得到证明。从此宣告了光通信时代的来临,并预示着微电子时代向光电子时代的序幕正式揭开了。

今天,电信网络、计算机网络和有线电视网络已经成为一个国家重要基础设施,所有政治、经济、军事、科技活动以至人们日常生活时刻都离不开这三网。我国现有电话用户 8 亿 5 千万,其中移动手机用户 4 亿 8 千万,是世界上最大的电信网络。计算机上网用户已达 1.37 亿,有线电视用户达 1.3 亿,占世界三分之一。

将来的趋势是三网合一。现在的手机上网已经很普遍了,这方面美国的苹果公司走在了前面。

光有不同的颜色和波长。不是所有颜色的光都能在光纤中传播。

光纤的损耗分别在 1450-1550nm 和 1250-1350nm 处具有最低值和次低值,因此是光纤通信的 2 个主要窗口。为了让一根光纤能传播尽量多的信息通道,采用了波分复用的光通信系统,就是把这 2 个波段划分成很窄的波长,每个波长形成一定的通信容量。将不同波长的信号通过一根光纤传至对方,再经过解复用,由光检测器恢复原来以不同波长传递的电信号。由于光信号在传递中会逐步衰减,为了达到长距离传输的目的,每隔一定距离需要通过掺铒光纤放大器将其信号放大。

3 无线通信技术(手机)

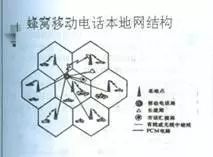

无线通信的基础是蜂窝式移动电话,它的早期制式是贝尔实验室在 1978 年推出的 “先进移动电话服务” 系统(AMPS)。该系统是将服务的区域分成许多小的六角形的地理区域(cell),就像蜂窝一样(见图 19)。每个小区内有低功率的无线电话发射器、接收器和一个控制系统,形成一个基站。

各服务区的基站通过光纤连接到中央交换实体(移动电话局),该实体装有电子交换系统。基站网络追踪移动终端的位置,当移动终端到达另一小区时能自动与邻近的基站重建联系,以便继续通话。由于小区内的无线通话功率低,只影响限定的范围,因而与别的小区的通信信号不会产生干扰。

第一个 AMPS 系统在 1979 年 7 月在芝加哥试验成功。1992 年 4 月,AT&T 公司微电子集团宣布制成新一代数字蜂窝电话的集成电路芯片,使该公司成为移动通信数字信号处理元件的领先供应者。这种数字信号处理器构成 DSP1600 系列,它使手机的体积和功率大大减小,在市场上大受用户欢迎。

除了手机通信以外,还有其它的无线通信手段(见图 20),包括:卫星传输高清晰度电视、卫星间通讯、多点视频通讯、无线局域网、交通工具之间的通讯、以及防撞雷达等。它们的工作频率在微波波段,从几个 GHz 到 100GHz。

各种无线通信及其工作频率。波段从微米到毫米波段,频率为 20-80 GHz。

无线通讯中最关键的器件是半导体高频振荡器件,目前有 2 种:高电子迁移率晶体管(HEMT)和异质结双极晶体管(HBT)。它们实际上就是典型的三极管,但由于利用分子束外延技术,n-p-n 每一层都可以做得很薄,缩小了电子运动的路径,具有高的截止频率 fT。目前这两种器件的截止频率都已达到了 100GHz 以上,满足了无线通信的需要。

npn 型双极晶体管截面图

4 半导体太阳电池 —— 太阳电池用硅材料

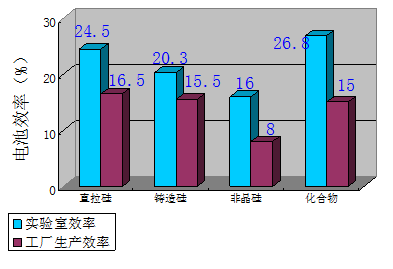

太阳电池用硅材料主要包括:直拉硅单晶、非晶硅、带状硅和薄膜多晶硅,这些材料在实验室和产业中制成的太阳电池的效率如图 22。

目前铸造多晶硅占太阳能电池材料的 47.54%,是最主要的太阳电池材料。到 2004 年,铸造多晶硅的市场份额已经超过 53%。直拉单晶硅占 35.17%,占据第二位,而非晶硅薄膜占 8.3%,位于第三位,而化合物半导体 CuInSe 和 CdTe 仅占 0.6%。

不同的半导体材料在实验室和产业中制成的太阳电池效率

5 半导体太阳电池 —— 多晶硅太阳电池

直到上世纪 90 年代,太阳能光伏工业还是主要建立在硅单晶的基础上。虽然硅单晶电池的成本在不断下降,但是和常规电力相比还是缺乏竞争力,因此,不断降低成本是光伏界追求的目标。

自上世纪 80 年代铸造多晶硅 的发明和应用以来,增长迅速。它以相对低成本、高效率的优势不断挤占单晶硅的市场,成为最有竞争力的太阳电池材料,到本世纪初,已占到 50%以上,已经成为最主要的太阳电池材料。

铸造多晶硅硅片的表面光学照片

到目前为止,铸造多晶硅的晶锭重量已经达到 300 kg,太阳电池片的尺寸达到 210×210 mm2。到本世纪初,多晶硅太阳电池的效率达到 20.3%。在实际生产中,铸造多晶硅太阳电池的最高效率也达到 17.7%左右,接近直拉硅单晶太阳电池的光电转换效率。

6 半导体太阳电池 —— 非晶硅薄膜太阳电池

今日非晶硅薄膜太阳电池已发展成为实用廉价的太阳电池品种之一,具有相当的工业规模。世界上非晶硅太阳电池的总组件生产能力达到每年 50MW 以上,组件及相关产品的销售额在 10 亿美元以上。应用范围小到手表、计算器电源,大到 10MW 级的独立电站,对太阳能光伏的发展起了重要的推动作用。

和晶体硅相比,非晶硅薄膜具有制备工艺简单、成本低和可大面积连续生产的优点。在太阳电池领域,其优点具体表现为:

(1)材料和制造工艺成本低。这是因为非晶硅薄膜太阳电池是制备在廉价的衬底材料上,如玻璃、不锈钢、塑料等,其价格低廉;而且,非晶硅薄膜仅有数千埃厚度,不足晶体硅电池厚度的百分之一,这也大大降低了硅原材料的成本;进一步而言,非晶硅制备是在低温进行,其沉积温度为 100℃~300℃,显然,规模生产的能耗小,可以大幅度降低成本。

(2)易于形成大规模生产能力。

(3)多品种和多用途。

(4)易实现柔性电池。非晶硅可以制备在柔性的衬底上,而且它的硅网结构力学性能特殊,因此,它可以制备成轻型、柔性太阳电池,易于和建筑集成,以及各种日常用品。

但是,和晶体硅相比,非晶硅太阳电池的效率相对较低,在实验室电池的稳定的最高转换效率只有 16%左右;在实际生产线上,效率不超过 10%;而且,非晶硅太阳电池的光电转化效率在太阳光的长期照射下有严重地衰减,到目前为止仍然没有根本解决。

另外,还有军事和卫星用的化合物太阳能叠层电池。

7 半导体白光照明

**➤1. 发展半导体白光照明意义

氮化镓发光管(LED)是一种高效长寿命的固态照明光源。白炽灯、荧光灯是目前面广量大的传统白光照明光源。白炽灯是一种热光(色温 2800K),含有大量的红外线,工作寿命短,发光效率低,而荧光灯则是一种冷光,高效率,但寿命短,有毒(含汞)。与传统的白炽灯和荧光灯相比,氮化镓发光管是一种具有体积小、重量轻、电压低、效率高、寿命长等特点的固态照明冷光源,因此是一种节能、绿色照明光源。

氮化镓 LED 目前已经用在许多场合:景观灯、交通灯、汽车尾灯、大屏幕显示灯。

能源是经济、社会可持续发展不可缺少的要素,节约能源、提高能效是可持续发展能源的重大战略。据统计,全世界 “照明” 耗能约占总电功率的 20%。由于 LED 高效发光,LED 白光照明可节省大量的发电煤和原油使用量,全球每年可减少 25 亿吨 CO2 排放量。

因此,氮化镓 LED 白光照明具有巨大的市场前景,将来成本和效率问题解决以后,可代替目前广泛使用的白炽灯和荧光灯,引发一次白光照明技术革命。国际上把半导体照明光源中期目标(5-10 年内)定为 > 100 lm/W,2020 年达到 200 lm/W 或 300 lm/W,这样就可替代传统照明。

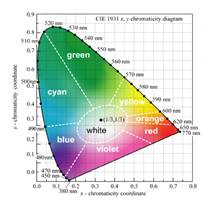

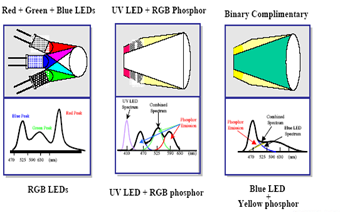

**➤2. 氮化镓 LED 白光照明的技术途径

众所周知,由红 (Red)、绿 (Green)、蓝(Blue)三基色可合成白光,如图 24 所示。该图为 1931 色度图,三角形中央虚线区为白光区。氮化镓 LED 一般只能发出一种颜色的光。白光照明也要通过 RGB 三基色的合成来实现。RGB 三基色可以直接靠 LED 发射三基色光,也可用 LED 去激发荧光物质,通过二次光转换获得三基色光或准三基色光。

所以,实现氮化镓 LED 白光照明有两种技术途径:一种是利用氮化镓发光二极管(LED)去激发荧光物质转换成白光,可称作为 “二次光转换白光技术”;另一种是利用 LED 直接发射白光,可称作为 “直接发射白光技术”。

**➤3. LED 白光照明技术发展方向

(1)研究发展近紫外、深紫外 LED 器件,实现高显色指数的 “固体白光荧光灯”。这种白光技术具有显色指数高(CRI>90)、转换效率高(外量子效率 43%),色彩重现性高等特点,是一种较理想的白光源。

(2)研究发展 III 族氮化物 LED 直接发射白光技术

(3)研究提高 LED 发光效率、光通量,发展功率型 LED 其器件

传统白炽灯发光效率为 16 lm/W,荧光灯发光效率为 85 lm/W,因此,Ⅲ 族氮化物 LED 白光照明光源要替代白炽灯和荧光灯,其发光效率至少要超过 100 lm/W,同时要降低成本。

8 光盘存储和激光测距、激光打印、激光仪器

光盘存储和激光测距、激光打印、激光仪器等是半导体激光器的另一重大应用领域。CD 盘(只读声盘)、DVD(数值可视盘)所用的激光器波长分别为 780nm 和 670nm、650nm,由激光器将信息 “写” 入光盘或者从光盘上 “读” 出声音或光信号。激光器的波长越短,光盘存储密度就越高。波长为 410nm 的 InGaN 激光器可以将光盘的存储量再提高一大步。波长为 670-630nm 的 InGaAlP 激光器已在许多场合取代了 He-Ne 激光器,在激光测距、激光打印、激光医疗仪器中得到了重要的应用。

9 半导体激光器的军事应用

波长为 808nm 的 AlGaAs 大功率激光器是大功率 YAG(掺钇铝石榴石)固体激光器的泵浦光源,代替了原来的氙气激光器,取消了庞大的电源和冷却系统,使固体激光器变得高效率、小体积、高性能、长寿命、低成本,适合于军事应用,例如激光雷达和核爆炸模拟、核聚变研究。水下光传播的窗口为 590nm,蓝绿光激光器的诞生为水下通信开了绿灯。火箭、飞机飞行过程中掌握方向的光纤陀螺中最关键的器件是半导体超辐射发光二极管。

10 环境保护

大自然中,水汽、甲烷、氨气、二氧化碳、一氧化碳、盐酸、溴酸、硫化氢等气体的灵敏吸收峰在 1.5-2.0mm 范围。InAsSb 或 GaInAsSb 应变量子阱激光器的波长可达 1.0-4.0mm 范围,近年来出现的量子级联激光器的波长可达 4.0-17mm。这些覆盖了红外-远红外范围的各类激光,构成了大气监控、监测的环保卫士。

半导体技术的未来发展

1 信息技术的革命

信息传输。信息量的爆炸式的增加,对信息通道的容量要求越来越大。在网上传递的不仅是文字、而且还有音乐、图像、电视信号等;不仅是有线,还需要无线;不仅是洲际、国际、城际,而且需要局域网。为此需要发展新的通信系统,如综合业务数字网络(ISDN)以及多媒体技术等。

信息处理,包括文本处理、知识处理、图像处理以及语言识别、图像识别、智能化处理等。人工智能就是通过计算机实现了某些人的智能。例如:理解和发出语言、识别图像、作数学证明、下棋、音乐作曲、进行专业鉴定、医学诊断等。计算机将把人们从一部分日常的脑力劳动中解放出来,并且通过应用 “思维工具” 把人们的智慧扩大到以前不可想象的程度。

2 更高的集成度

世界集成电路主流工艺将经过:2007 年的 65 纳米(集成电路线宽)、2010 年的 45 纳米、2013 年的 33 纳米、以及 2016 年的 22 纳米工业化生产的 4 个发展阶段。为此,就必须解决一系列的关键技术和专用设备,如:新型器件的研发(非传统 CMOS 器件、新型存储器、逻辑器件等),IC 设计、封装、和测试技术,新型光刻机、刻蚀机等配套设备等。

半导体器件的尺寸不能无限制地减小,如果器件尺寸小到电子的德波罗依波长(10 纳米),量子效应将会更加明显,这时需要设计建立在量子力学原理基础上的新型半导体器件。

3 半导体光电器件

半导体光电器件向更长和更短波长、更大功率、更高工作频率的方向发展

大功率激光器列阵分准连续 (QCW) 器件与连续 (CW) 器件,它们除了作固体激光器的泵浦源外,还可直接用作材料加工、医疗、仪器、敏感技术、印刷制版等,进入传统中由非半导体激光器主宰的市场,代替气体、固体激光器。AlGaN/GaN 异质结双极晶体管具有线性好、电流容量大、阈值电流均匀等优点,主要应用在线性度要求高、工作环境苛刻的大功率微波系统中,如军用雷达、通信等;还可应用于在苛刻环境下工作的智能机器人等系统中。

4 集成光学和集成光电子学

由集成在半导体薄膜上的激光器、调制器、波导、光栅、棱镜和其它无源光学元件构成的系统叫做集成光学系统。集成光学系统用光互连代替电互连,在计算机和通信系统中具有通带宽、信息量大、损耗小、速度快、能并行处理、抗电磁干扰等优点。硅材料的成本低廉、工艺成熟,在微电子器件中得到广泛应用。但是由于它是间接带隙材料,不能作发光器件。目前科学家们正在解决光源的问题,以便在硅材料上做到光电集成。

5 半导体超晶格和量子线、量子点器件

半导体超晶格、量子线、量子点是低维结构,它们具有一些特殊的物理性质,如量子限制效应和电子运动的二维或一维特性,可以制成一些性能优异的器件,如:激光器、高电子迁移率器件、光双稳器件、共振隧穿器件等。当器件的尺寸、维度进一步减小,使得电子运动的平均自由程大于器件的尺寸时,电子在运动过程中将不受杂质、晶格振动等的散射,而作一种相干波运动。

利用这些特点预计可制造出超高速、超低电能的电子器件。例如量子点单电子晶体管将使动态随机存储器(DRAM)的功耗大大降低。

6 半导体量子信息器件

目前的工艺已经能在半导体量子点上产生和探测单个光子,使得半导体量子点成为实现量子信息处理(量子计算、量子通信)最有希望的固体器件。量子信息科学技术的迅速发展,为精密测量、量子计算和保密通讯等领域都提供了全新的革命性的理论和实验方法。量子信息最关键的是利用光子的相干性。

光子作为量子理论中最基本的量子化实体,能够很容易地实现收集、传递、复制、存储和处理信息的全过程,具有作为量子通讯、量子计算载体的独特的先天优势。因此基于光子过程的量子信息处理器件是各种量子信息工程的基础,它的基本原理研究和制备必将为计算科学和通讯能力带来飞越式的发展。

7 自旋电子器件

目前微电子器件是应用载流子电荷携带信息。如果一种材料能同时利用载流子的电荷和自旋属性作为信息的载体,将可以制造出具有非挥发、低功耗、高速和高集成度的优点的器件,甚至有可能引起电子信息科学重大的变革。掺磁性离子的稀磁半导体及自旋电子学(Spintronics)即应此要求而生。

实验发现,半导体中自旋相干时间已经达到 ns 量级,远远超过电荷的相干时间,预示着自旋电子学在未来量子计算和量子通信中的重要应用前景。实现自旋为基的量子计算机的主要困难是精确控制和保持自旋相干,因此如何产生自旋相干电子态,以及减小自旋退相干有许多物理问题需要研究和解决。

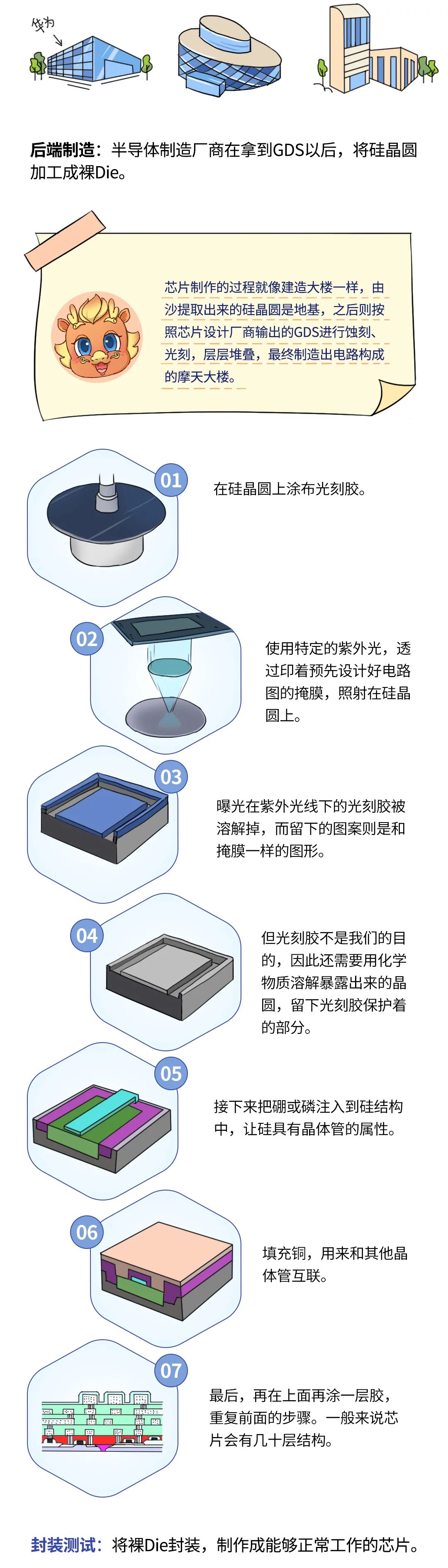

难住中国的芯片,是怎么从沙子中一步步炼成的?

新材料在线 2022 年 01 月 01 日 08:30

Source:以上图片来自新材料在线 ®

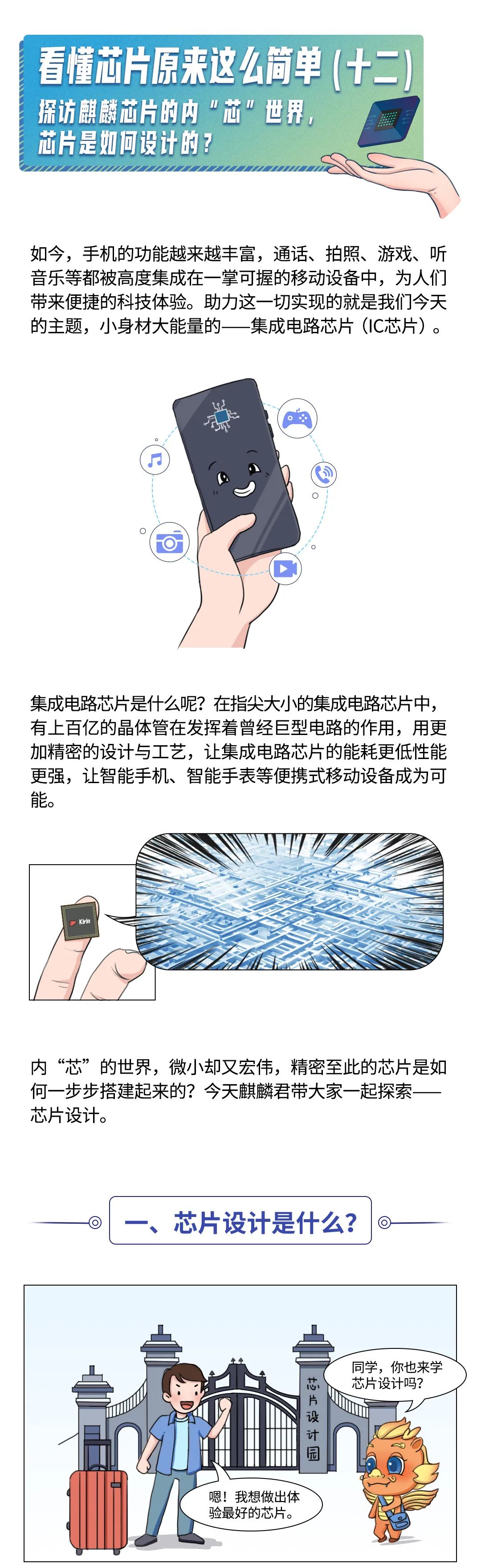

芯片设计制造全流程,带你探访芯片的内 “芯” 世界

爱科普的 华为麒麟 2021 年 11 月 24 日 17:23

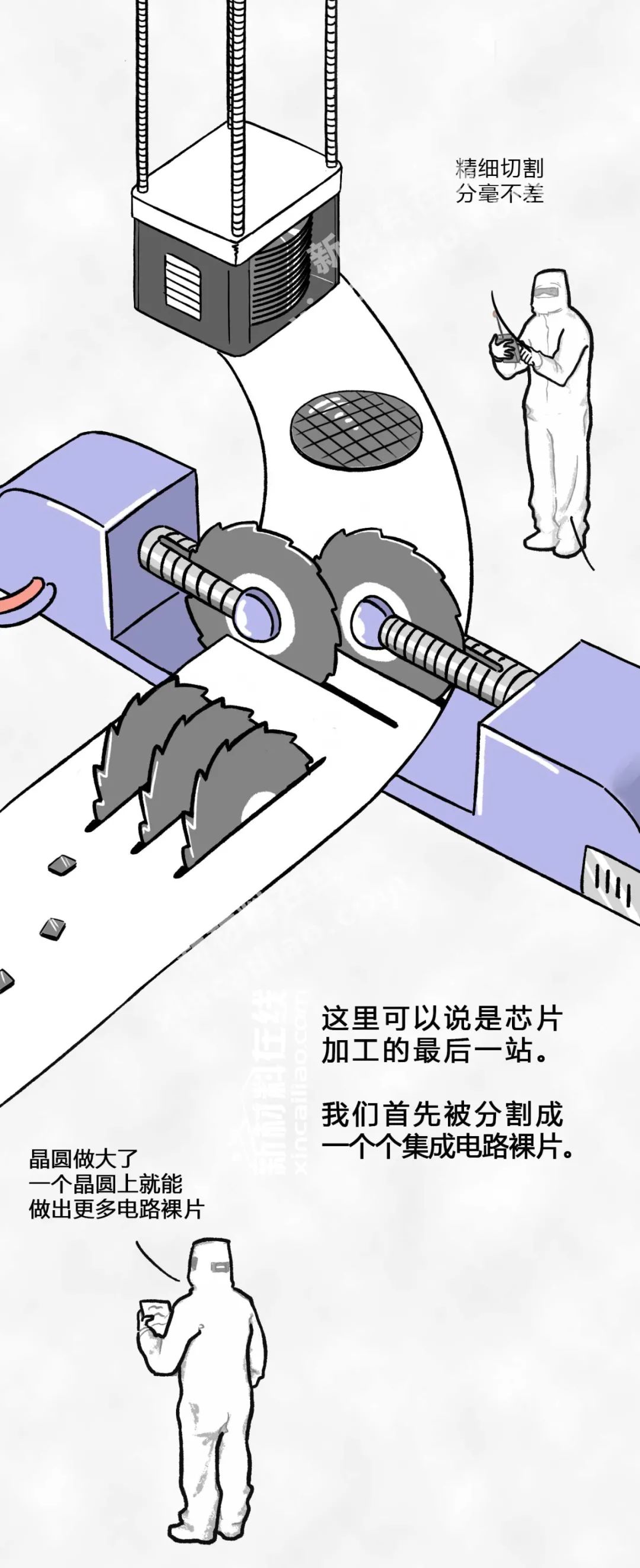

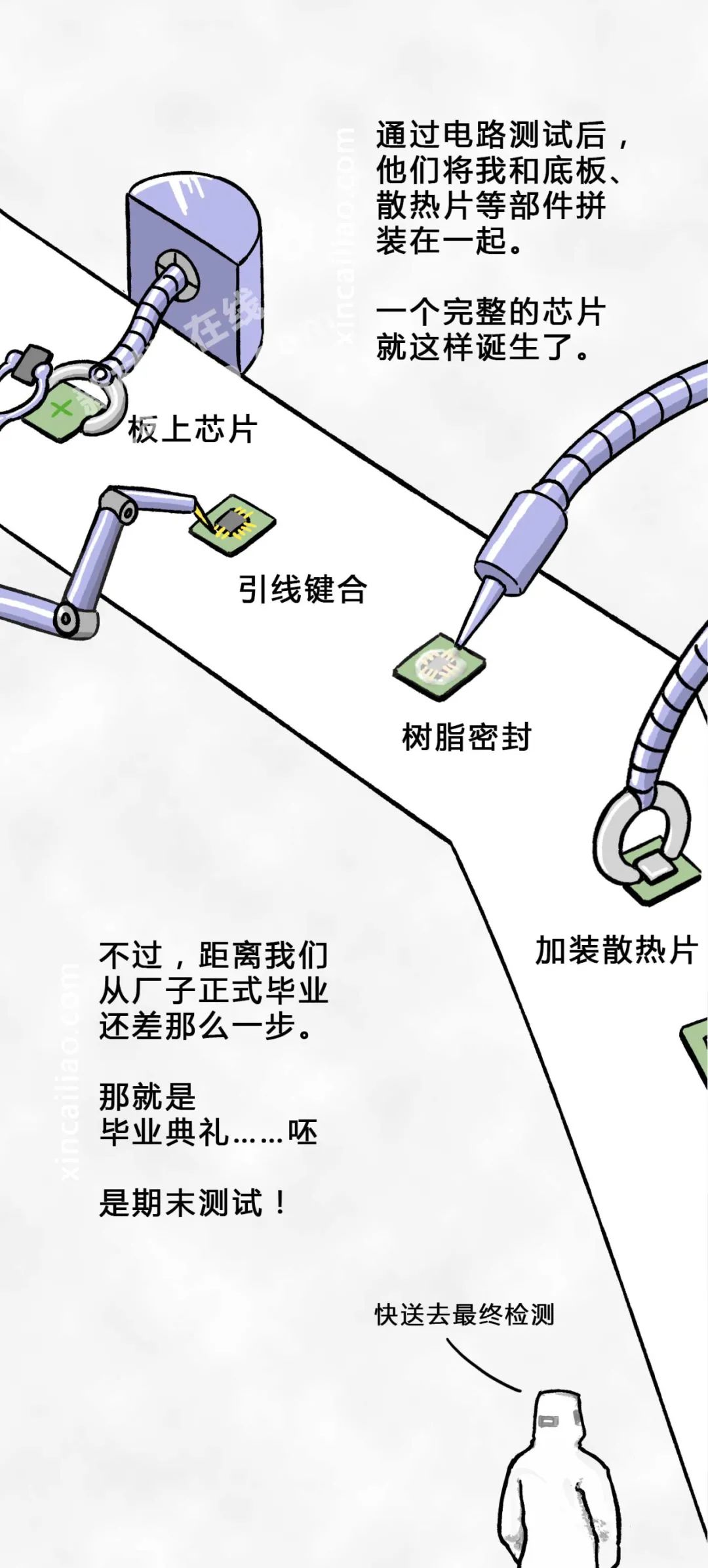

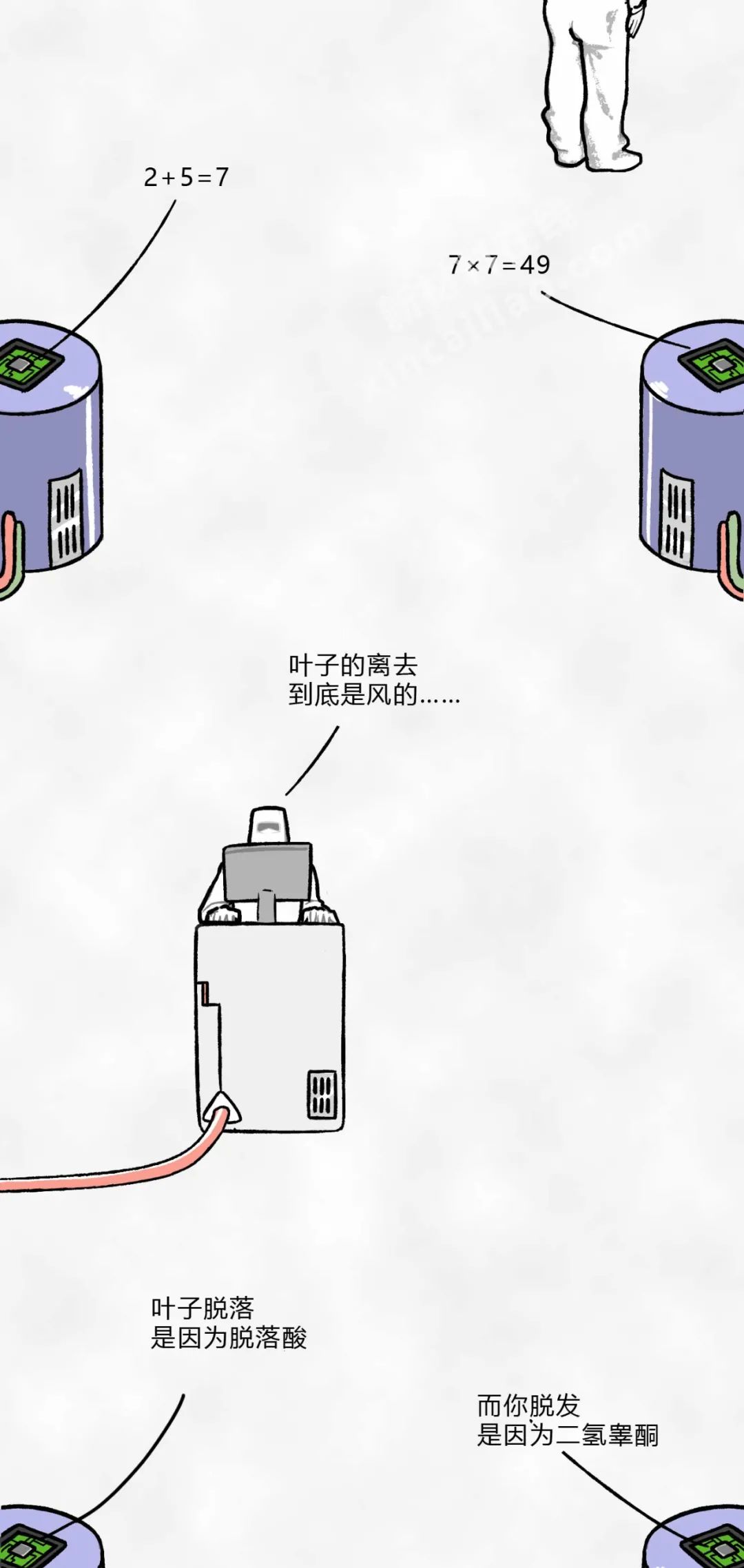

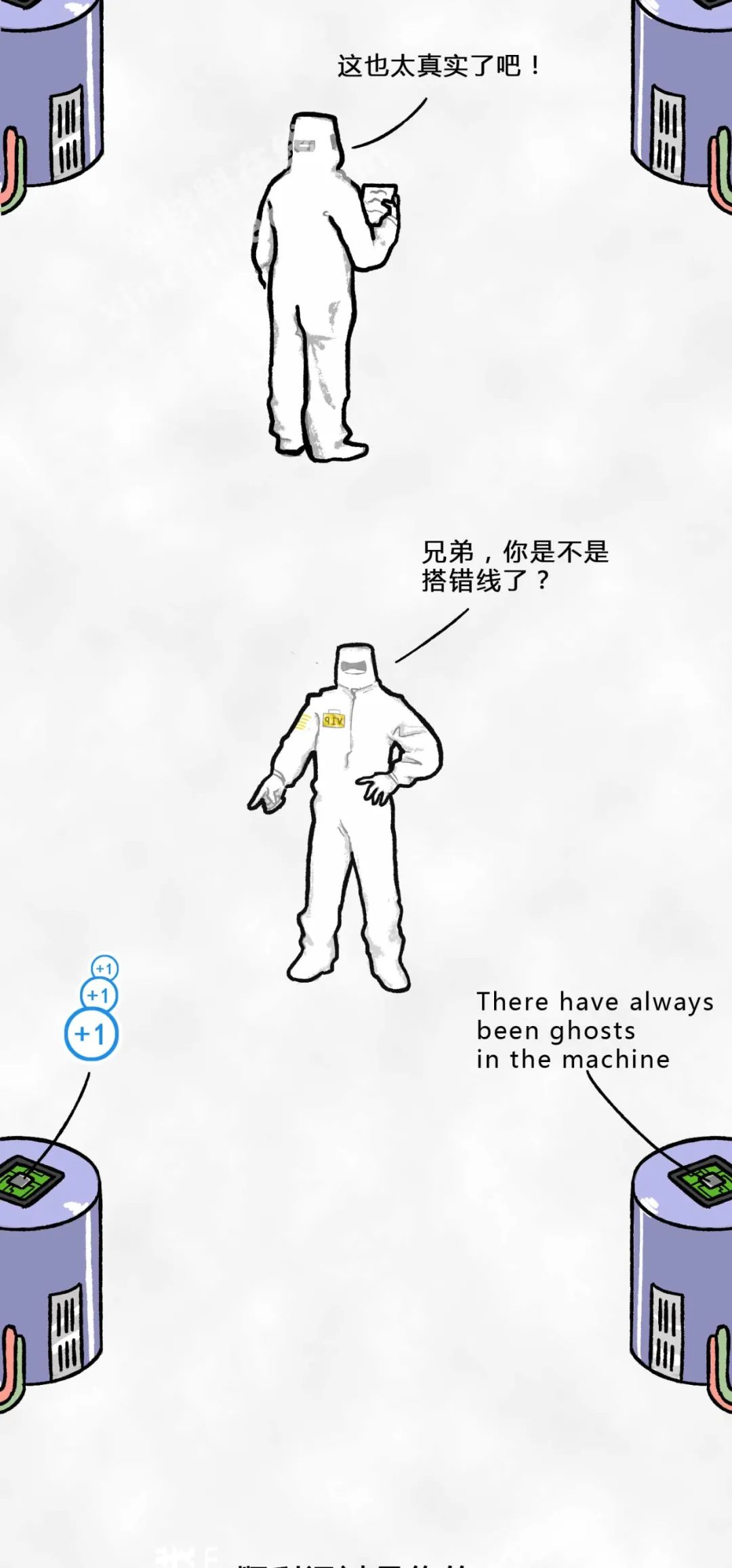

由沙成芯,方寸之间。

指尖大小的芯片,内含 153 亿个晶体管。

如此复杂的工艺是如何实现的?

漫解麒麟芯片的内 “芯” 世界!

拿好小本本,麒麟芯片的设计之旅开始喽👇

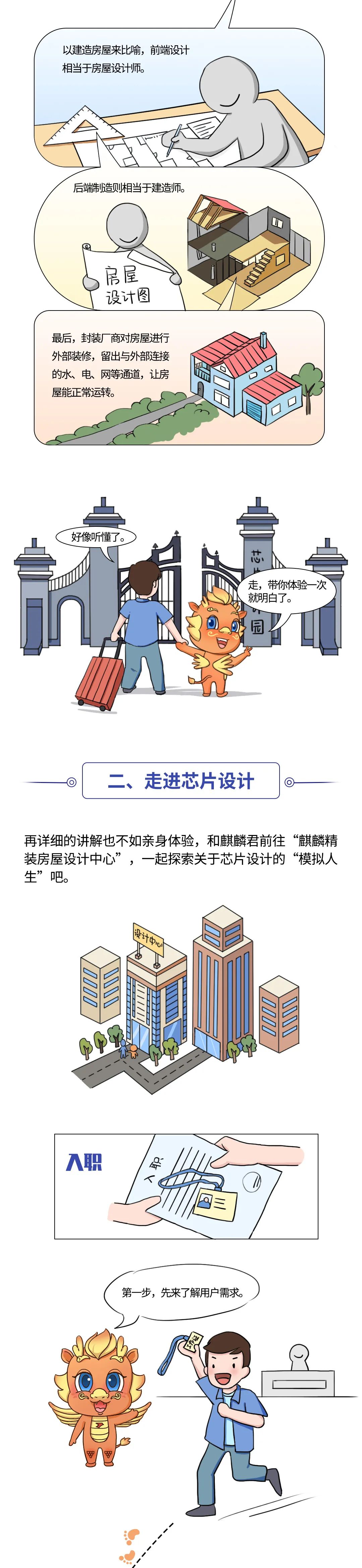

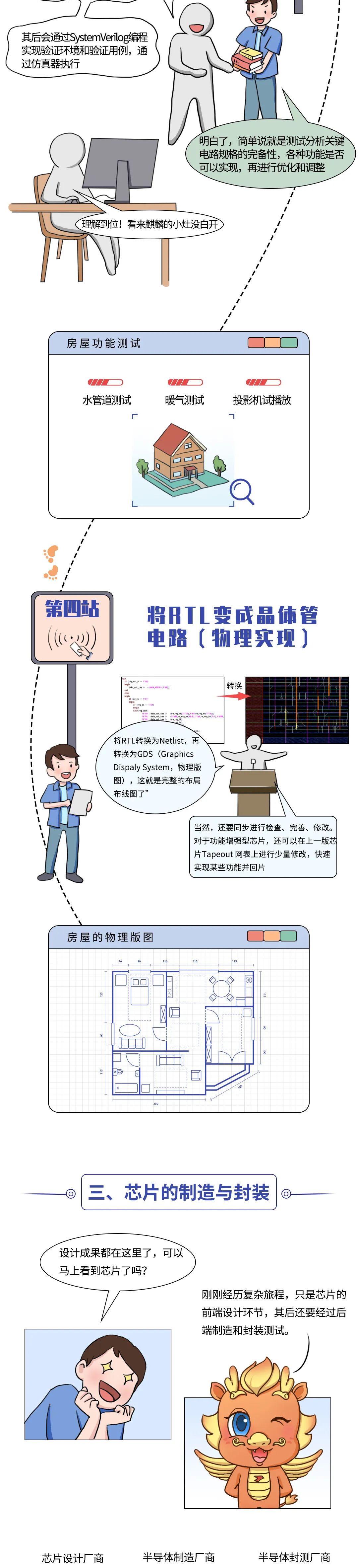

芯片 - 设计流程入门

*原创 thatway 那路谈 OS 与 SoC 嵌入式软件 2023 年 11 月 01 日 07:16 北京 *

芯片近些年来一直是风口,几乎所有有实力的上市公司都要蹭下这个热度:自研芯片。这也诞生了很多工作岗位,相对于硬件工程师,软件开发工程师能做的事情有限,但是也是非常重要的,而且跟着风口喝口汤也是可以的。整体来说:需求、架构、验证是需要软件参与的,本文结合自己的部分经验,从最基本的芯片设计流程进行介绍,其中会涉及一些可能你经常听到的卡脖子技术。

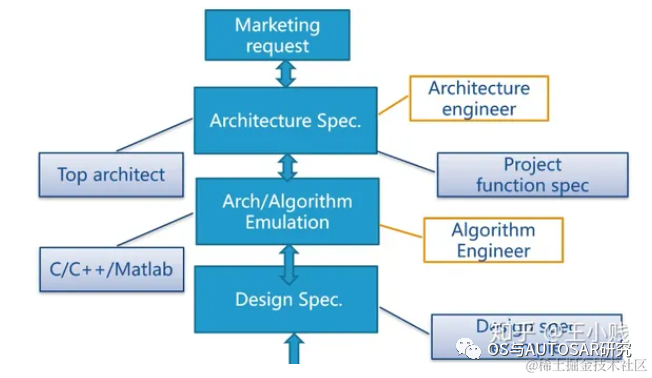

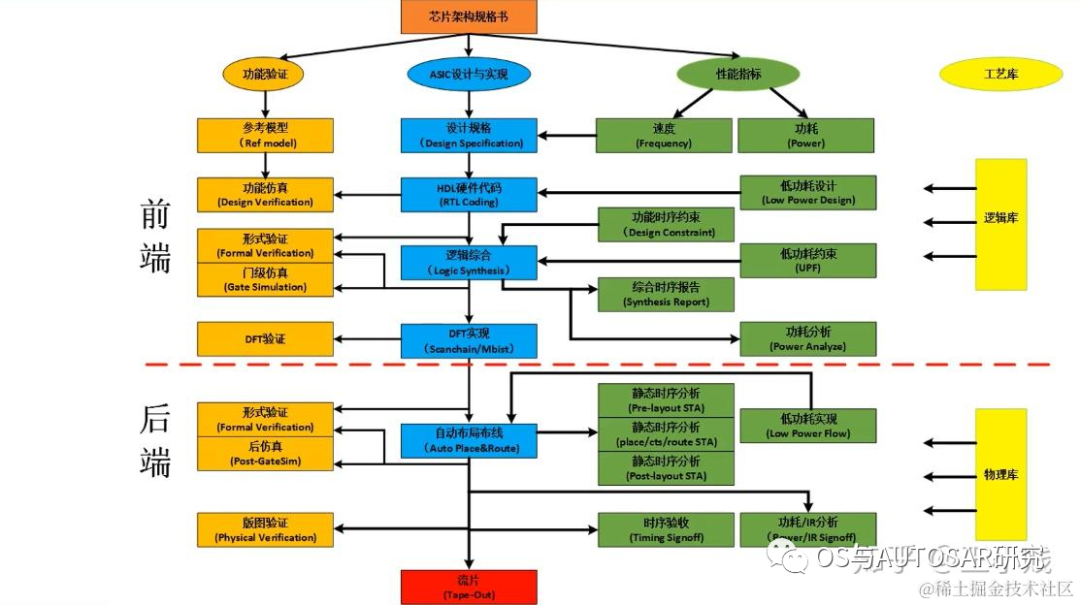

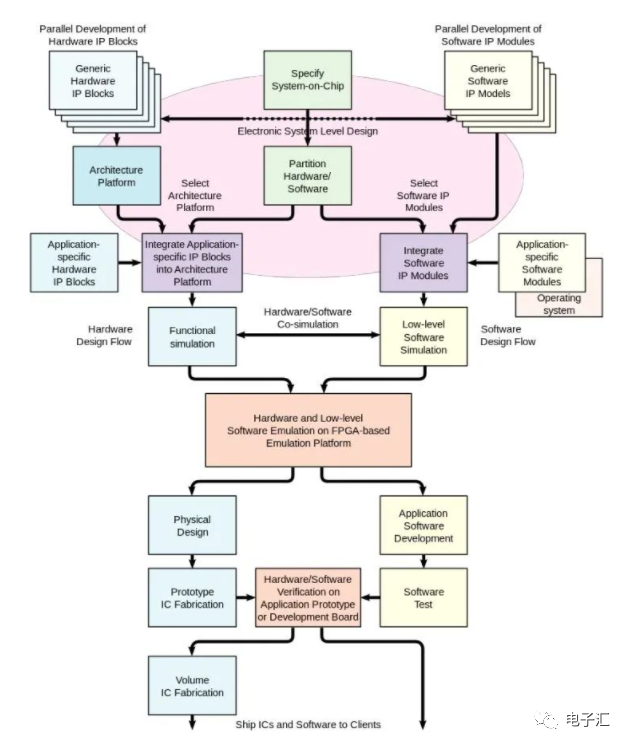

芯片设计的四个步骤,如上图,我们只关注需求和设计,制造和封装不是我们软件工程师能左右的。

1. 市场需求

要做一个芯片,首先得有需求,也就是应用场景,有市场去买单。当前科技时代,电子技术在各方面都有应用,可以说有电路板的地方就有芯片需求。例如手机、电脑、智能家具,我们的衣食住行用等方方面面。

有了需求,就可以根据需求梳理出来我们硬件上需要那些模块功能和性能指标,以及软硬件上要用的技术。这些需要软硬件的架构师进行设计,最终形成Spec。

Spec 会确定所有的功能和要求,之后才可以进行芯片设计。

1.1 关于 EDA 模拟软件

-

软件在做架构设计的时候,有时候需要进行一些验证,看软件是否支持,可以使用qemu模拟运行的方式看应用能支持不。

-

软硬件在做架构设计的时候,可以使用很多 IC 厂商提供的 IP 集成工具来模拟 SoC,就是用纯软件的方式把 SoC 上的各个 IP 都添加模拟出来,例如VDK(Virtualizer Development Kit) 工具。

这里说的 VDK 工具,其实就是一种电子设计自动化EDA(Electronics Design Automation)工具,也就是我们俗称的 EDA 工具。这是我们卡脖子的技术之一,很复杂,而在芯片设计中非常的重要,贯穿设计、验证和制造,特别是验证可以大力减少出错成本和缩短研发周期。可谓 “没有金刚钻,不揽瓷器活”。详细可以参考:浅谈 EDA 验证工具,芯片开发到底有多难?

VDK 与 qemu 的区别就是 qemu 支持的芯片型号有限,自己添加很麻烦,要修改 qemu 的源码。而在 VDK 图形界面上点一点就可以添加一个 IP,而且很多 IP 是不出名的,厂商私有的不会广泛支持,就需要自己加。所以 IP 厂商基本会有自己的集成验证工具供客户使用。

芯片开发的周期很漫长,在最开始需求阶段,一些应用上的软件也许就具备开发条件了,例如在 qemu 上进行 app 应用的开发,一些依赖于 SoC 上 IP 的应用,可以使用 VDK 做一些数据流的通路开发,并不支持具体的业务,这样后续拿到真正芯片后就可以省略很多一部分研发任务,并且可以提前验证软件技术方案的可行性。

如果软件技术方案不可行需要修改 SoC 硬件也可以及早的修改。因为芯片研发越到后期修改的成本越大,如果流片了还需要修改,那就快 game over 了,巨额资金打水漂。所以宁愿先投入研发人员去慢慢磨,也不愿意在硬件上去试错,人可没芯片生产值钱。

1.2 关于架构师

数字集成电路设计实现流程是个相当漫长的过程,拿手机基带芯片为例,对于 3G, 4G, 5G, 工程师最初见到的是无数页的协议文档。

-

架构师要根据协议来确定:协议的哪些部分可以用软件实现,哪些部分需要用硬件实现;

-

算法工程师要深入研读协议的每一部分,并选定实现所用算法;

-

芯片设计工程师,需要将算法工程师选定的算法,描述成 RTL;

-

芯片验证工程师,需要根据算法工程师选定的算法设计测试向量,对 RTL 做功能、效能验证;

-

数字实现工程师,需要根据算法工程师和设计工程师设定的目标 PPA 将 RTL 揉搓成 GDS;

-

芯片生产由于太过复杂,完全交由代工厂完成,封装亦是;

-

对于测试,大部分公司都是租借第三方测试基台由自己的测试工程师完成,只有少部分土豪公司才会有自己的测试基台。

架构师是芯片灵魂的缔造者,是食物链的最顶端,是牛逼闪闪的存在。

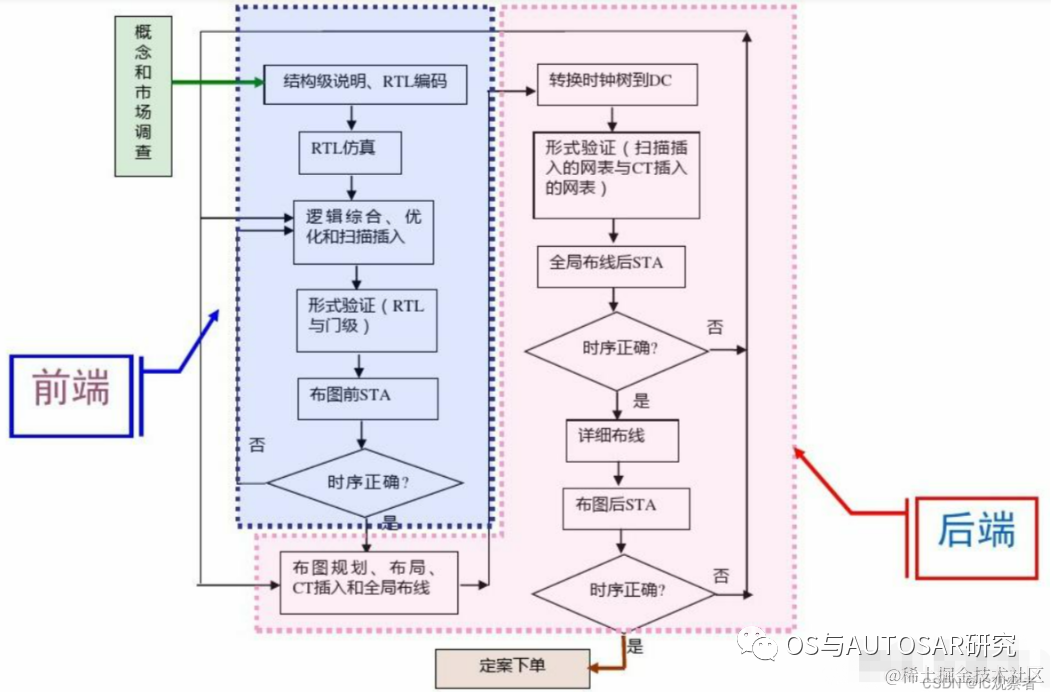

2. 芯片设计概述

芯片设计分为两部分,前端(逻辑设计)和后端(物理设计)。

这其中很多流程看似高大上,但是有 IP 供应商提供的工具以后,其实就是界面上点点的事情。

芯片设计中涉及的工具繁多,基本都是老外的,这需要国内芯片公司的崛起,有自己的很多 IP 后才可以投入到这些工具的研发中去。

有一个说法就是老外掌握一项新技术,首先就是加密做界面化,不提供源码然后商业卖钱。而这个周期要延迟一两年到市场上,而中国则直接推给自己的客户,客户有能力抄的就抄跑了,大家都不太注重商业保密,可能技术比较 low不用藏着掖着,大家都是抄的。。。这就是中国速度。

3. 芯片前端设计

-

RTL 设计

-

验证

-

静态时序分析

-

覆盖率

-

ASIC 逻辑综合

3.1 RTL 设计

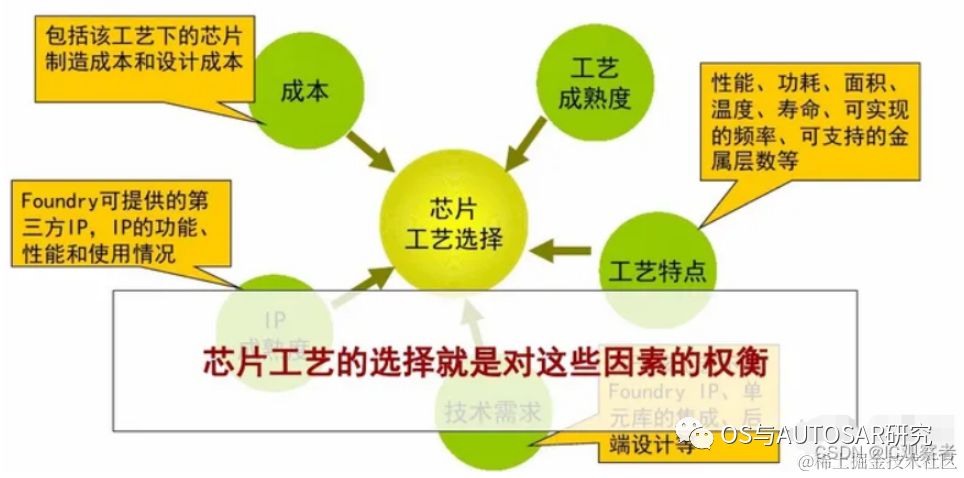

首先要确定芯片的工艺,如下图:

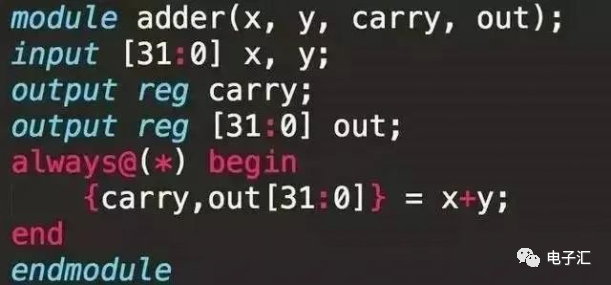

RTL(register transfer level) 设计:利用硬件描述语言,如 VHDL,Verilog,System Verilog, 对电路以寄存器之间的传输为基础进行描述。

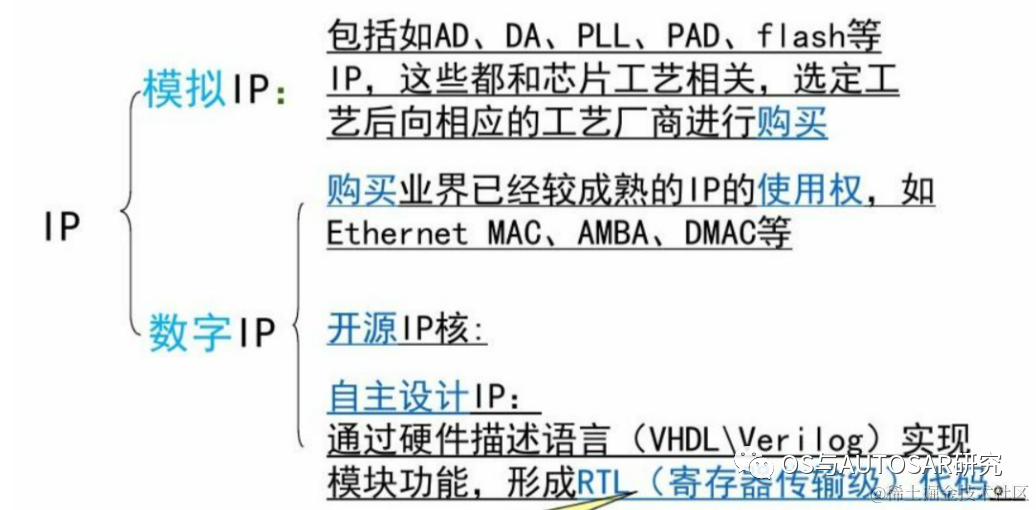

RTL 使用代码编写,来实现功能模块,就是一个个 IP。这些 IP 分为数字 IP 和模拟 IP:

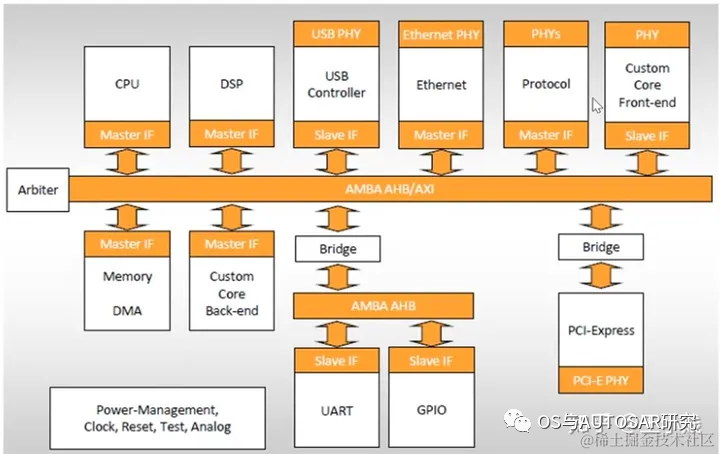

SOC 芯片最终由 SOC integration 工程师把各个 IP 集成到一起。

上图中我们可以看到一个典型的 SoC有那些 IP,例如 CPU,DSP,USB 外设,memory 等。

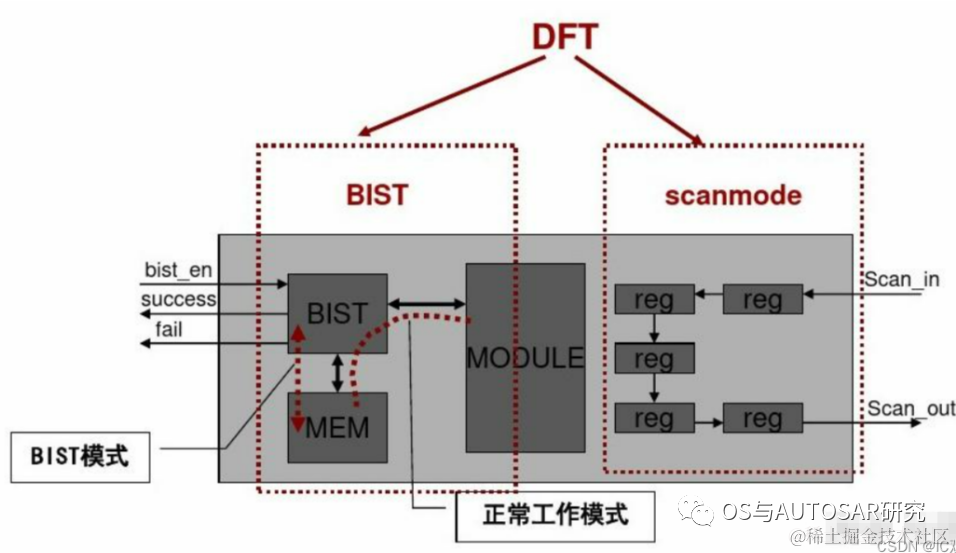

对于 RTL 还需要进行支持 BIST(自测试),设计的时候也需要做可测性设计 DFT(Design For Test)

除了对功能测试,还需要对代码进行自动检查:通过 lint, Spyglass 等工具,针对电路进行设计规则检查,包括代码编写风格,DFT,命名规则和电路综合相关规则等检查。

3.2 验证

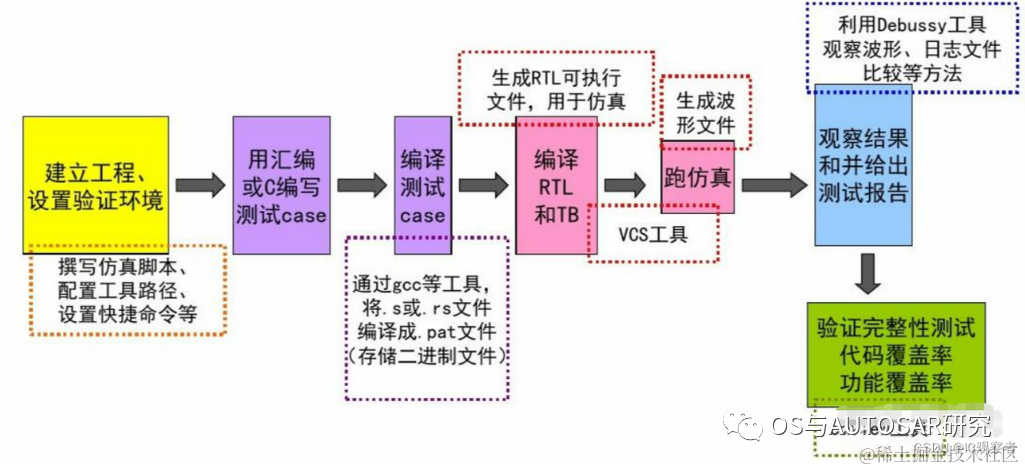

验证是保证芯片功能正确性和完整性最重要的一环。验证的工作量也是占整个芯片开发周期的 50%-70%,相应的,验证工程师与设计工程师的数量大概在 2-3:1。从验证的层次可以分位:模块级验证,子系统级验证和系统级验证。从验证的途径可以分为:模拟(simulation),仿真和形式验证(formality check)。

这里又出现了芯片验证,这里软件开发人员又来活了,之前在 qemu、VDK 上模拟的程序现在可以在RTL 上模拟了,这里是越来越贴近硬件了。在多平台验证虽然很繁琐,就像验证完一个玩具系统,然后继续下一个,好似没有用,但是每一次都是在进步。

这里需要注意的一点就是在各个验证平台下的代码复用问题,大的模块差异可以通过编译时区分,小的差异可以通过运行时读取标志寄存器来在代码里面走不同分支或加载不同的配置文件区分,这里需要把握一个度。

一点经验:多用配置文件例如 xml、dts、config 文件,不用宏,直接 debug 版本适应所有验证平台,编译时借助编译工具脚本自动区分。

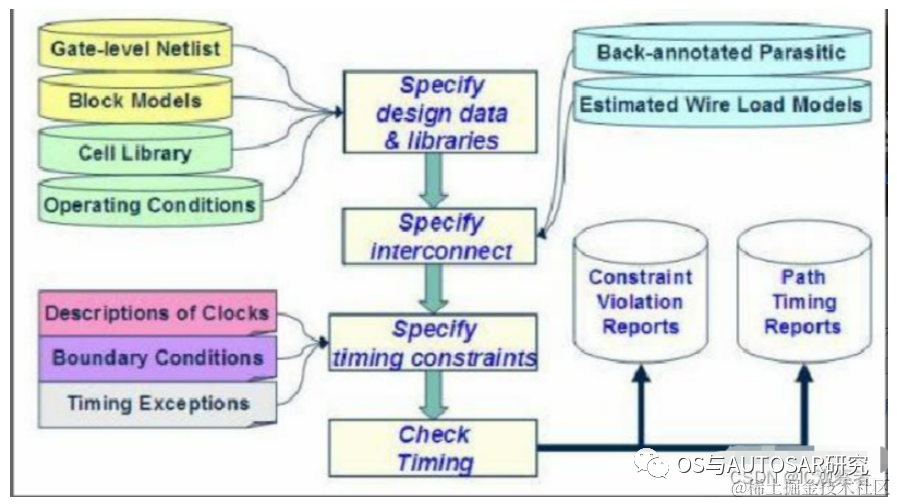

3.3 静态时序分析(STA)

静态时序分析是套用特定的时序模型(timing model), 针对特定电路,分析其是否违反 designer 给定的时序限制(timing constraint)。

目前主流的 STA 工具是 synopsys 的 Prime Time。

静态时序分析的作用:

- 确定芯片最高工作频率

通过时序分析可以控制工程的综合、映射、布局布线等环节,减少延迟,从而尽可能提高工作频率。

- 检查时序约束是否满足

可以通过时序分析来查看目标模块是否满足约束,如不满足,可以定位到不满足约束的部分,并给出具体原因,进一步修改程序直至满足要求。

- 分析时钟质量

时钟存在抖动、偏移、占空比失真等不可避免的缺陷。通过时序分析可以验证其对目标模块的影响。

3.4 覆盖率

覆盖率作为一种判断验证充分性的手段,已成为验证工作的主导。从目标上,可以把覆盖率分为两类:代码覆盖率 作用:检查代码是否冗余,设计要点是否遍历完全。检查对象:RTL 代码 功能覆盖率 作用:检查功能是否遍历 检查对象:自定义的 container 在设计完成时,要进行代码覆盖率充分性的 sign-off, 对于覆盖率未达到 100% 的情况,要给出合理的解释,保证不影响芯片的工能。

3.5 ASIC 综合

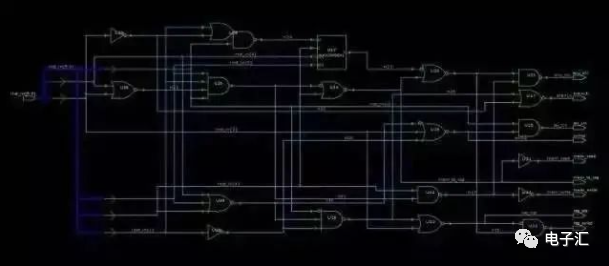

逻辑综合的结果就是把设计实现的 RTL 代码翻译成门级网表(netlist)的过程。

在做综合时要设定约束条件,如电路面积、时序要求等目标参数。

工具:synopsys 的 Design compiler, 综合后把网表交给后端。

至此我们前端的工作就结束啦!

4. 后端设计

1. 逻辑综合

2. 形式验证

3. 物理实现

4. 时钟树综合-CTS

5. 寄生参数提取

6. 版图物理验证

4.1 逻辑综合

同 3.5 中前端的逻辑综合

4.2 形式验证

1)验证芯片功能的一致性

2)不验证电路本身的正确性

3)每次电路改变后都需验证

形式验证的意义在于保障芯片设计的一致性,一般在逻辑综合,布局布线完成后必须做。工具:synopsys Formality

4.3 物理实现

物理实现可以分为三个部分:

-

布局规划 floor plan

-

布局 place

-

布线 route

物理实现可以分为三个部分:

-

布局规划 floor plan

-

布局 place

-

布线 route

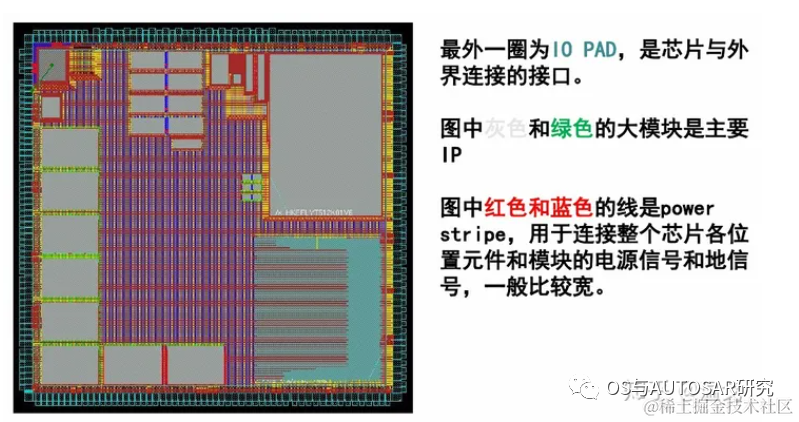

布图规划 floor plan

布图规划是整个后端流程中作重要的一步,但也是弹性最大的一步。因为没有标准的最佳方案,但又有很多细节需要考量。

布局布线的目标:优化芯片的面积,时序收敛,稳定,方便走线。

工具:IC compiler,Encounter

布图规划完成效果图:

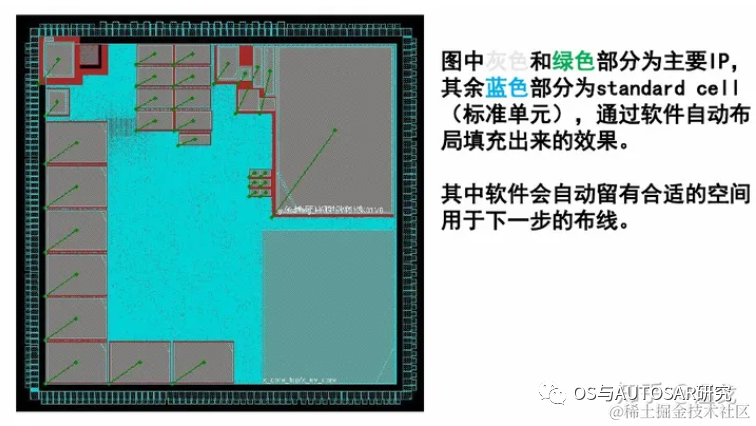

布局

布局即摆放标准单元,I/O pad,宏单元来实现个电路逻辑。

布局目标:利用率越高越好,总线长越短越好,时序越快越好。

但利用率越高,布线就越困难;总线长越长,时序就越慢。因此要做到以上三个参数的最佳平衡。

布局完成效果图:

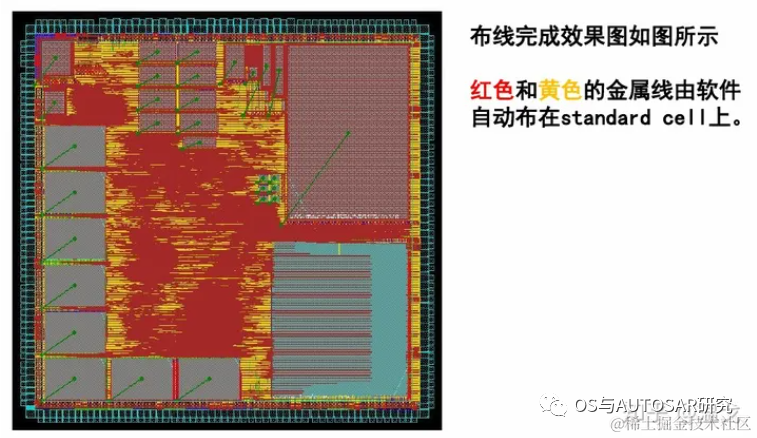

布线

布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束条件下,根据电路的连接关系,将各单元和 I/O pad 用互连线连接起来。

4.4 时钟树综合 ——CTS

Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。

由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。

4.5 寄生参数提取

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。

工具 Synopsys 的 Star-RCXT

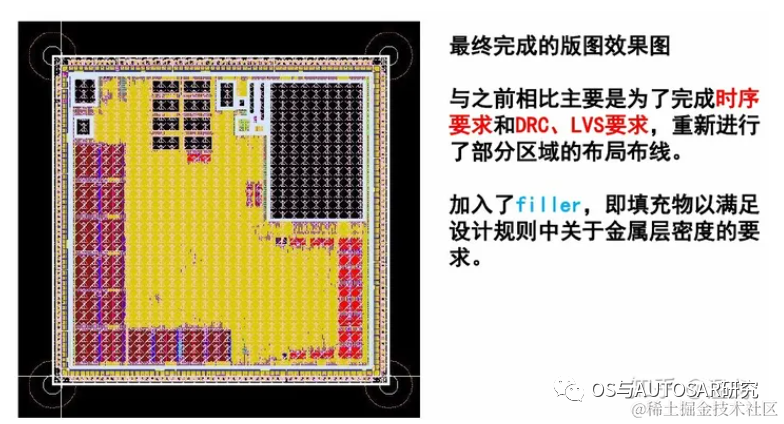

4.6 版图物理验证

这一环节是对完成布线的物理版图进行功能和时序上的验证,大概包含以下方面:

LVS(Layout Vs Schematic)验证:简单说,就是版图与逻辑综合后的门级电路图的对比验证;

DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求;

ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气规则违例;

实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的 DFM(可制造性设计)问题等。

物理版图以 GDSII 的文件格式交给芯片代工厂(称为 Foundry)在晶圆硅片上做出实际的电路。

最后进行封装和测试,就得到了我们实际看见的芯片。

芯片设计到底难在哪里?

电子汇 2024 年 09 月 05 日 22:45 广东

芯片作为现代电子产品的核心部件,一直充当着 “大脑” 的位置,其技术含量和资金极度密集,生产线动辄数十亿上百亿美金。

芯片制造的完整过程包括:芯片设计、晶圆制造、封装、测试等几个主要环节,其中每个环节都是技术和科技的体现。

对于芯片来说设计和工艺同样复杂,八十年代 EDA 技术诞生 —— 芯片自动化设计,使得芯片设计以及超大规模集成电路的难度大为降低,工程师只需将芯片的功能用芯片设计语言描述并输入电脑,再由 EDA 工具软件将语言编译成逻辑电路,然后再进行调试即可,正如编辑文档需要微软的 office,图片编辑需要 photoshop 一样,芯片开发者利用 EDA 软件平台来进行电路设计、性能分析到生成芯片电路版图。现在的一块芯片有上百亿个晶体管,不依靠 EDA 工具,高端芯片设计根本无从下手。你细品,这么浩瀚的工程怎么能靠手动完成呢?

重点是尽管有了 EDA 也并不代表芯片设计这件事很容易,芯片设计仍然是一个集高精尖于一体的复杂系统工程。

不管是 IDM 还是 fabless,共同的特点是以芯片设计为产业的核心。举个栗子,2018 年 AMD 的处理器改由台积电代工,制程为 7nm,英特尔的处理器制程还是 14nm,但性能照样压制了 AMD,说明芯片设计也是非常关键的鸭。

设计一款芯片,开发者先要明确需求,确定芯片 “规范”,定义诸如指令集、功能、输入输出管脚、性能与功耗等关键信息,将电路划分成多个小模块,清晰地描述出对每个模块的要求。

然后由 “前端” 开发者根据每个模块功能设计出 “电路”,运用计算机语言建立模型并验证其功能准确无误。“后端” 开发者则要根据电路设计出 “版图”,将数以亿计的电路按其连接关系,有规律地翻印到一个硅片上。

至此,芯片设计才算完成。如此复杂的设计,不能有任何缺陷,否则无法修补,必须从头再来。如果重新设计加工,一般至少需要一年时间,再投入上千万美元的经费,有时候甚至需要上亿。

敲黑板,戴眼镜,既然大家普遍对芯片制造的难度有一定的了解,那这篇文章希望可以让大家对芯片设计的难度也有共同的认知。

01 第一关,难在架构设计

芯片设计,环节众多,每个环节都面临很多挑战。以相对较为简单的数字集成电路设计为例设计多采用自顶向下设计方式,层层分解后包括:

需求定义:结合外部环境分析、供应链资源、公司自身定位等信息,提出对新一代产品的需求,并进一步考虑产品作用、功能、所需线板数量、使用集成电路类型等,精准定义产品需求。这一环节的难度在于对市场、技术的未来趋势准确判断和对设计人员、制造工厂等自身和产业链情况、能力的充分了解。

功能实现:描述芯片需要实现的目标,通常用硬件描述语言编写。这一环节的难度在于对芯片整体可以达到的性能、功能的把握,既要充分满足目标,又不能超过自身的能力上限。

结构设计:根据芯片的特点,将其划分成接口清晰、相互关系明确、功能相对独立的子模块。这一环节难度在于对芯片结构的熟悉,是否能用尽可能少的模块和尽可能低的标准达到要求。

逻辑综合:开发者将硬件描述语言转换成逻辑电路图。这一环节难度在于需要保证代码的可综合、清晰简洁、可读性,有时还要考虑模块的复用性。

物理实现:将逻辑电路转换成为有物理连接的电路图。这一环节难度在于如何根据制程,使用尽可能少的元件和连线完成从 RTL 描述到综合库单元之间的映射,得到一个在面积和时序上满足需求的门级网表,并使内部互不干扰。

物理版图:以 GDSII 的文件格式交给晶圆厂,在硅片上做出实际的电路,再进行封装和测试,得到物理芯片。

必须说明的是,芯片设计时,需要考虑许多变量,例如信号干扰、发热分布等,而芯片的物理特性,如磁场、信号干扰,在不同制程下有很大不同,没有数学公式可以直接计算,也没有可套用的经验数据直接填入,只能依靠 EDA 工具一步一步设计,一步步模拟,不断取舍。每一次模拟之后,如果效果不理想,就要重新设计一次,对团队的智慧、精力、耐心都是极大考验。

02 第二关,难在验证

芯片验证目标是在芯片制造之前,通过检查、仿真、原型平台等手段反复迭代验证,提前发现系统软硬件功能错误、优化性能和功耗,使设计精准、可靠,且符合最初规划的芯片规格。

它不是在设计完成后再进行的工序,而是贯穿在设计的每一个环节中的重复性行为,可细分为系统级验证、硬件逻辑功能验证、混合信号验证、软件功能验证、物理层验证、时序验证等。

验证很难,首先在验证只能证伪,需要反复考虑可能遇到的问题,以及使用形式化验证等手段来保证正确的概率,非常考验设计人员的经验和智慧。

其次在验证的方法必须尽可能高效。现在的芯片集成了微处理器、模拟 IP 核、数字 IP 核和存储器 (或片外存储控制接口),验证复杂度指数级增长。如何快速、准确、完备、易调试地完成日益复杂的验证,进入流片阶段,是每个芯片设计人员最大的挑战。

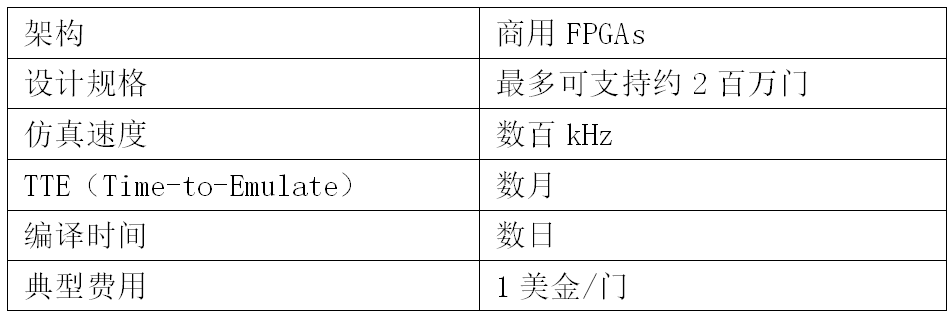

最后在验证工具本身。以常见的 FPGA 硬件仿真验证为例,90 年代 FPGA 验证最多可支持 200 万门,每门的费用为 1 美元。如今单位价格虽然大幅下降,随着芯片的复杂程度指数级增长,验证的门数也上升到以千万和亿为计算的规模,总体费用更加惊人。

此外,FPGA 本身也是芯片设计的一种。现在大型设计(大于 2 千万等效 ASIC 门)需要用多块 FPGA 互联进行验证,FPGA 的设计面对 RTL 逻辑的分割、多片 FPGA 之间的互联拓扑结构、I/O 分配、布局布线、可观测性等现实要求,这就又给设计环节增加了难度。

3 第三关,难在流片

流片就是试生产,设计完后,由芯片代工厂小批量生产一些,供测试用。它看起来是芯片制造,但实际属于芯片设计行业。

流片技术上不困难,因为芯片设计基于现有工艺,除了少量需要芯片设计企业指导的生产之外,困难在于钱、钱、钱。

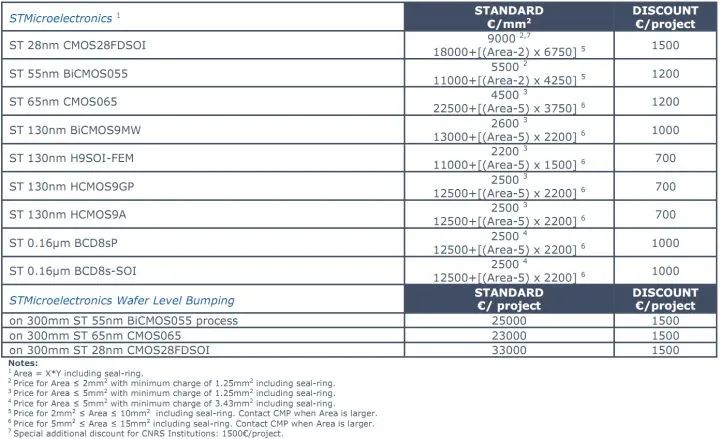

流片一次有多贵?先引用 CMP(Circuits Multi-Projets, 美国一家非营利性多项目晶圆服务组织)的公开报价吧。

按照这份报价,以业内裸芯(die)面积最小的处理器高通骁龙 855 为例(尺寸为 8.48 毫米 ×8.64 毫米,面积为 73.27 平方毫米),用 28 纳米制程流片一次的标准价格为 499,072.5 欧元,也就是近 400 万元人民币!

然后,芯片设计企业可以拿到什么呢?25 个裸芯,平均每个 16 万元!

更重要的是,流片根本不是一次性的事啊!

流片失败,需要修改后再次流片;流片成功,可能需要继续修改优化,二次改进后再次流片。

每一次都需要至少几百万元。

什么叫做氪金?这才叫做氪金啊!

或许有知友会提出疑问,这是成本上的问题,为什么算在困难上呢?这当然是困难了,世界上最大的困难不就是没钱吗?

之所以在会提到流片费用,是因为许多人在谈及芯片制造困难的时候都会指出,建立一条先进制程芯片产线需要天量资金投入,但通过流片可以看出,其实芯片设计对资金的渴求也同样惊人。

04 第四关,越来越具有挑战性的设计需求

首先是随着芯片使用场景延伸至 AI、云计算、智能汽车、5G 等领域,芯片的安全性、可靠性变得前所未有的重要,对芯片设计提出更高、更严格的要求。

其次是随着 AI、智能汽车等领域快速发展,带来专用芯片和适应行业需求的全新架构需求,这一全新的课题给芯片设计带来更多新的挑战。

最后是随着硅基芯片根据摩尔定律,在两三年之后将达到 1 纳米的工艺极限,继续提升性能、降低功耗的重任更多落在芯片设计身上,给芯片设计更大的压力。此外,制程工艺提升也迫切需要芯片设计的指导才能实现,也额外增加了压力。

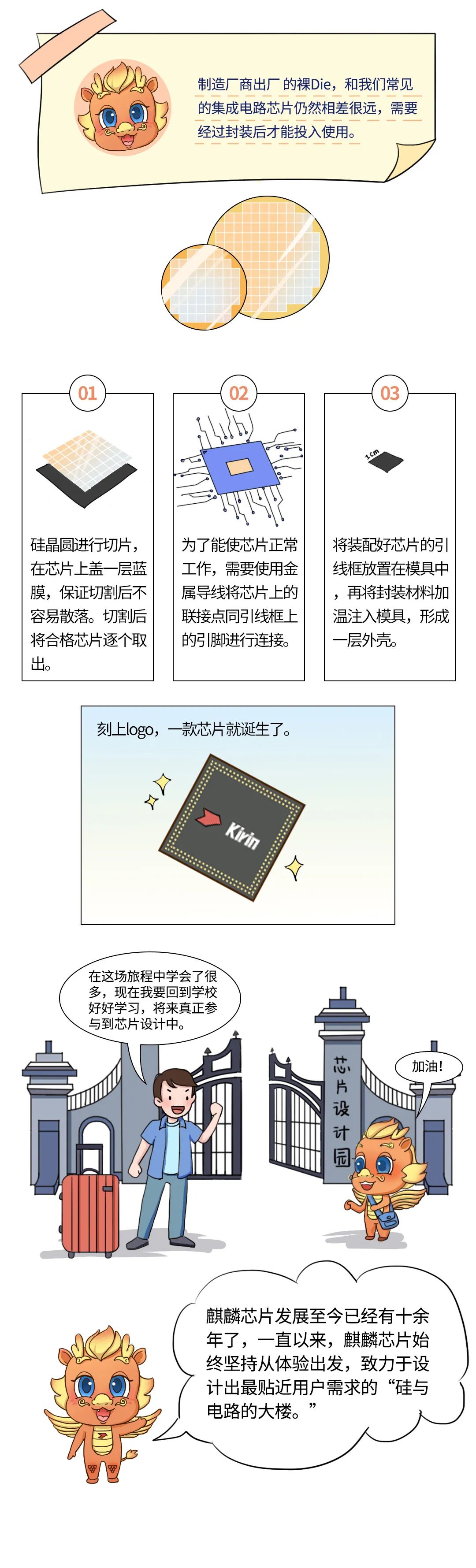

走进晶圆厂,深入了解芯片制造流程

电子汇 2024 年 09 月 05 日 22:45 广东

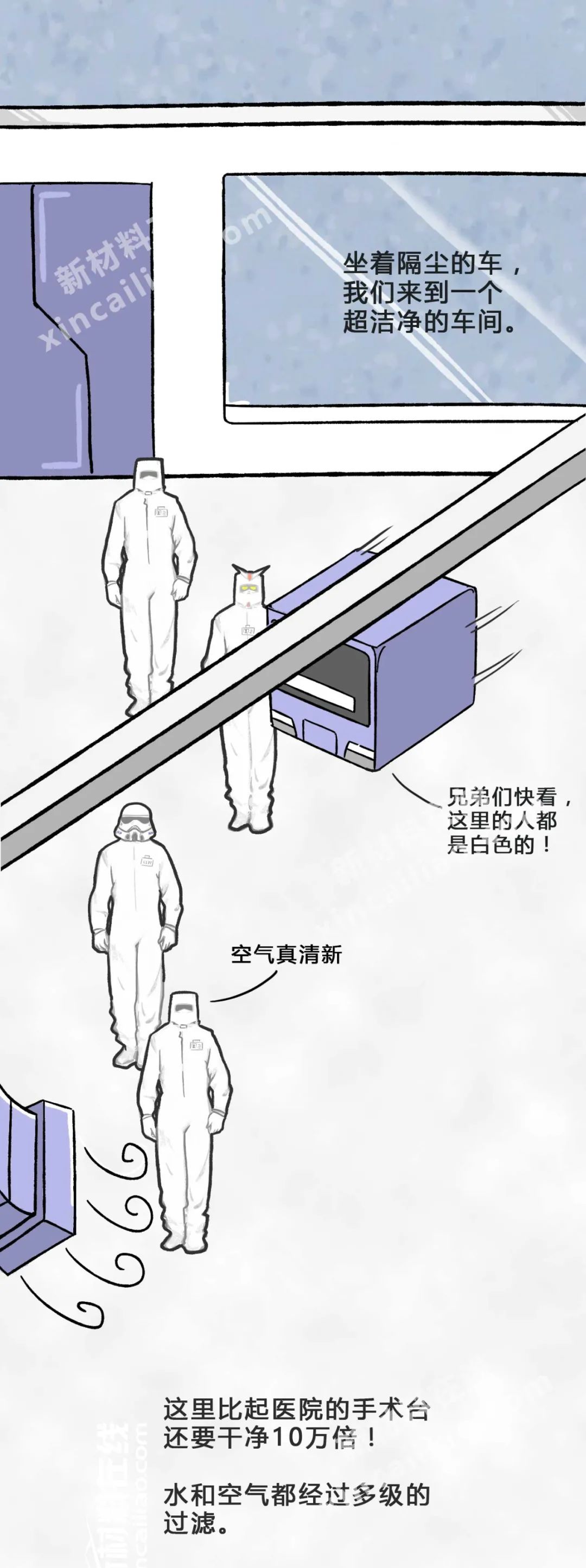

有些晶体管的尺寸超过 500 亿个,这些晶体管比人类头发丝的宽度还小 1 万倍。它们是在巨大的超洁净厂房地板上制作的,可达七层楼高,长度相当于四个足球场。

芯片在许多方面都是现代经济的命脉。它们为电脑、智能手机、汽车、电器和其他许多电子产品提供动力。但自疫情以来,世界对它们的需求激增,这也导致供应链中断,导致全球短缺。

这反过来又加剧了通货膨胀,并在美国引起了人们的警觉:美国正变得过于依赖海外制造的芯片。美国仅占全球半导体制造产能的 12% 左右;超过 90% 的最先进的芯片来自台湾。

硅谷巨头英特尔 (Intel) 正试图恢复其在芯片制造技术方面的长期领先地位,该公司正押注 200 亿美元,希望能帮助缓解芯片短缺的局面。该公司正在其位于亚利桑那州钱德勒的芯片制造中心建造两家工厂,这将需要三年时间才能完成。最近,该公司宣布了可能更大规模的扩张计划,将在俄亥俄州的新奥尔巴尼和德国的马格德堡建立新工厂。

为什么制造数以百万计的这些微小部件意味着建造和花费如此之大?看看位于俄勒冈州钱德勒和希尔斯伯勒的英特尔生产工厂,就能找到一些答案。

芯片有什么作用?

芯片或集成电路在 20 世纪 50 年代末开始取代体积庞大的单个晶体管。许多这些微小的部件是在一块硅上生产的,并连接在一起工作。产生的芯片存储数据、放大无线电信号和执行其他操作;英特尔以各种微处理器而闻名,它们执行计算机的大部分计算功能。

英特尔公司已经成功地将其微处理器上的晶体管缩小到令人难以置信的尺寸。但竞争对手台积电可以生产更小的元件,这是苹果选择台积电为其最新款 iPhone 制造芯片的一个关键原因。

芯片是如何制造的

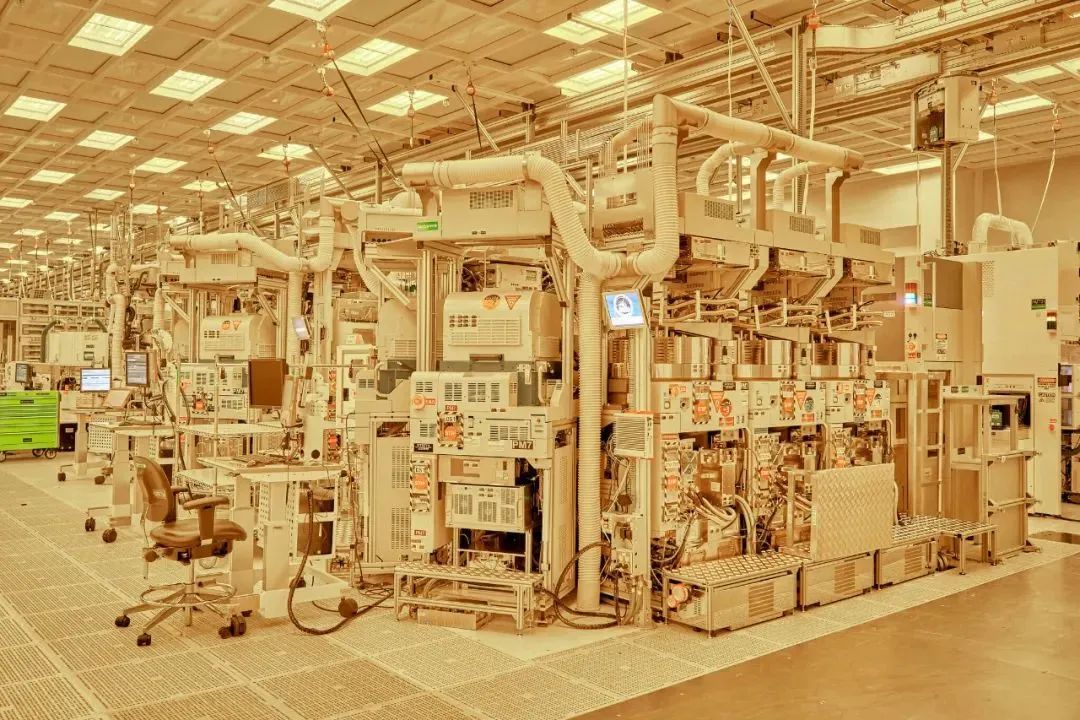

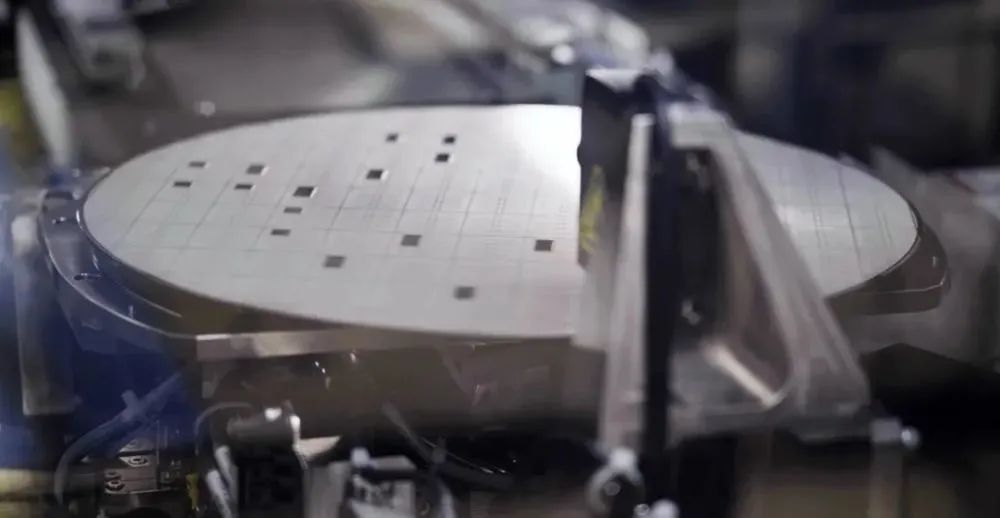

成排排列的专用机器接收装满芯片的容器,这些芯片被移入和移出这些系统进行处理。

其中一台机器用于在制造芯片时从硅晶片上蚀刻材料。

芯片制造商将越来越多的晶体管封装到每一块硅上,这就是为什么技术每年都在增加。这也是为什么新的芯片工厂要花费数十亿美元,而很少有公司能负担得起。

除了建造厂房和购置机器外,公司还必须花费巨资开发复杂的加工步骤,用平板大小的硅片来制造芯片 —— 这就是为什么这些工厂被称为 “晶圆厂”。

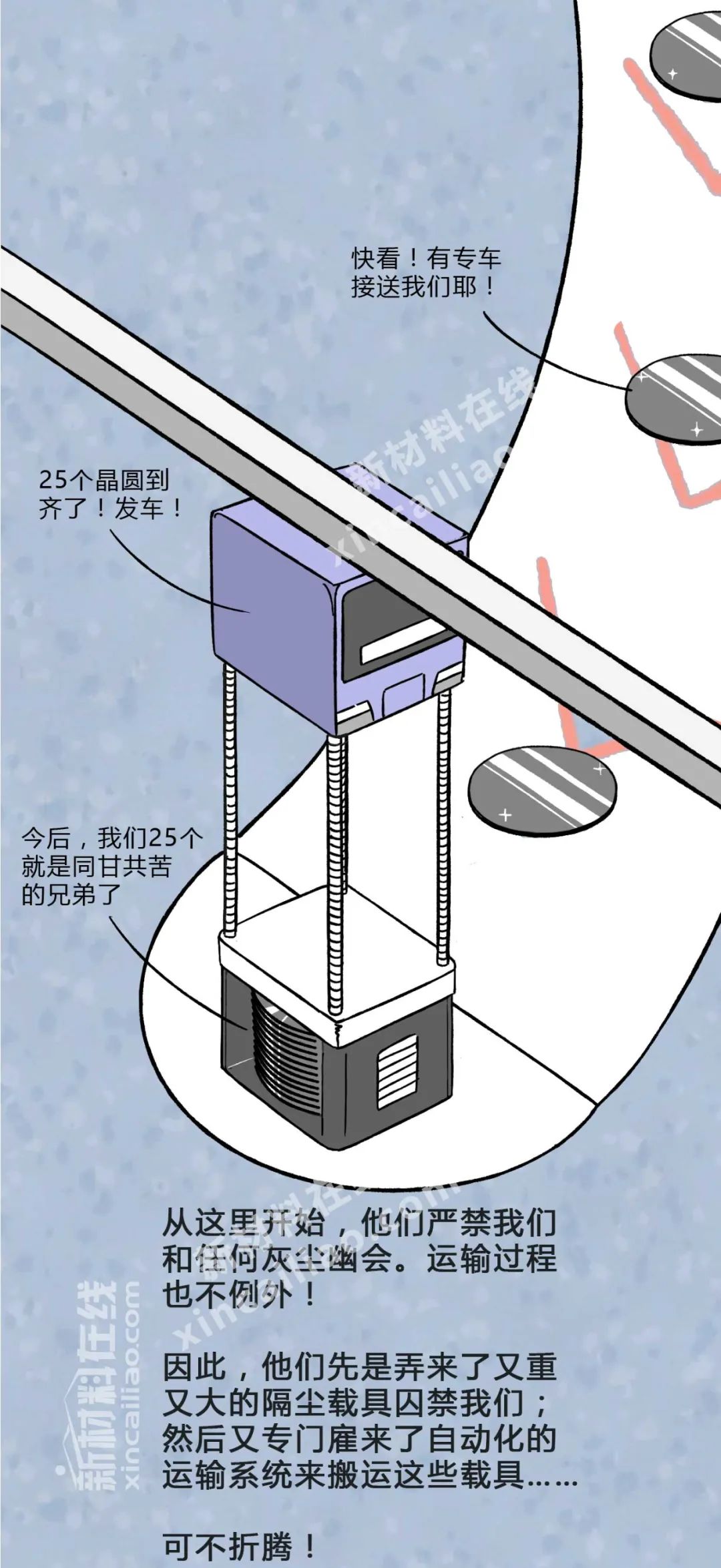

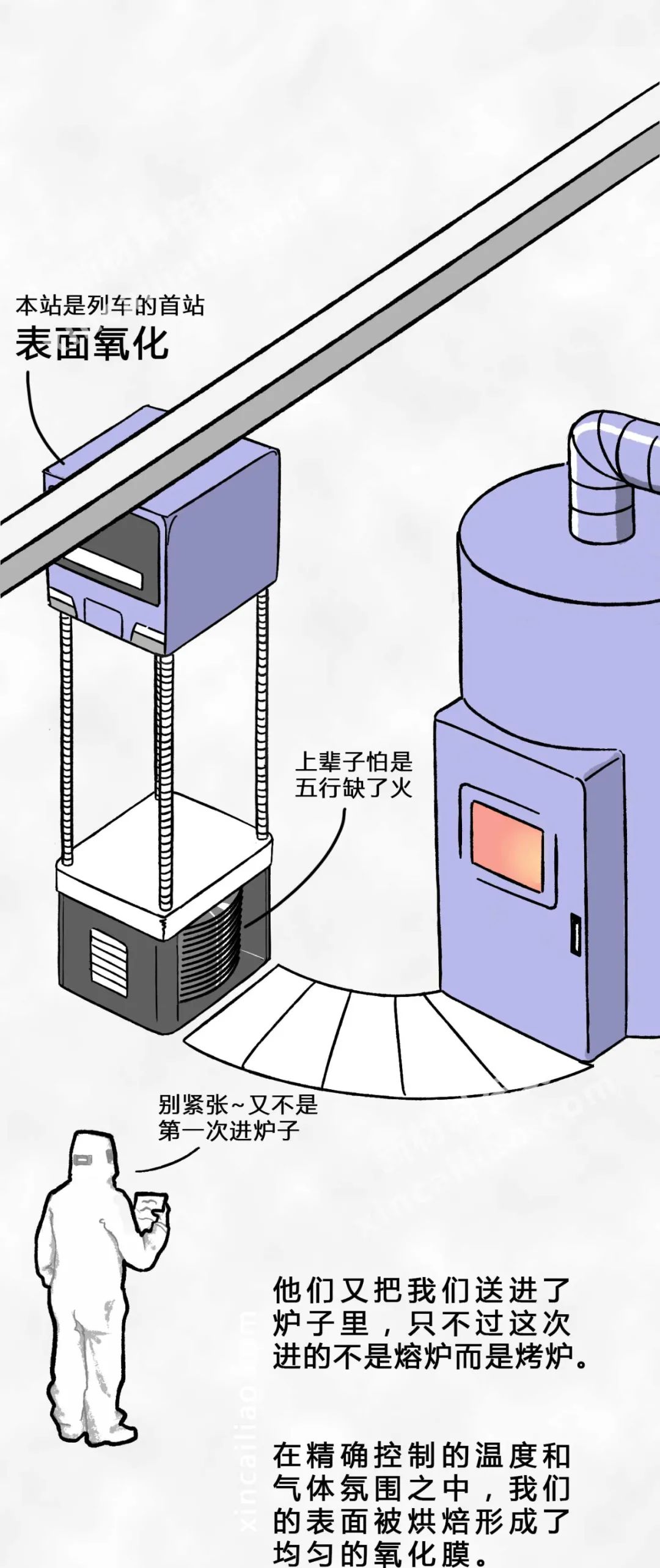

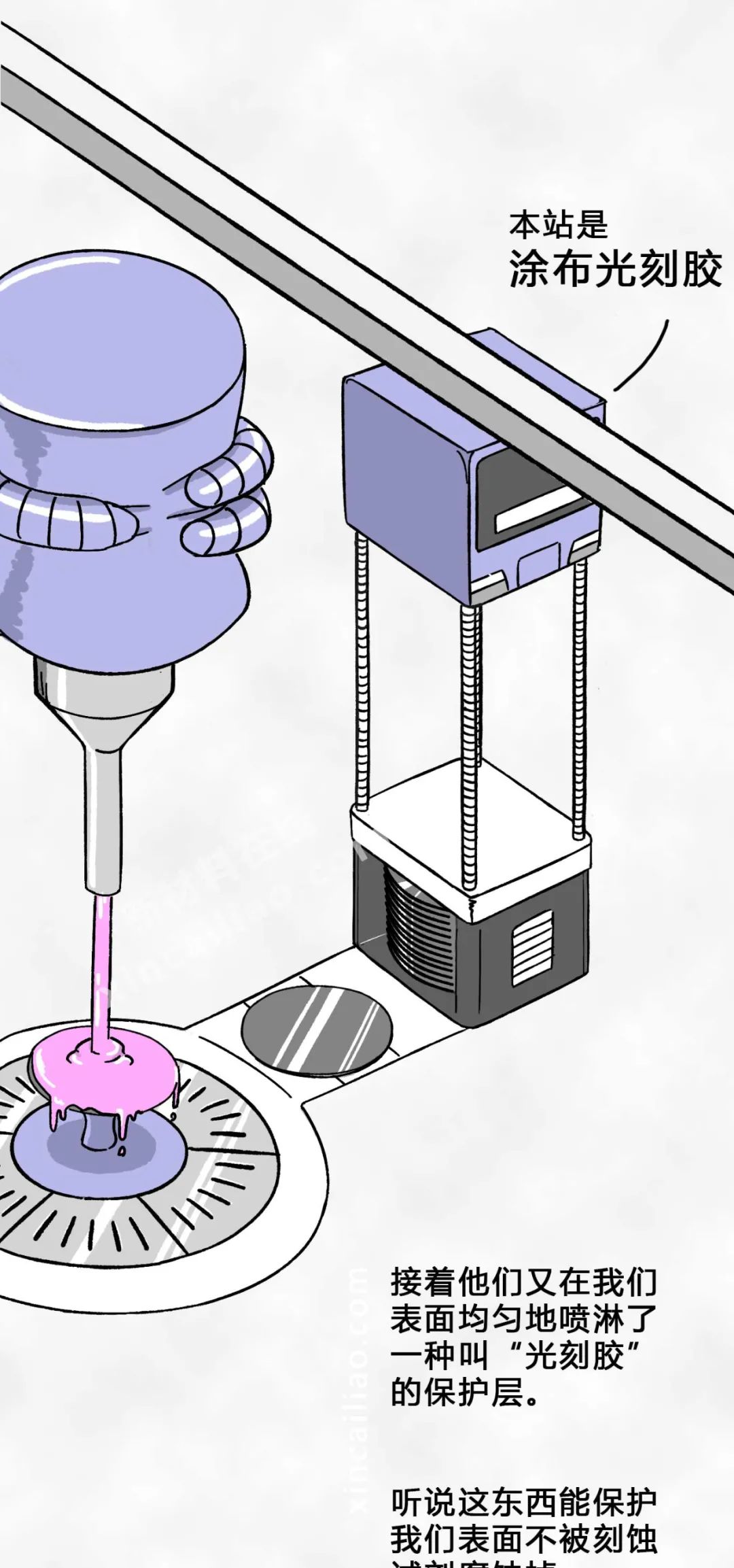

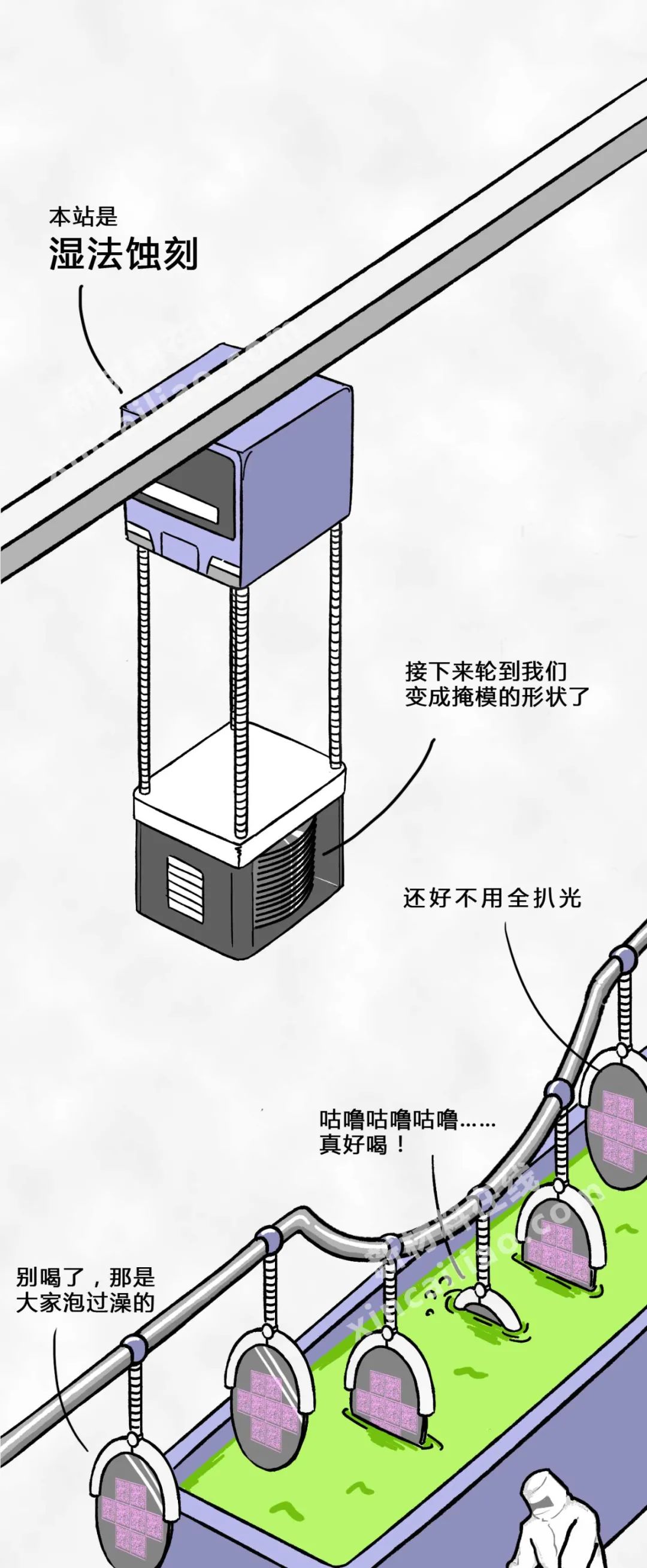

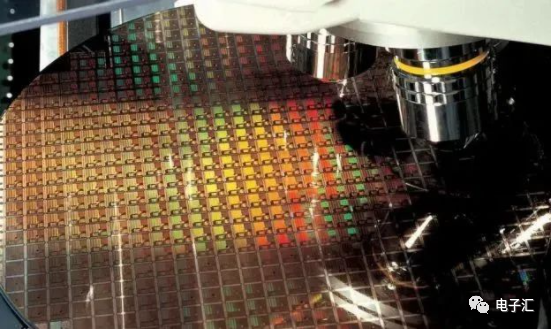

巨大的机器在每个晶圆上设计芯片,然后沉积和蚀刻材料层来制造晶体管并将它们连接起来。在这些系统中,在自动高架轨道上的特殊吊舱中,一次最多可运送 25 片晶圆。

加工一块晶圆需要数千个步骤,长达两个月。近年来,台积电已经为产量设定了节奏,运营着拥有四条或四条以上生产线的 “千兆工厂”(gigafabs)。市场研究公司 TechInsights 的副董事长 Dan Hutcheson 估计,每个工厂每月可以加工 10 万片以上的晶圆。他估计,英特尔在亚利桑那州的两家计划投资 100 亿美元的工厂每个月的生产能力约为 4 万个晶圆。

芯片如何封装

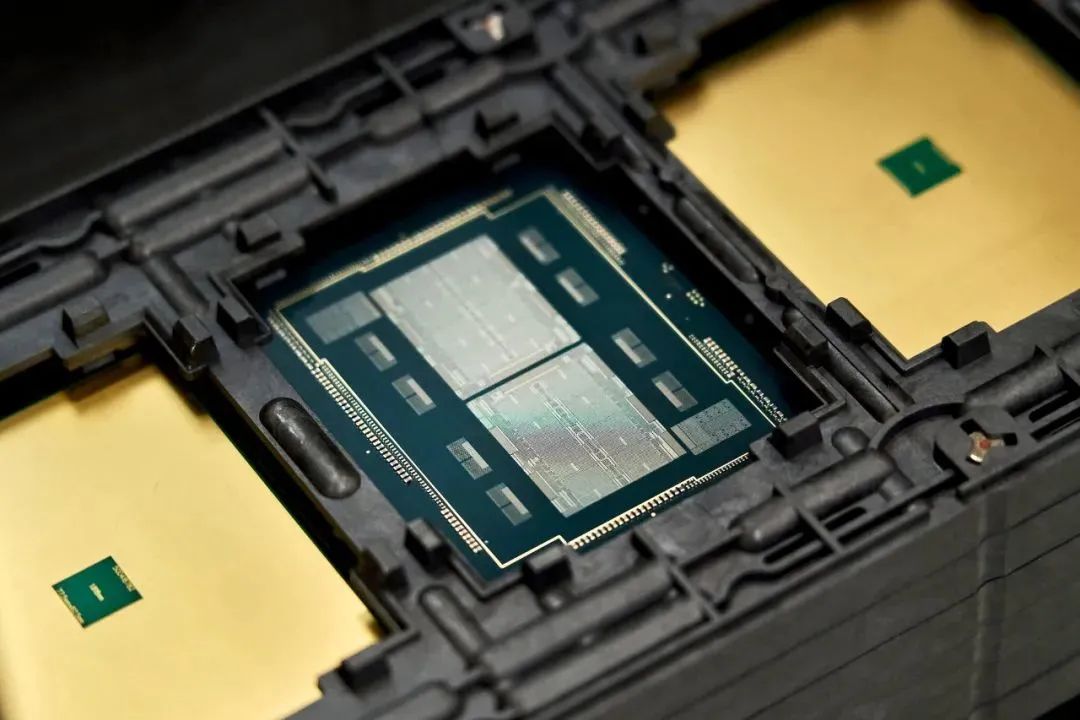

使用新技术堆叠芯片,然后进行封装。

单个芯片在包装前存储在磁带和卷轴上。

芯片将附着在封装基板上。

在封装过程中,小型 “小芯片” 将直接键合到晶圆上。

加工后,晶圆被切成单独的薄片。这些被测试和包裹在塑料包装连接到电路板或系统的一部分。

这一步已经成为一个新的战场,因为要把晶体管做得更小更加困难。现在,各家公司正在将多个芯片堆叠起来,或者将它们并排放置在一个包装中,将它们连接起来,就像一块硅片一样。

如今,将少量芯片封装在一起已成为一种常规做法,而英特尔 (Intel) 已经开发出一种先进的产品,利用新技术将 47 个独立芯片捆绑在一起,其中包括一些由台积电 (TSMC) 和其他公司制造的芯片,以及在英特尔工厂生产的芯片。

是什么让芯片工厂与众不同

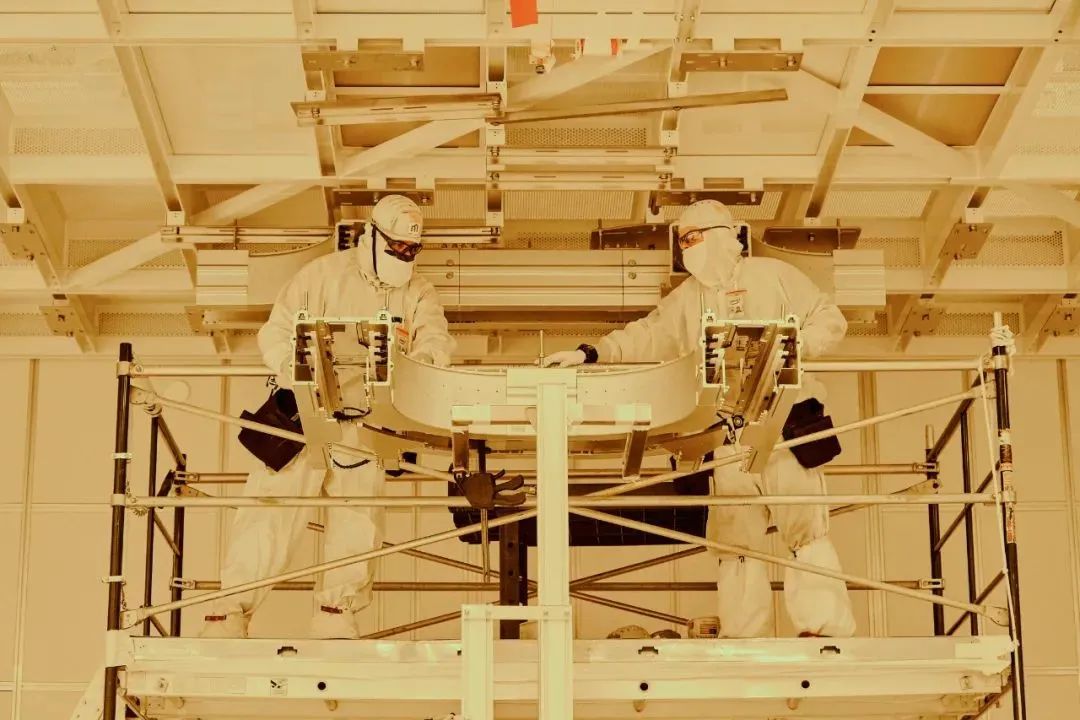

英特尔员工在俄勒冈州希尔斯伯勒的英特尔园区洁净室内等待移动工具零件。

工人在洁净室内安装自动化物料搬运系统。

大型管道将气体从英特尔希尔斯伯勒园区的处理机器中排出。

英特尔芯片通常售价为数百至数千美元。例如,英特尔今年 3 月发布了其最快的台式电脑微处理器,起价为 739 美元。一块肉眼看不见的灰尘可以毁掉一个人。因此,晶圆厂必须比医院手术室更清洁,需要复杂的系统来过滤空气、调节温度和湿度。

晶圆厂还必须不受任何可能导致昂贵设备故障的振动的影响。因此,完美的洁净室建在巨大的混凝土板上,安装在特殊的减震器上。

同样重要的是移动大量液体和气体的能力。英特尔的顶级工厂大约有 70 英尺 (21 米) 高,有巨大的风扇帮助空气循环到正下方的洁净室。在洁净室的下面是成千上万的泵、变压器、动力柜、公用事业管道和与生产设备连接的冷水机。

对水的需求

希尔斯伯勒的水处理厂。芯片制造每天需要数百万加仑的水。

英特尔希望与环保组织和其他组织合作,到 2030 年增加亚利桑那州的供水。

英特尔希尔斯伯勒工厂的一座塔从水中去除气体。

晶圆厂是水密集型业务。这是因为在生产过程的许多阶段都需要水来清洁晶圆。

英特尔公司在钱德勒的两个站点每天从当地公用事业单位共抽取约 1100 万加仑 (约 4200 万升) 的水。英特尔未来的扩张将需要更多的资金,这对于像亚利桑那州这样饱受干旱困扰的州来说似乎是一个挑战,该州已经削减了对农民的用水分配。但农业实际消耗的水比一个芯片厂多得多。

英特尔表示,它在钱德勒的站点依靠三条河流和一口井的供应,通过过滤系统、沉淀池和其他设备回收了约 82% 的淡水。这些水被送回该市,该市运营英特尔资助的处理设施,并重新分配用于灌溉和其他非饮用水用途。

英特尔希望通过与环保组织和其他组织合作,在当地社区节约和恢复水资源的项目上,到 2030 年促进亚利桑那州和其他州的供水。

如何建造晶圆厂

希尔斯伯勒的工人搬运建筑材料。

英特尔未来在钱德勒的工厂之一。为了建造其设施,英特尔将需要大约 5,000 名熟练的建筑工人,为期三年。

挖掘钱德勒的两个新工厂的地基预计将清除 890,000 立方码的泥土

Chandler 挖掘的泥土将以每分钟一辆自卸卡车的速度运走。

起重机在钱德勒工地搬运建筑材料。除其他外,这些起重机将为新晶圆厂吊装 55 吨冷水机。

为了建造未来的工厂,英特尔将在三年内需要大约 5000 名熟练的建筑工人。

他们有很多事要做。英特尔建筑主管丹・多伦 (Dan Doron) 说,挖掘地基预计将清除 89 万立方码 (约合 68 万立方米) 的泥土,这些泥土以每分钟一辆自卸卡车的速度运走。

该公司预计将浇筑超过 44.5 万立方码的混凝土,并使用 10 万吨钢筋作为地基,这比建造世界最高建筑迪拜哈利法塔的钢筋还要多。

多伦说,一些施工用的起重机非常大,需要 100 多辆卡车才能把零件组装起来。这些起重机将为新晶圆厂吊起 55 吨的冷却器。

一年前成为英特尔首席执行官的帕劳・基辛格正在游说美国国会为芯片厂建设提供拨款,并为设备投资提供税收抵免。为了管理英特尔的支出风险,他计划重点建设晶圆厂 “外壳”,这些外壳可以配备相应的设备,以应对市场变化。

为了解决芯片短缺的问题,基辛格将不得不执行他的计划,生产由其他公司设计的芯片。但一家公司能做的也就这么多了;像手机和汽车这样的产品需要来自许多供应商的零部件,以及旧芯片。在半导体领域,也没有哪个国家能够独善其身。尽管推动国内制造业可以在一定程度上降低供应风险,但芯片行业将继续依赖一个复杂的全球企业网络来提供原材料、生产设备、设计软件、人才和专业制造。

转自:半导体行业观察翻译自纽约时报

一个亿,在一家芯片公司可以烧多久?

电子汇 2024 年 10 月 28 日 17:18 广东

这个问题我分别问了几个芯片公司的创始人。

有说 2 年的(某中等规模电路,成熟制程的 MCU 芯片公司);

有说 1 年的(某 AI 算力芯片公司);

有说半年的(通讯 SoC 芯片,需要搭建百人团队的);

最厉害的有说一个月的(这花钱的速度… 不禁让我流下了贫穷的泪水);一个月花完的这位兄弟是买了某 A 字母公司出品的超豪华架构套餐吗?

一个亿烧完的时候,其实很多公司连芯片的影儿都没见着,有模有样的 demo 可能都没搞出来。但是不好意思,下一笔融资必须马上接着到账,否则之前投的钱就可能全部打水漂。这钱到底怎么烧的。芯片设计公司并没有什么特别昂贵的机器和场地投入,属于轻资产公司,主要开销来自人员的成本,流片成本以及各类知识产权类和服务类的费用,这几项开销,会让你体会到什么才叫花钱如流水。

拿一款应用于数据中心的 AI 处理器芯片来举例,即便做一款不算业界最高精尖的指标的,一个亿也只能勉强搞个一代产品出来。

对于芯片团队来说,首先得找三个架构师是没跑儿的(一个做系统级的,俩微架构 IP 级的或者搞搞性能设计和 PPA 的),第一步至少地把芯片架构搭起来啊,按照 2021 年下半年的数据,资深一点的架构师(架构师没有资历太浅的)的年薪基本已经是 150W 起步,如果想招业界超级大牛架构师他们的薪资 200W 起。桥豆麻袋!这是架构师的现在薪资,我可没说这是他的期望薪资(手动捂脸),别忘了咱们是一家初创公司,想要吸引顶级的架构师进来咱们团队怎么办?现金,期权股票,愿景灌输(江湖俗称洗脑脑或画饼饼)一样不能少啊。哦对了,创始人如果有很强的说服能力和个人魅力和行业影响力,能让一群牛逼的大佬选择平薪甚至降薪加入,遇到这样的创始人,金主爸爸们投资人们就赶紧投了,我把它称之为芯片企业的第二核心竞争力!

架构师有了,吭哧吭哧搭建个小半年是最少的,期间开始要做具体的 RTL 了。芯片小规模的?先招 5 个 designer(逻辑芯片设计工程师)。中等规模的?先招 10 个 designer 吧。超大规模的?20 个起,上不封顶。等等,光有设计肯定不行,一个设计得配俩验证(design verification)工程师吧,咱们初创公司,得省着点花钱,一个设计工程师配 1.5 个验证工程师,或者一个设计师配一个经验丰富的验证工程师(妈妈夸我真是省钱小能手)。即使是最小规模编制的团队,也要 10 位芯片前端的工程师(5 位设计 + 5 位验证),由于设计和验证属于整个行业最紧俏的人才类型,去年大部分的芯片公司为了确保团队稳定,都给自己的工程师团队猛涨了一波薪资,想要说服他们出来加入咱们小初创,要么创始团队说破嘴皮,要么 HR 说破嘴皮,或者花钱让猎头说破嘴皮。目前在职的设计 / 验证人员的薪资范围大概是这样的,以上海行情为例,应届硕士普遍 30-50W;2-5 年普遍 40-80W;5 年 - 10 年 50-100W;10 年以上大多 100W 起步。越是高端的芯片,越是需要资深的人员加入,为了省钱,创始人白天开会,管理,拉融资,晚上还要回公司自己在一线做技术,真的非常不容易;RTL 快要 freeze 的时候,不要停,DFT(可测性设计工程师)和 PD(物理实现工程师)人员就要上了。芯片公司要是想养一个完整的后端团队是非常昂贵的。后端类的工种大多属于项目制,芯片流片节点前才会介入(会阶段性累成汪),在架构和前端阶段时往往工作量不饱和,因此很多芯片公司选择将芯片后端的工作外包给芯片设计服务公司(design service),但是一次设计的费用也要几十万到几百万不等。

芯片公司虽然是属于硬件类的公司,但是软件类的工程师也少不了,由于近两年 AI 芯片的大火,导致曾经的一个冷门品类 “编译器软件工程师” 近两年快被炒出天价了,两个大厂 HR 为了争夺一位 3 年经验的编译器哥打得不可开交甚至要开启拍卖喊价模式的场景还历历在目。现在的芯片在设计阶段,软件、算法就已经要考虑嵌入进去了。如果说芯片设计类的工程师还只是贵,那么芯片算法类的工程师真的是又贵又少又傲娇,一个资深点的 AI 芯片算法工程师的年薪比创始人高个 2 倍也是正常现象。这样算下来,光是基本人员勉强配齐或者找点设计服务公司帮忙干点,2000W 左右已经准备要花出去了,到这里为止还只是刚搭了刚需版本的团队,芯片还连半个影子都没有。

创业初期,创始团队已经要确认好是加入哪个指令集架构阵营了,现在大部分低功耗的逻辑芯片公司用的都是 ARM 公司的架构,做手机芯片的公司基本都在 ARM 的阵营里。ARM 的产品物美但不太会价廉。还记得前面那位大哥买的豪华套餐吗?ARM 的架构起步价通常以百万计算,单位不是人民币而是美金!想要看源代码?一千万美金起步(当然咱初创,先买个 IP 用着,先不想看源码的事情,即便这样也要几百万花出去了)。这个还只是初始授权费用。之后卖出去的每一片芯片,ARM 也会收取一定比例的费用,这个在后续对芯片公司来说就是很可观的一笔支出。既然买个架构都这么贵,那我选不要钱的 RISC-V 架构行不行(你可以理解为手机系统的安卓,开源,便宜甚至不要钱),当然可以!但是后续的生态建设费用高的离谱,你看看那些用 RV 架构的公司,谁家还没有十个八个的 marketing 和 sales 的,而这支市场销售团队又是一年几百万的开支,老板掐指一算,含着泪还是买了 ARM。

接下来,迎面走来的是 EDA 软件方队,他们迈着坚实步伐,对你说:同志,该交钱了。如果说在人员配置,指令集构上还有各种省钱的法子,那么在 EDA 软件这块,这钱真省不下来。所有芯片的设计图纸必须要跑在 EDA 软件上,你可以理解为做网页平面设计的人离开不 Adobe 公司的 Photoshop 一样。正版 EDA 软件,目前还是被几家巨头垄断着,不管是 Synopsys 公司的, Cadence 公司的,还是 Mentor 公司的,买一套又是几百万起(美金),即便是花了上千万买的的 EDA 仿真工具也才给十几个 License。那我用盗版行不行的?除非不想把芯片拿去流片,否则还是老老实实买正版吧。

买虚拟的东西的钱到这里就结束了吗?图样图 simple。接下来就是一堆的 IP 要怎么解决,自己设计还是买还是找 design service 公司来做,总之不管用哪种,都要刷卡。接口类的 HDMI, PCIE,DDR 等等等这些 IP 怎么解决,一个 IP,直接买的话一个可能要几十万甚至上百万,而且每个 license 都有授权期限,过期了还得续费;自己招工程师做 IP,一个小团队的年薪开支也是几百万起,找设计服务公司也是一个道理,人家外包公司老板还要再赚点差价,但是至少接了活儿可以马上撸起袖子干,自己招的人可能还要磨合一段时间,靠不靠谱还要时间来验证。如果是做 CPU 或者手机的 SOC 基带处理器芯片,几十个 IP 等着咱来配齐。算起来,这一块就是几百到几千万的开支,没有上限。

以上开销粗略估计了一下 已经快来到 5000W 的价位了,一个亿的钱,光在这些看不见摸不着的东西和服务上已经花去一半了。开过一家芯片公司以后,突然觉得女朋友的爱马仕包包都显得如此的亲民。但是能把这些钱顺顺利利花出去的公司,其实已经比很多公司要强了,有些公司大半年招不到人的,一直在战略性犹豫是自研还是攒个东西先应付着的,投资人看了后真想口吐芬芳。

准备开始流片后,花钱的速度那简直就是安了火箭一般。流片对于芯片公司来说就像参加一次大考,而且考试报名费出奇地贵。忍不住插播一下,芯片设计公司流片前的场景就跟参加高考前的教室场景一样,到处都是打气横幅:流片攻坚战最后 60 天倒计时… 那氛围,像极了高考前。

小公司流片一般不会选择第一版就 full mask(包下一整块的晶圆片),而是会采用 mpw 方式,类似于拼多多的模式,几家设计公司共享一个晶圆,但要保证使用的是同一种工艺;不管是否拼单,都需要提前把掩膜版(Mask)的钱付了。Mask 这玩意儿的制造设备由于贵的吓人,所以做出来的掩膜版也是无敌贵。一套 65nm 工艺节点的掩膜版起价大概在 100W 美金,如果采用 28nm 工艺,则一套掩膜版 300W 美金起,如果是 14nm,一套 500W 美金起。哦对了,一般一套是不够的,可能需要备足 2 套。投资人的心在滴血。

当然,掩膜版归掩膜版,流片的钱还是要另外付的。流一次片的价格相当于烧掉一套房子,这真不是在开玩笑。成熟工艺流片次可能是上海外环一套房,48nm 工艺流片一次可能是张江一套房,14nm 工艺流片一次可能是黄浦江一套房,5-7nm 工艺流片一次那就是上海法租界一套房。讲到这里,一个亿基本已经花完了。

房子到手后,哦不,是芯片流片回来到手后,马上就要上测试。流片不是说一次流片成功就万事大吉了,通常一款芯片刚 tape out 回来测试至少会有几百个 bug,光是修复这些 bug 一年时间又没了。上面那个巨烧钱的团队成员:老板,咱们工资要结一结了。修复 bug 真的需要绞尽脑汁,让多少青葱少年变成了秃头大叔,解决不了的问题还得找专业的失效分析公司帮你看看,修复几个 bug 几十万是跑不了的,对了,交完钱以后麻烦请后面排一下队,前面还有 10 家芯片公司的档期在排。当然,出现 bug 也不全是设计的问题,有些也会涉及到晶圆厂的工艺的问题,找晶圆厂的工程师找问题。不好意思实在太忙,要不您找外面的第三方测试机构帮您找工艺 bug?一次又是几十万烧掉了。

假设一年以后所有的 bug 都解决了(哪怕还有一个 bug,芯片都还只是一块砖!),就准备找长电,华天封装测试了,虽然也要花钱但是价格比晶圆厂流片确实要亲民不少。Finally,芯片终于做好了。为了下一轮融资和做企宣,这个时候激动人心的发布会终于可以开起来了~手握一颗芯片,微笑面对镜头 “咱家的芯片,YES!”

如果说把办一家芯片公司比作西天取经的话,第一代芯片开始走量的时候,这个时候你可能才刚走出了长安城后面如何打市场,如何提高量产良率,如何降低成本提高毛利率,如何把自己的芯片做进终端的方案里,如何取得各项认证(尤其是汽车芯片!),各项商务谈判会复杂到让你怀疑人生。库存的流转,供应链的拿捏,产能的获取,每一步都如履薄冰,每一步都有要花钱解决和打点的人或者机构。对了,第一代芯片还没开始流片的时候,一般第二代芯片就已经开始研发了,上面的花费每一项都要再重新来一遍。

所以对于芯片初创公司来说,第一次流片失败,如果故事讲得好,下一轮融资进来还能再撑一撑,否则很有可能就撑不到第二次送去流片的时候了。今天一业内大牛跟我说:芯片初创公司团队就是要一鼓作气,再而衰,三而竭。我深表认同,2 次流片没成功,团队凝聚力基本就散掉了,这是花再多钱都买不回的东西。

所以,曾经有圈内一知名投资经理总结出了投资芯片设计公司的三大方法:求签,测八字,看面相。投资前给创始团队每个人都算一卦,看看这帮人有没有大富大贵的命,没有就别浪费钱了。虽然是玩笑话,但还是道出了芯片投资的辛酸和不易。

现在整个半导体圈异常火热,连卖奶茶的公司和卖西裤的公司都扬言要来自研芯片,看完我的这篇回答估计企业老板内心一颤,咱还是安安静静卖奶茶卖衣服吧

来源:知乎 作者:仔小蒙

via:

-

半导体知识及芯片发展史 半导体材料与工艺 2024 年 01 月 11 日 20:46 江苏

-

一文了解半导体的历史、应用、未来 中国科学院半导体研究所 2018 年 10 月 08 日 12:31 北京

-

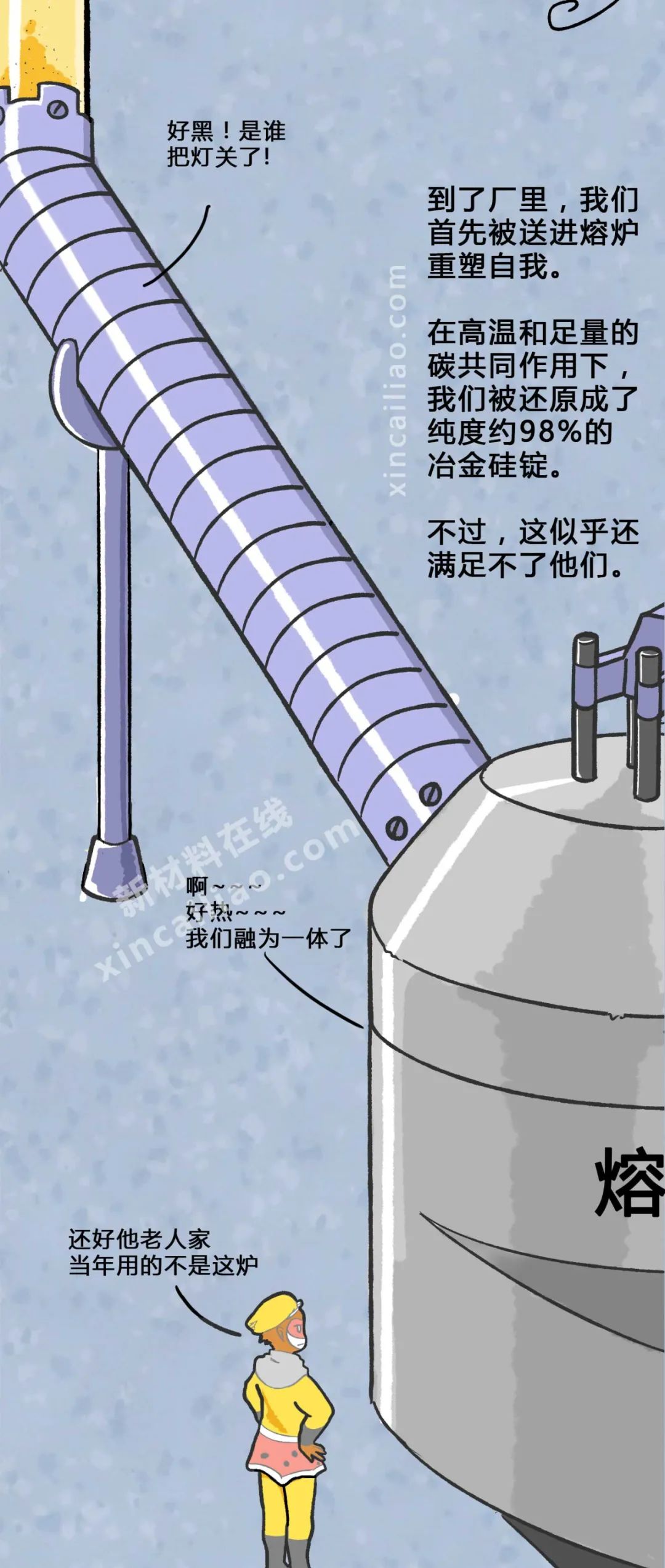

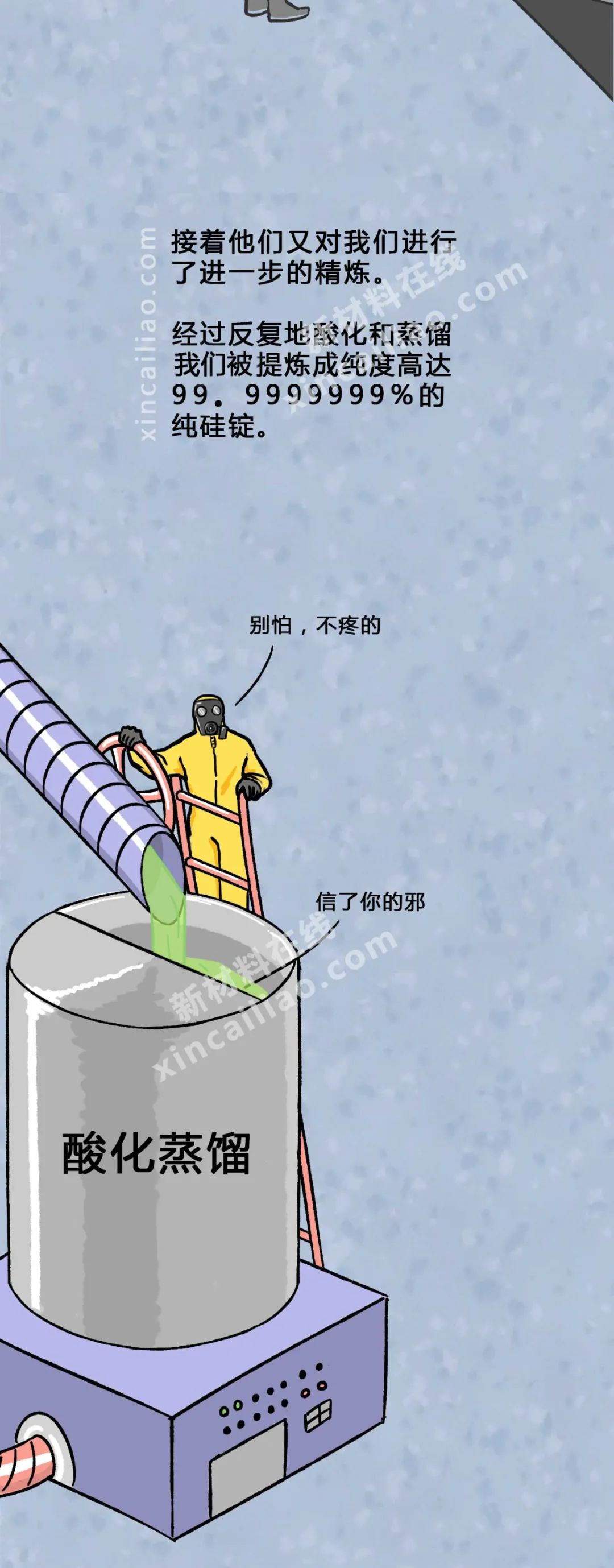

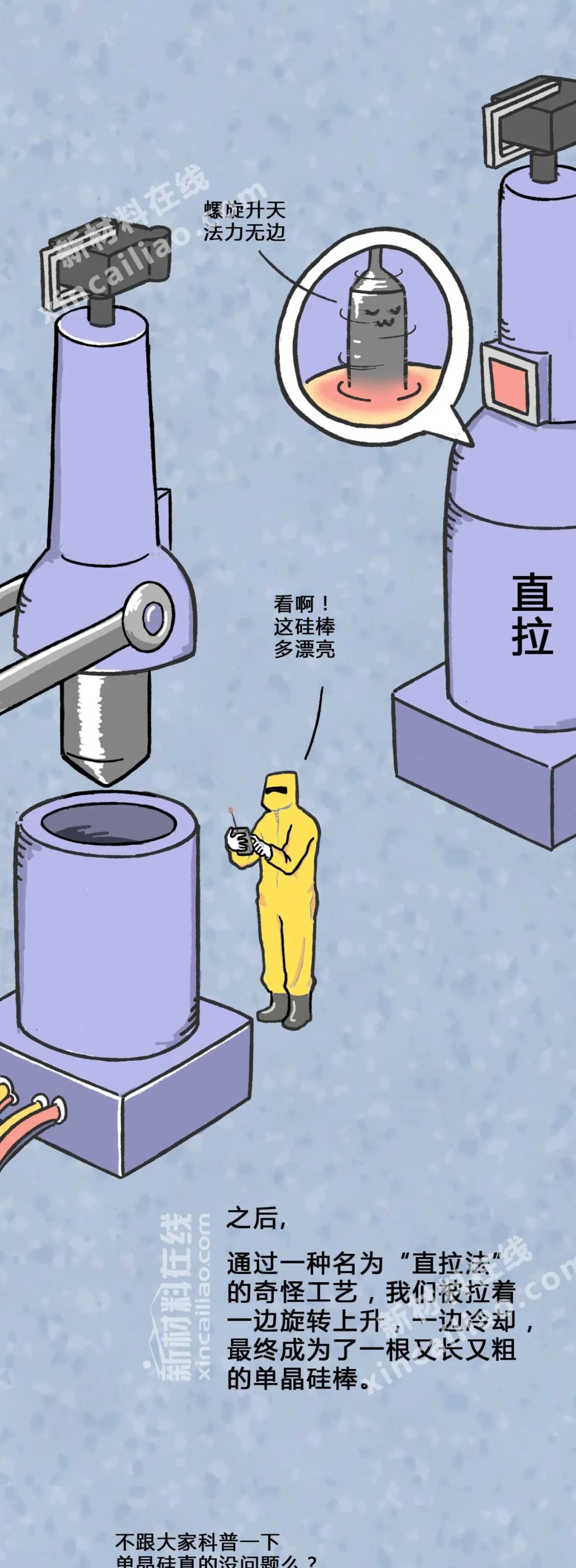

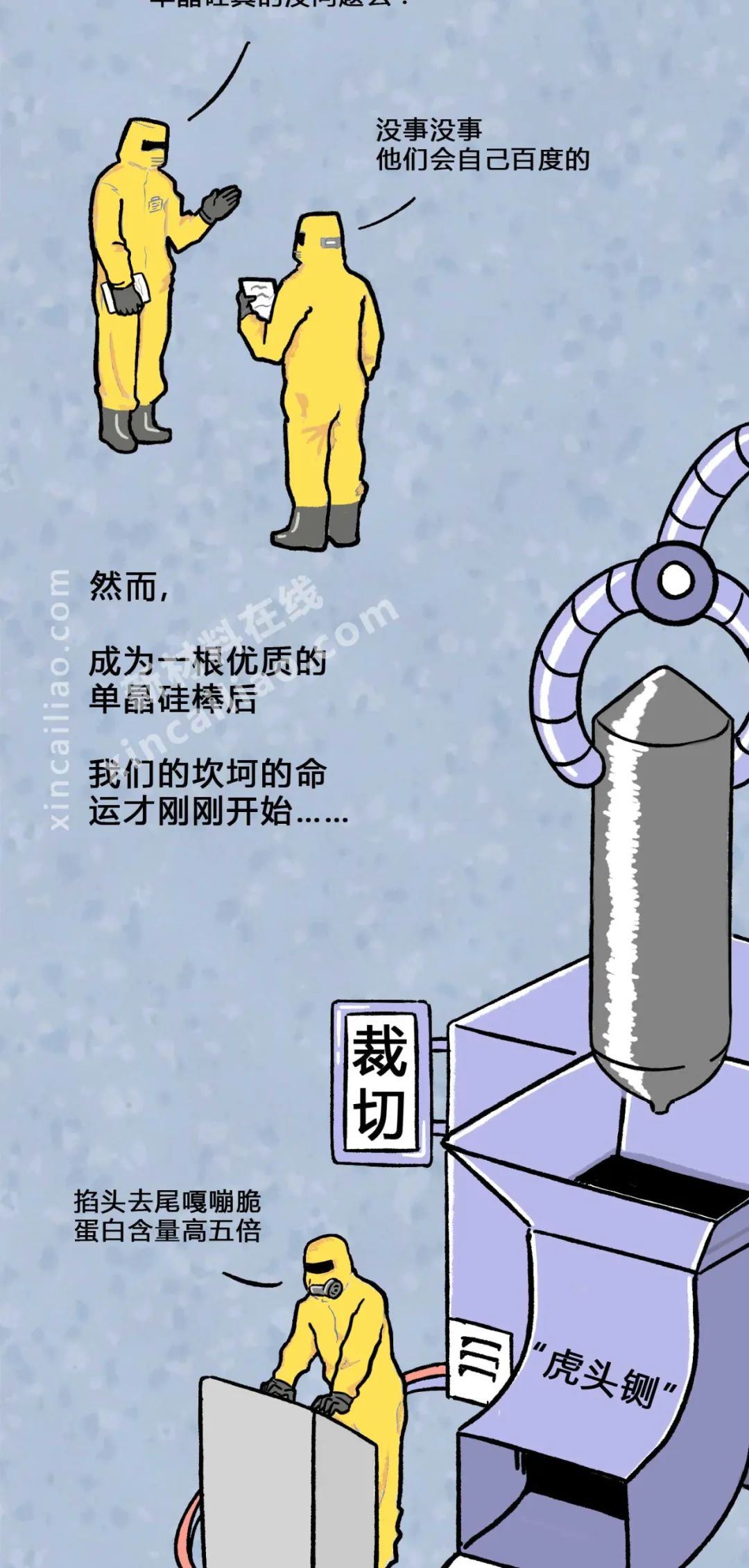

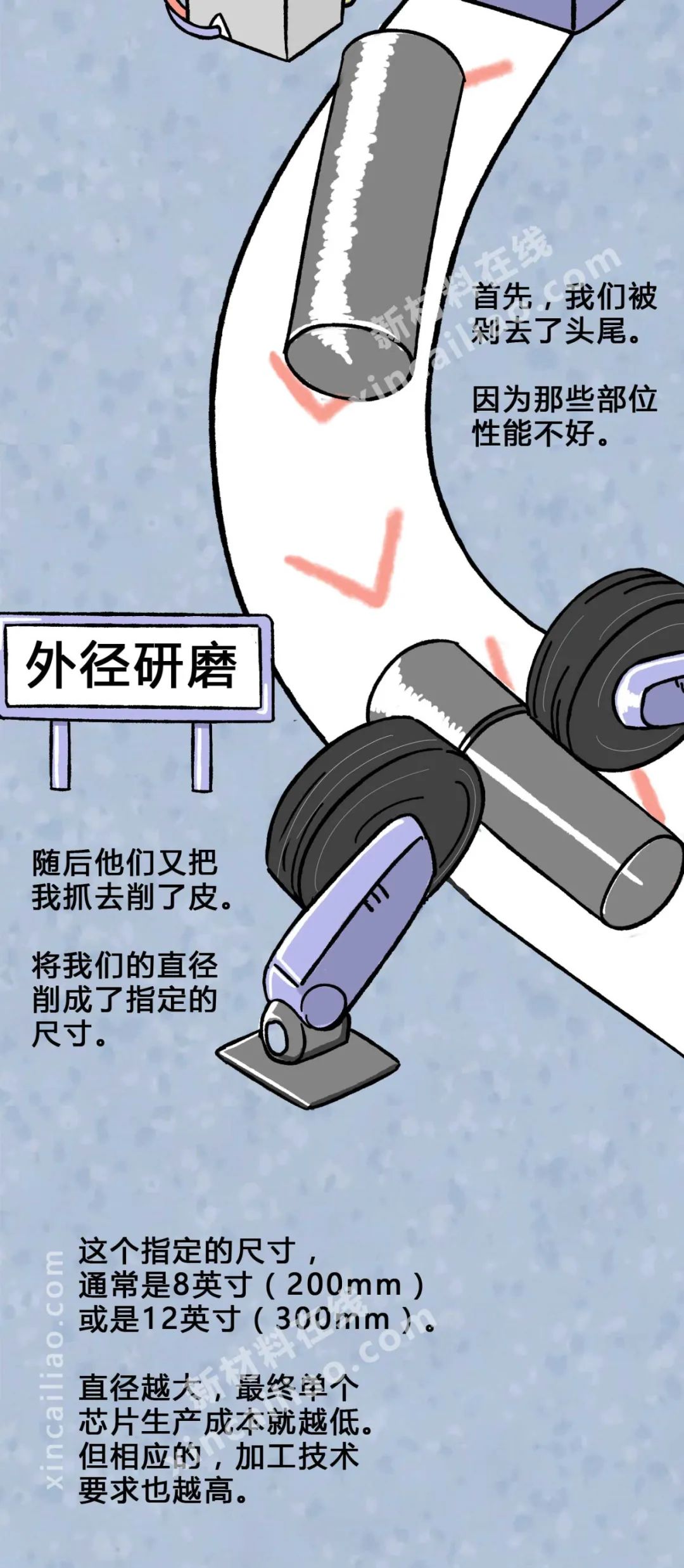

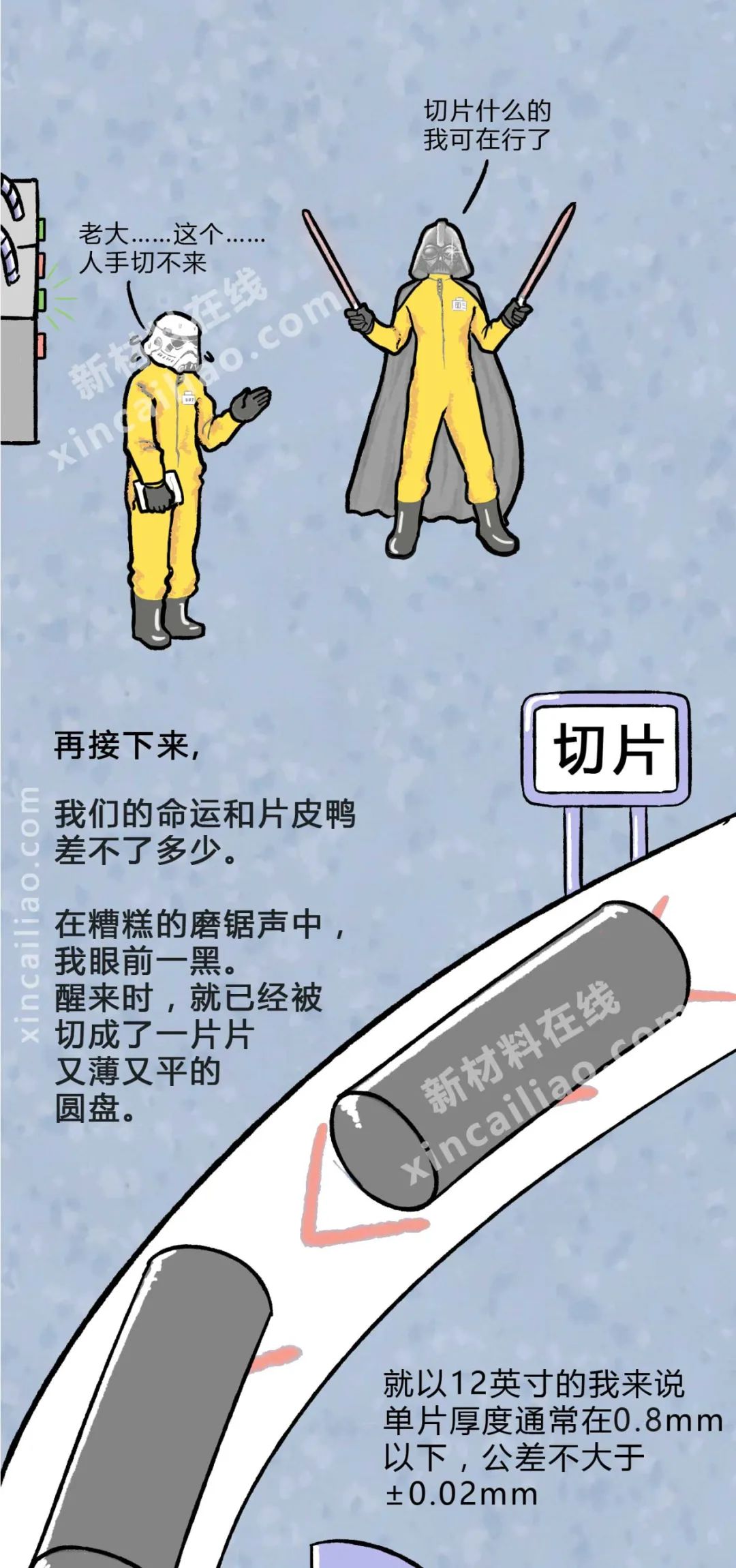

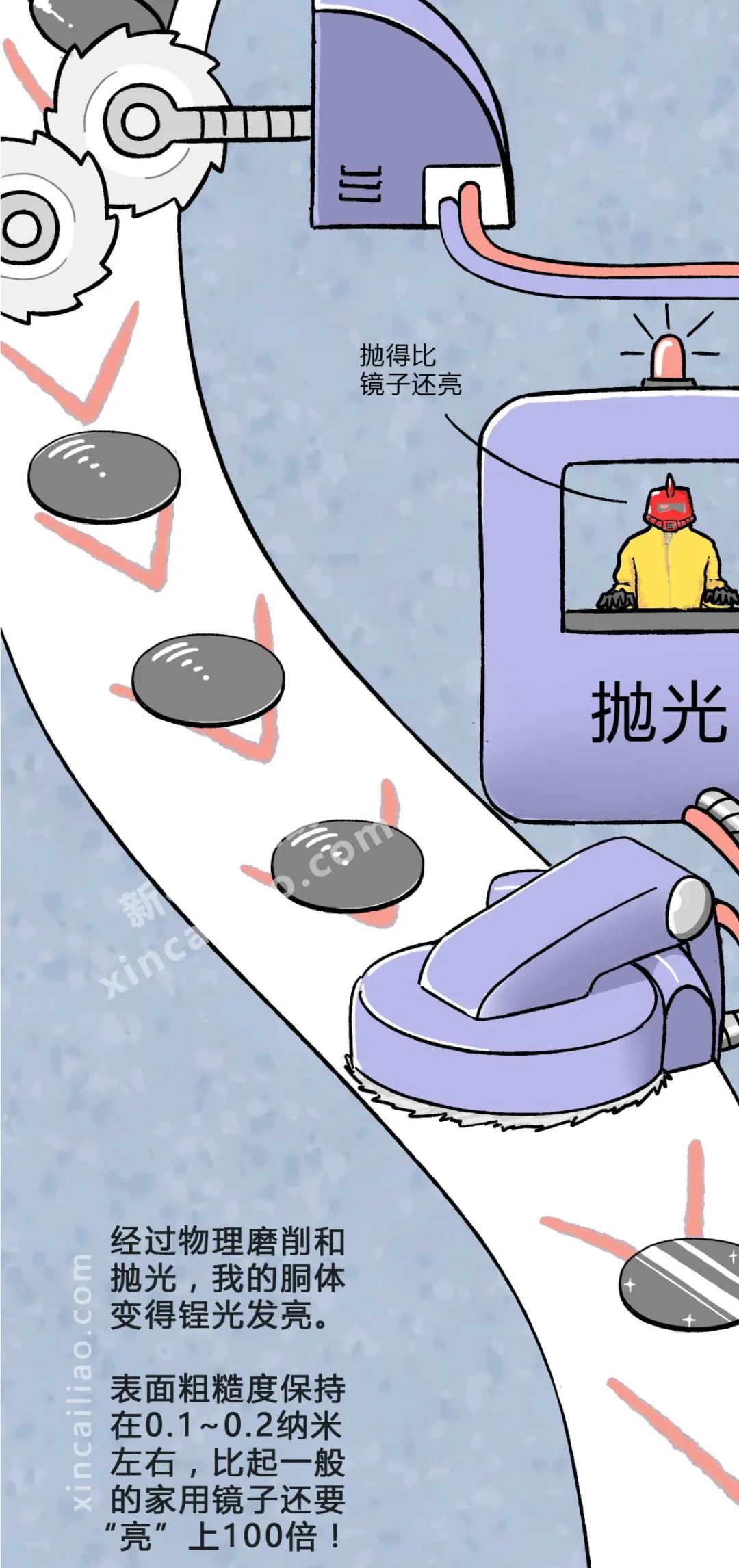

难住中国的芯片,是怎么从沙子中一步步炼成的?新材料在线 2022 年 01 月 01 日 08:30

-

超全!芯片设计制造全流程,科普漫画第五弹带你探访芯片的内 “芯” 世界 爱科普的 华为麒麟 2021 年 11 月 24 日 17:23

-

芯片 - 设计流程入门 *原创 thatway 那路谈 OS 与 SoC 嵌入式软件 2023 年 11 月 01 日 07:16 北京 *

-

我们来谈一谈:芯片设计到底难在哪里?电子汇 2024 年 09 月 05 日 22:45 广东

-

走进晶圆厂,深入了解芯片制造流程 电子汇 2024 年 09 月 05 日 22:45 广东

-

一个亿,在一家芯片公司可以烧多久?电子汇 2024 年 10 月 28 日 17:18 广东

芯片发展、设计、制造全解析

芯片发展、设计、制造全解析

3495

3495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?