注:本文为 “圆圆 De 圆” 的光刻机相关文章的几篇合集。

文中部分插图受原文图源所限不清晰。

了解集成电路及光刻技术发展历程

原创 圆圆 De 圆 半导体全解

一、集成电路诞生背景

为什么集成电路现在被人们提及的越来越多呢?

那就要从世界上第一台真正意义上的通用计算机 ENIAC 说起了……

它于 1946 年 2 月诞生在美国宾夕法尼亚大学,如下图:

那时还没有发明晶体管,ENIAC 主要使用近 18000 个电子管作为元器件,长 30.48 米,宽 6 米,高 2.4 米,占地面积约 170 平方米,30 个操作台,重达 30 英吨,耗电量 150 千瓦,造价 48 万美元。计算速度是每秒 5000 次加法或 400 次乘法,是使用继电器运转的机电式计算机的 1000 倍、手工计算的 20 万倍。ENIAC 的出现加快了人类向信息化社会迈进的步伐,是科学技术发展史上的里程碑。

但是由于电子管有着体积大、功耗大、发热多、寿命短、电源利用效率低、结构脆弱而且需要高压电源等缺点,随着计算量的增大,很快就不适合发展的需求。这促使了晶体管的发明。

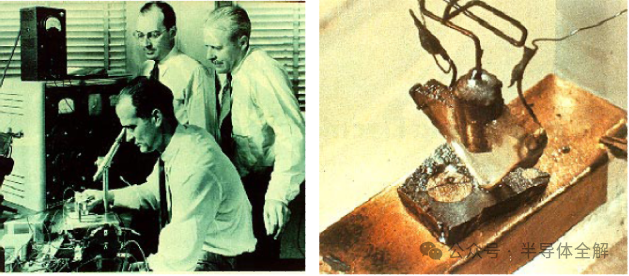

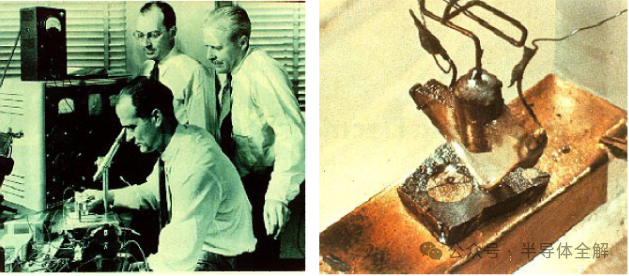

1947 年 12 月贝尔实验室的 William Shockley、JohnBarden 和 Walter Brattain 研制出一种点接触型的锗晶体管,下图中左边是研发出晶体管的三位大神,右图是世界上的第一个晶体管。

晶体管出现后,人们就能用一个小巧的、消耗功率低的电子器件来代替电子管了。为此,三位发明者获得了 1956 年的诺贝尔物理学奖。

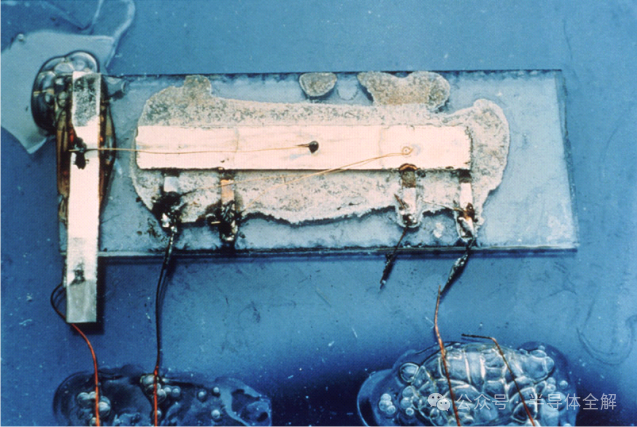

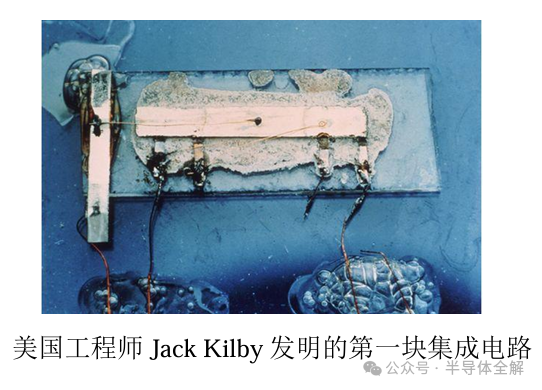

之后,英国雷达研究所的科学家 G.W.A.Dummer 在 1952 年的一次会议上提出,可以把电子线路中的分立元器件,集中制作在一块半导体晶片上,一小块晶片就是一个完整电路,这样电子线路的体积就可大大缩小,可靠性大幅提高。这就是最早的有关集成电路的构想。之后科学家又做了大量的工作,终于在 1958 年美国 Texas Instruments 公司的 Jack Kilby 在实验室实现了第一个基于锗晶体管的集成电路震荡演示实验,标志着集成电路的诞生。

Jack Kilby 也因此被授予 2000 年诺贝尔物理学奖,诺贝尔奖评审委员会对他的评价是:“为现代信息技术奠定了基础”。

二、什么是集成电路?

集成电路(integrated circuit) 是一种微型电子器件或部件,采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。

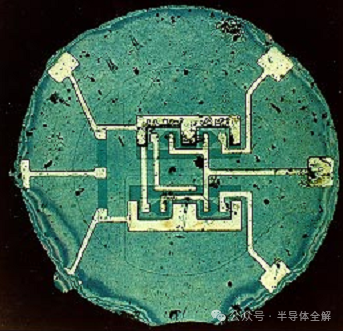

1952 年 5 月,英国科学家 Dummer 第一次提出了集成电路的设想。Intel 公司德诺宜斯 (Robert Noyce) 发明了 IC 的单晶制造概念,全球第一块单晶制造的集成电路就是下图这样:

集成电路因为其具有的突出优点,如重量轻、体积小、引脚少、使用寿命长、高可靠性、性能好且成本低等,自发明之后便得到了广泛的应用。按照其功能和结构的不同,可以分为模拟集成电路,数字集成电路和数 / 模混合集成电路;按照用途可以分为电脑用集成电路(包括中央微处理器、内存储器、外存储器、I/O 控制电路等)、通信用集成电路、遥控集成电路、语言集成电路、报警器用集成电路及各种专用集成电路等。

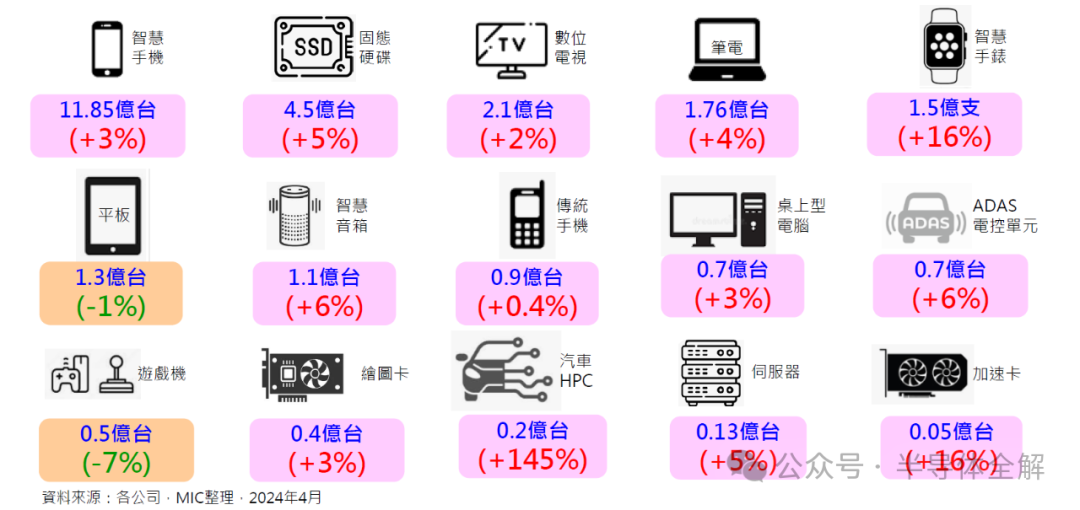

下图是相关机构对 2024 年电子产品销量及对集成电路的需求预测。

随着时间的推移,在应用需求的强烈驱动下,集成电路的集成密度突飞猛进。1965 年,Intel 公司创始人之一 Gordon Moore 在整理数据时发现了一个惊人的趋势:芯片集成的晶体管的数量每年增加一倍。他把这一现象发表在题为 “Gramming More Compnents Onto Integrated Circuits” 的报告中,这就是著名的摩尔定律。后来根据集成电路的实际发展情况,在 1975 年 IEEE 电子组件大会上,Moore 把 “每年增加一倍” 修改为 “每两年增加一倍”。在此基础上,Intel 首席执行官 David House 又将时间周期改为 18 个月。现在一般把摩尔定律表述为 “集成电路上可容纳的晶体管数目,大约每隔 18 个月便增加一倍”。

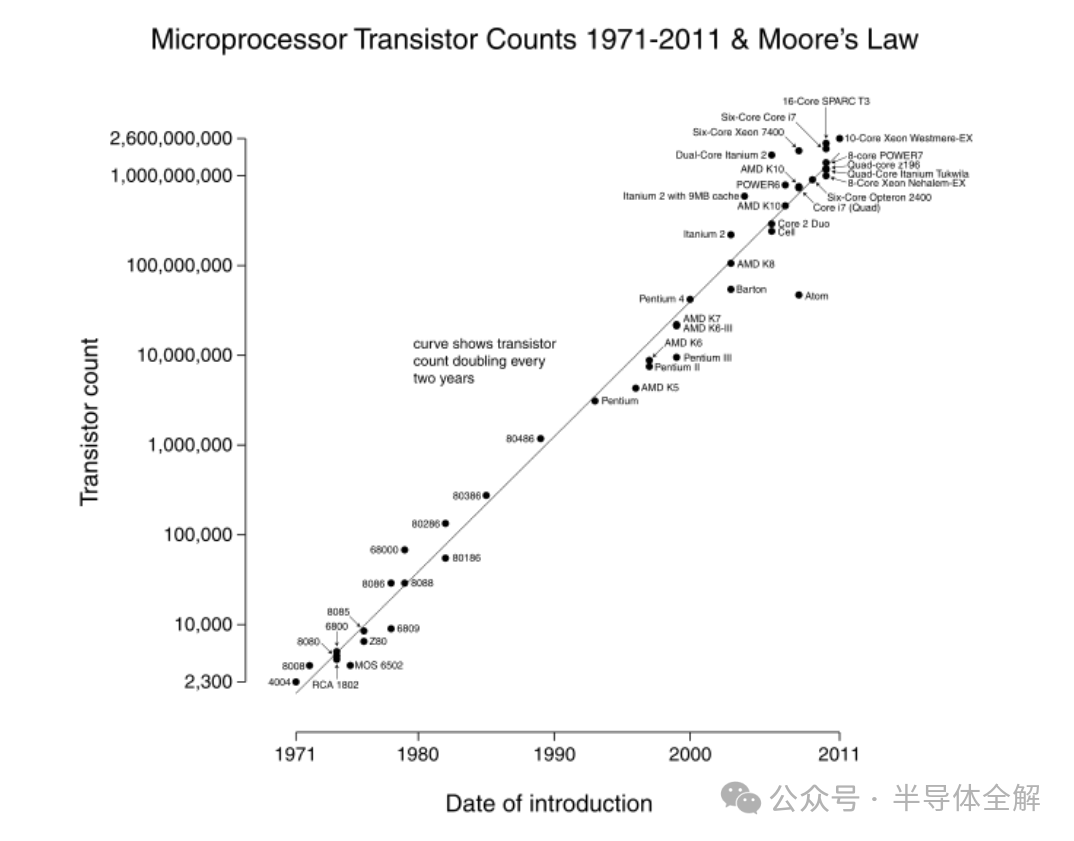

虽然摩尔定律最初是对集成电路发展趋势的归纳总结,但自其提出后,随着其预言不断的获得验证,它反过来开始牵引整个集成电路行业的发展,引导着半导体产业长期规划和目标设定。目前半导体集成电路产业的发展基本上遵循着摩尔定律,下面均以电脑用集成电路中的中央微处理器(Centrol Processing Unit,CPU)为代表来介绍集成电路的发展。从 1971 年至 2011 年,单个 CPU 上晶体管数量与摩尔定律的关系如图所示。

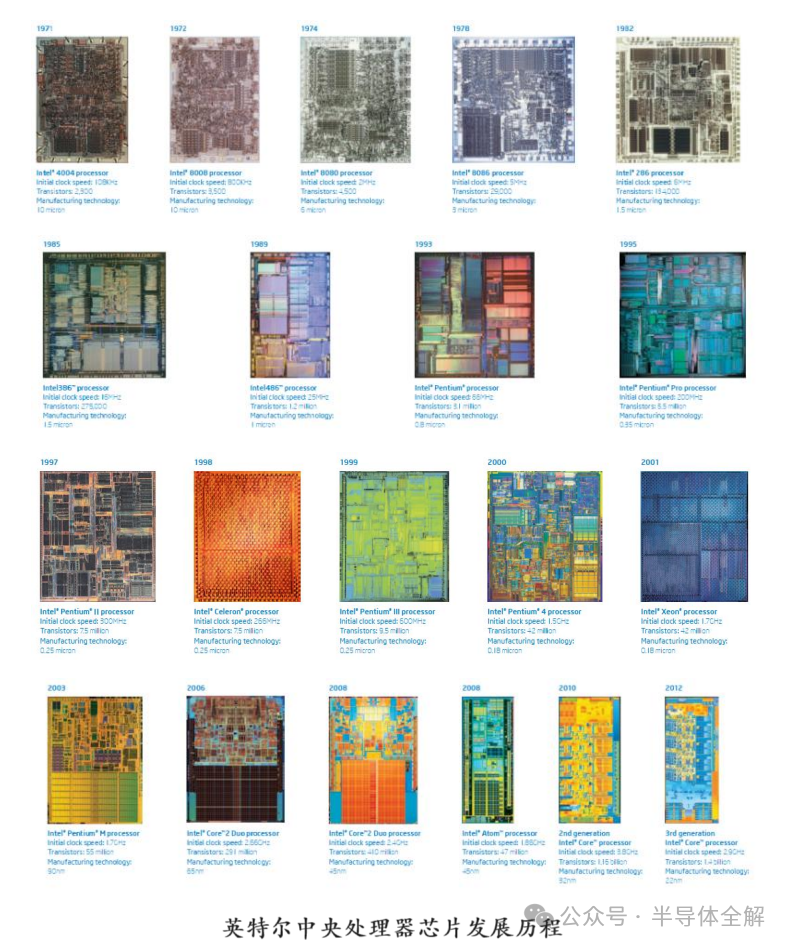

Intel 公司的 CPU 发展历程如下图所示。

从上图可以看出,单个微处理器上集成的晶体管数量增长规律和摩尔定律所预测的基本一致。

具体来看,1971 年 Intel 开发出第一代也是世界上第一个微处理器芯片 4004,采用的是 10μm 工艺,包含了 4 个芯片,2300 个晶体管。到 2012 年,在 Intel 采用 22nm 工艺的通用中央微处理器上集成的晶体管数量已经达到了 14 亿个,增长超 60 万倍。

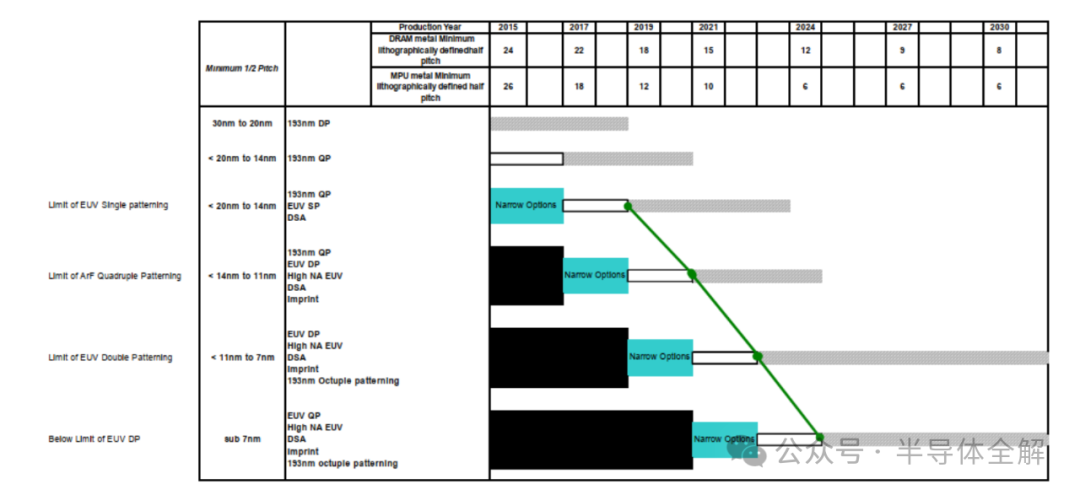

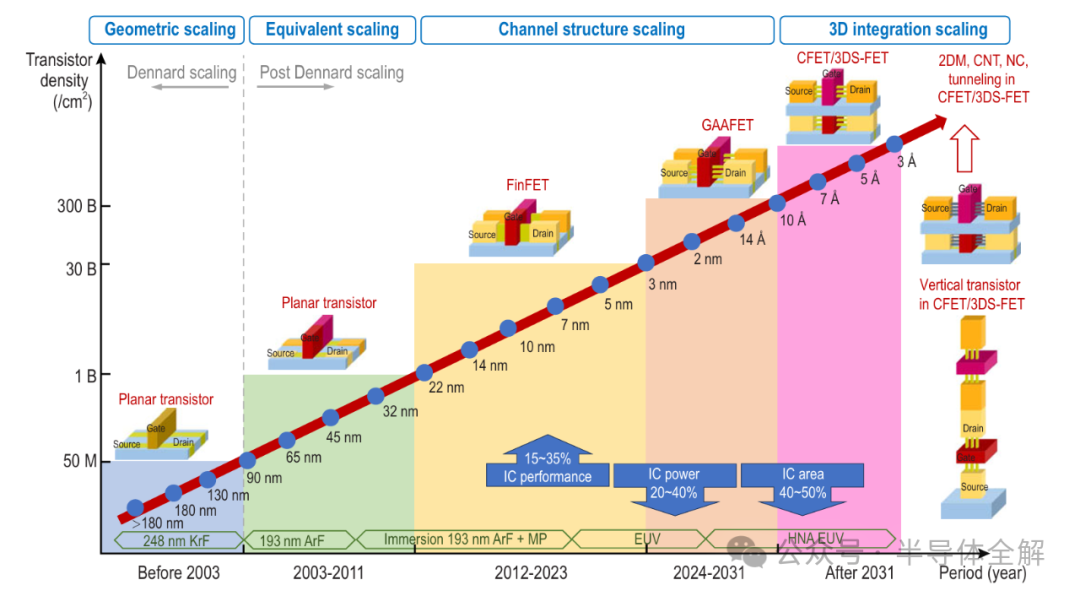

集成数量的增加主要归功于晶体管关键尺寸的减小。关键尺寸(CD,critical dimension)是指半导体器件中的最小尺寸。这种最小尺寸往往就是最小刻线的宽度,即俗称的 “线宽”,也被称作为节点(node)。对于典型的密集线(dense line)图形来说,CD 就是密集线周期(pitch)的一半。通常来说,特征尺寸越小,芯片的集成度越高,并且功耗也越低,性能相应的会更好。从这方面来说,采用 CD 来评价集成电路的性能更有意义。半导体国际技术路线图 ITRS(INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS)就是采用 CD 作为主要指标来对集成电路行业的为未来进行规划。下图是 2015 年的半导体技术路线图,基本上符合上述特征尺寸的要求。

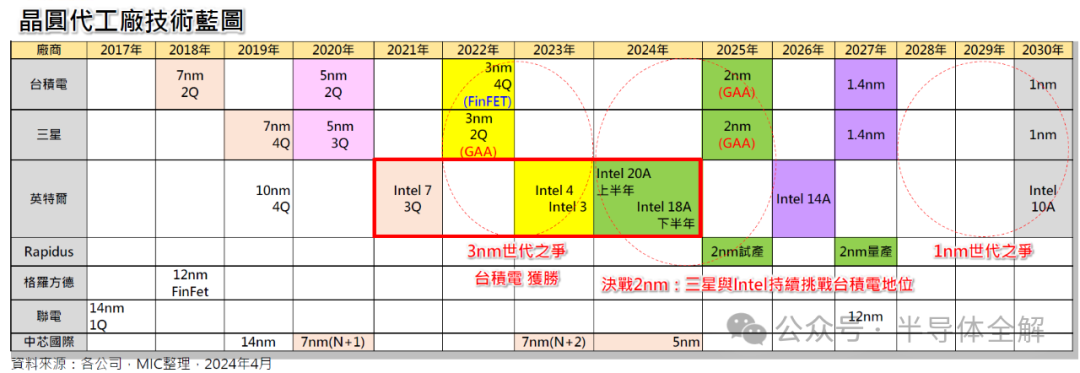

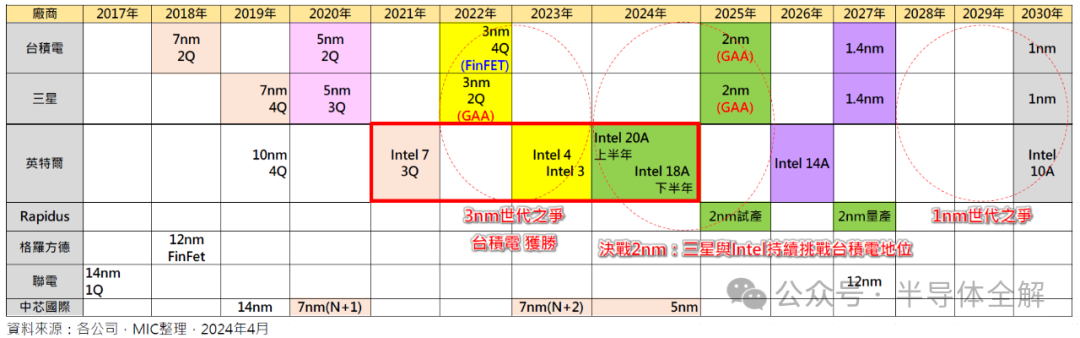

实际上,工业界的进展往往要快于 ITRS 的规划,例如半导体代工巨头台积电公司(TSMC)已经在 2018 年实现了 7nm 工艺的量产,并且在 2020 年下半年就实现 5nm 工艺量产,2022 年进入到 3nm 时代,即将进入到 2nm 时代!

同时也需要看到,随着节点越来越小,摩尔定律也逐渐逼近极限,摩尔定律失效的呼声越来越高,学者们提出了 “More than Moore” 和 “beyond CMOS” 来预测半导体集成电路的发展。无论集成电路技术发展的终点如何,摩尔定律对集成电路发展的贡献是巨大的。

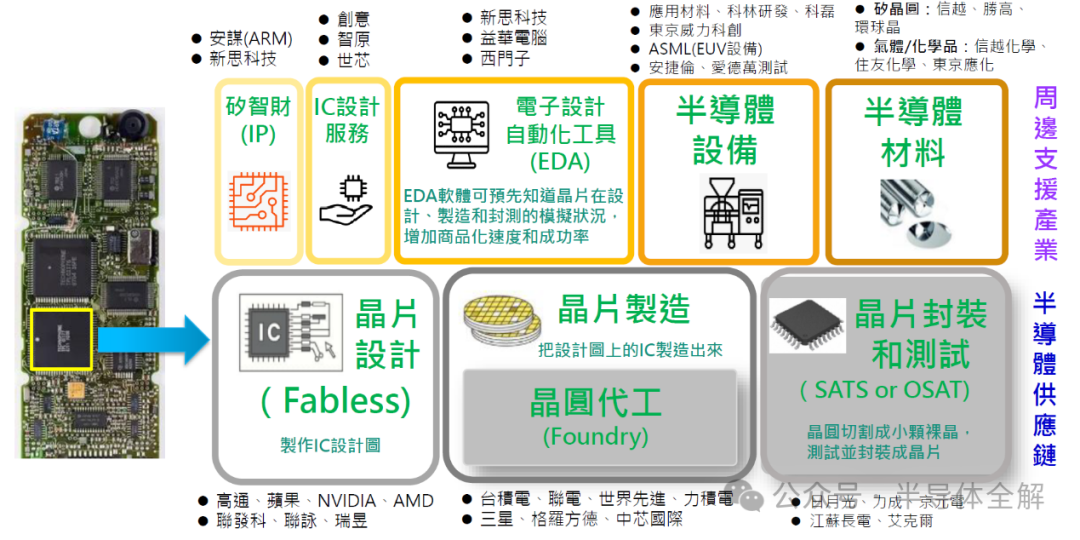

伴随着集成电路发展的是集成电路的制造工艺。在过去几十年里,集成电路的制造取得了巨大的进步。大规模集成电路的制造是一件极为复杂的事情,包括非常复杂的物理、化学工序。主要分为 5 个阶段:晶圆(wafer)的制备、芯片的制造、芯片的检测、芯片的封装和验收测试,整个产业链涉及非常广泛。

三、光刻技术发展历程

其中用于芯片制造的光刻技术的持续改进是关键。改进的主要推动力是降低集成电路中每单元功能的成本,这就需要提高制造设备的分辨率和生产效率,从而使得单位时间内能集成更多的晶体管。

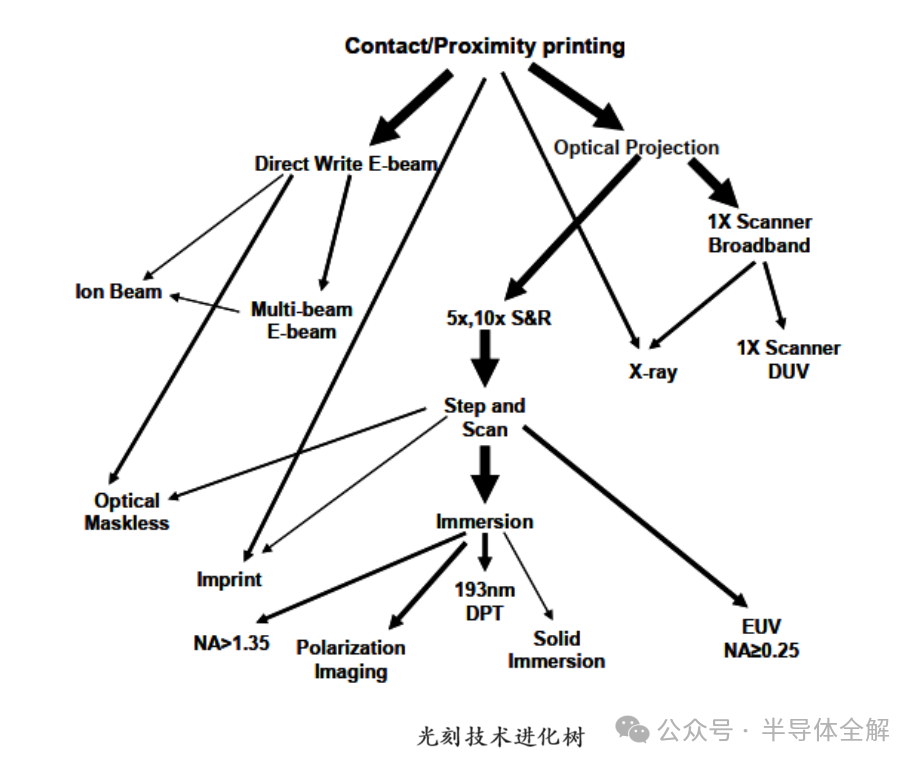

下图给出了光刻技术演进的示意图。

最早的光刻技术是接触式印刷,主要应用于 1960 年至 1975 年,它相对比较简单,通过光照使得掩模图案直接曝光在基底上,但是缺点也很明显,接触曝光容易破坏基底和昂贵的掩模。所以随后发展出了直写光刻技术和投影光刻技术。直写光刻不需要掩模,精度高,但是效率低,通常用于制造掩模,不适合工业量产。而投影光刻技术通过光学成像将掩模图案曝光在晶圆上,产率很高,是目前工业界主要的光刻技术。

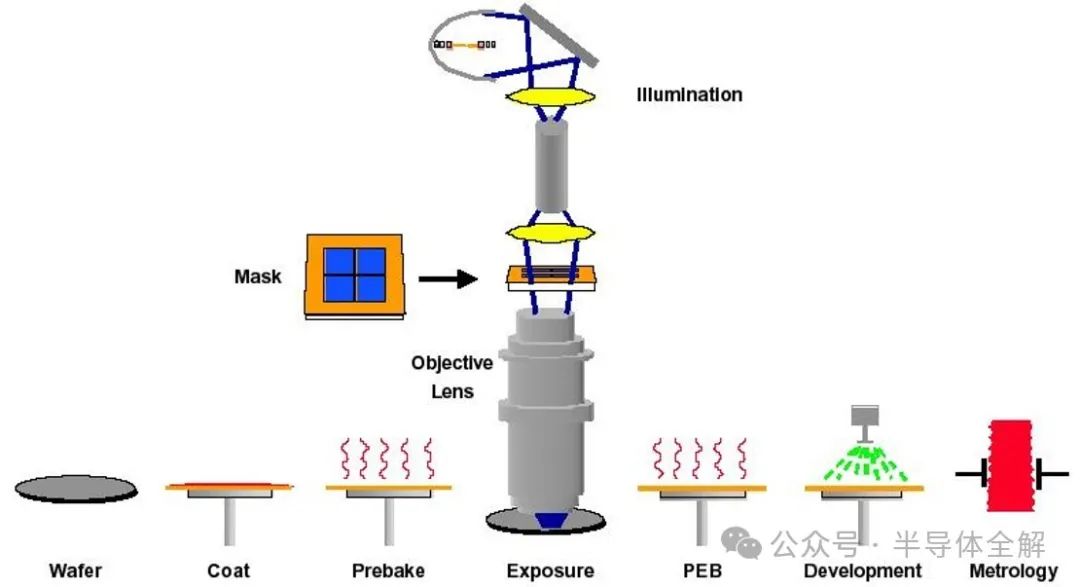

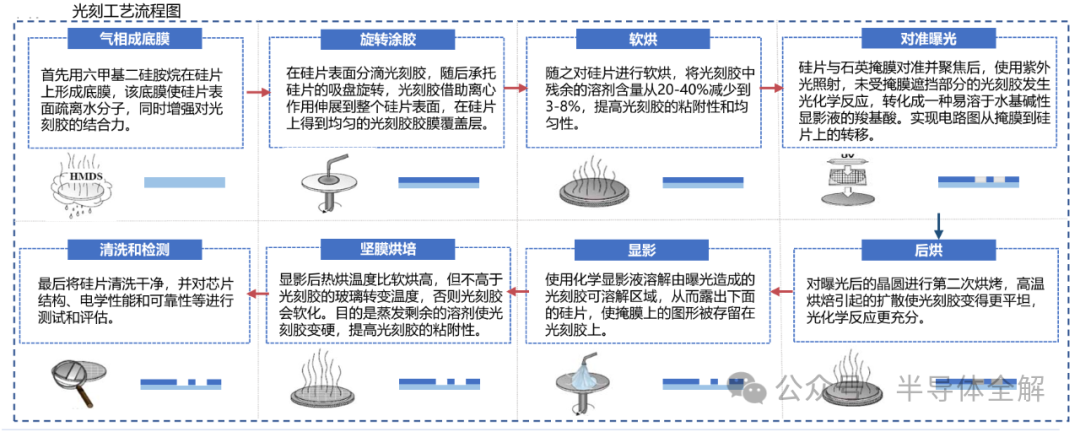

光刻工艺是指将包含电路信息的掩模图形经投影物镜精确地转移到涂覆有光刻胶的硅片上的过程。典型的光刻工艺包括硅片预处理、旋涂光刻胶、软烘、对准 / 曝光、曝光后烘、显影、刻蚀 / 离子注入和去胶等步骤。

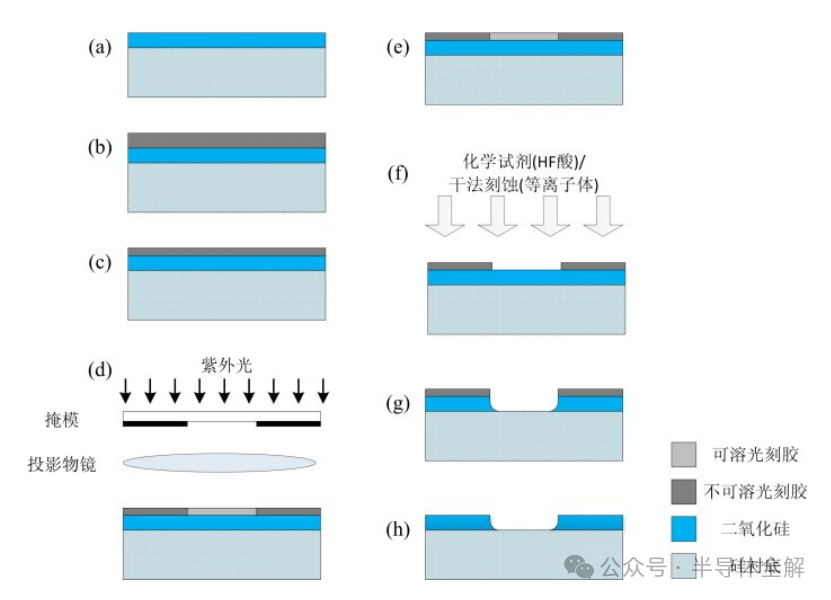

下图为正胶在硅片上产生二氧化硅窗口的光刻工艺流程,图中对应的工序如下:

(a) 预处理,(b) 涂胶,© 前烘,(d) 对准曝光,(e) 曝光后烘,(f) 显影,(g) 刻蚀,(h) 去胶。

下面对光刻工艺各步骤进行说明:

预处理(Prepare Wafer):在涂抹光刻胶之前对硅衬底进行处理,包括脱水烘焙,涂抹化合物增加衬底表面附着能力等;

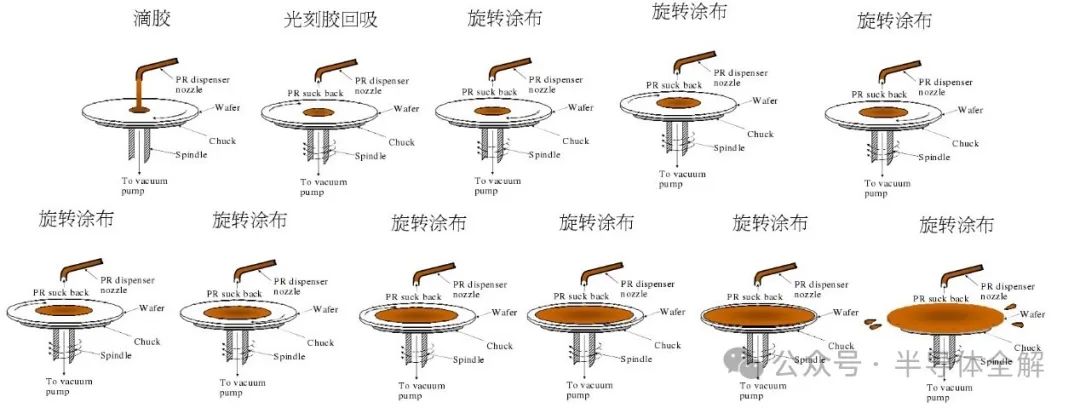

涂胶(Coat with Photoresist):将光刻胶平整、均匀地涂抹在硅衬底表面;

前烘(Prebake):对于液态的光刻胶,杂质容易污染溶剂,通过在较高温度下烘焙,使溶剂挥发;

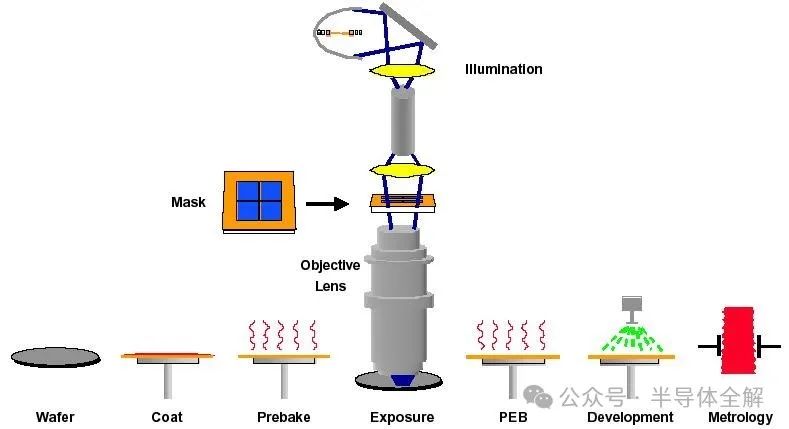

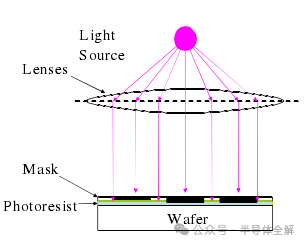

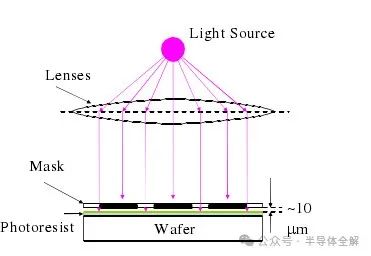

对准与曝光(Align and Expose):通过掩模和硅片上的标记等实现两者之间的严格的位置关系,然后通过投影曝光的方式将掩模板的图案精确地成像在硅片上,实现光刻胶的曝光,如下图所示。

后烘(Post-exposure Bake):再次烘焙,目的是减少驻波效应,激发化学反应使正光刻胶更易溶于显影液;

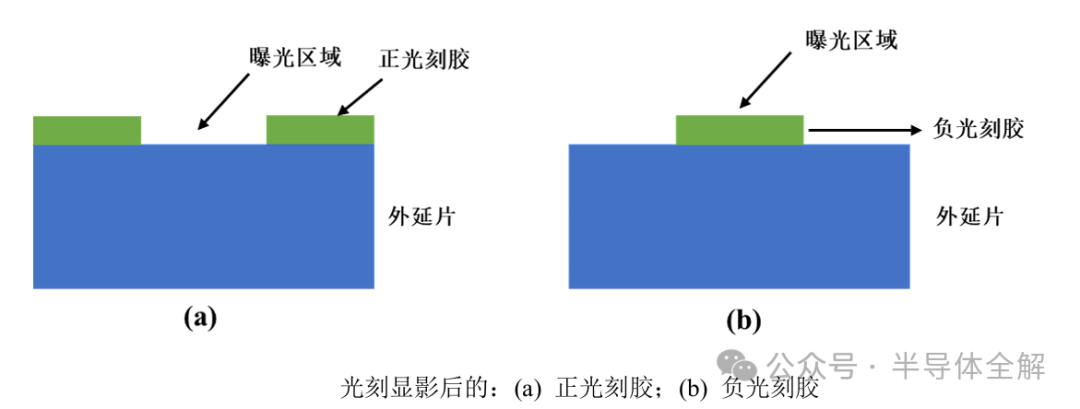

显影(Develop):曝光和后烘流程结束后,便加入显影液。显影液会和正光刻胶的感光区、负光刻胶的非感光区发生化学反应。

显影完成后,光刻胶层中的图案便显现出来。实际工艺中为了保证高质量的显影效果,每一种光刻胶几乎都有专门适配的显影液,这样成像质量和分辨率会提高;

刻蚀与掺杂(Etch and Implant):对硅晶上无光刻胶遮蔽的区域进行刻蚀和离子注入,完成掩模板图案到硅片的转移;

去胶(Strip Resist):去除光刻胶层。

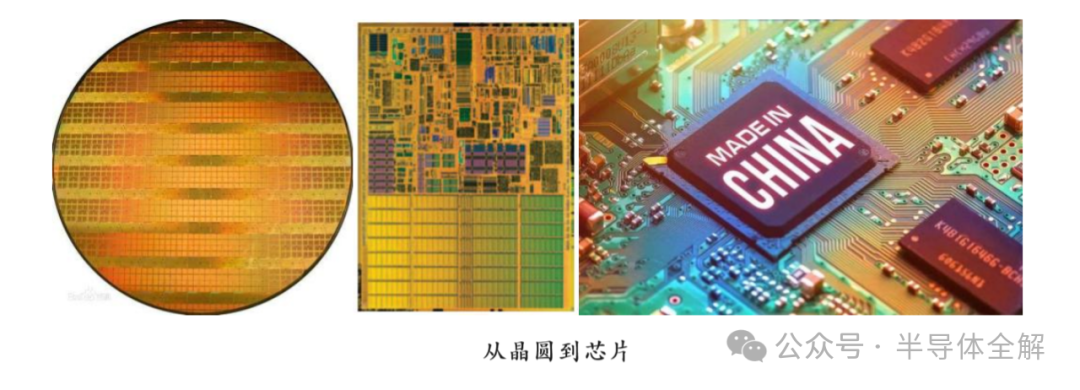

经过上述一系列工序后,芯片便制造完成了,再经过后续一系列的检测,切割和封装等工序,就可以提供给用户使用了,如下图所示。

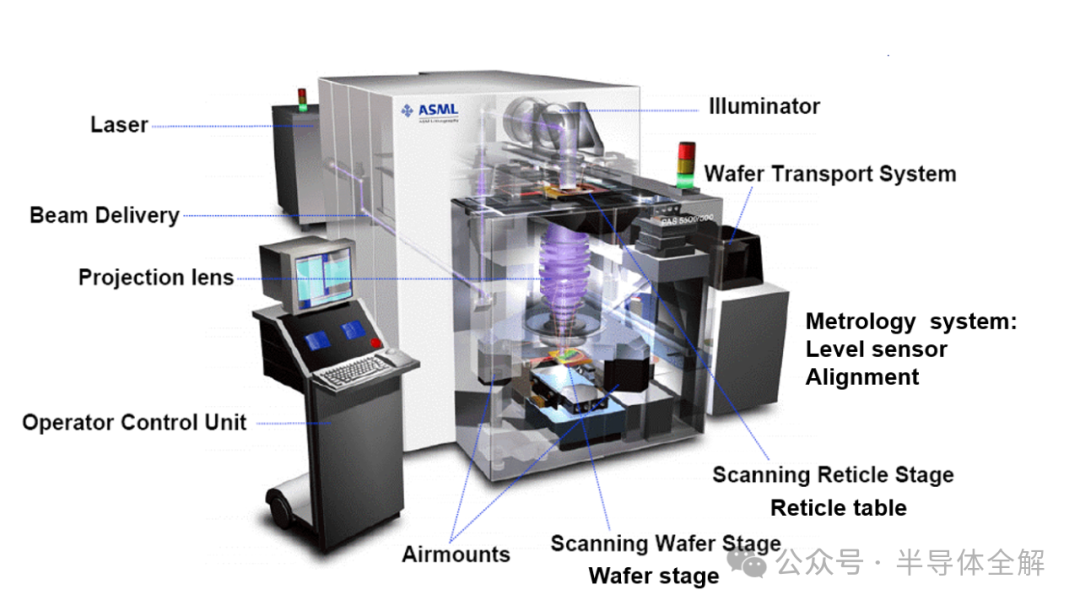

上节所述芯片制造过程需要用到的设备有很多,包括氧化炉,涂胶显影机,化学机械抛光机,清洗机,薄膜沉积设备,光刻机,刻蚀机,离子注入机,前道检测设备以及减薄机,划片机,引线键合机和后道测试设备等。其中用于曝光的光刻机是芯片制造的核心设备,单台成本最大,技术含量最高,涉及精密光学,精密机械,精密运动控制和精密环境控制等学科,并且几乎每个学科到需要达到当时技术的极限,因此光刻机被誉为半导体工业皇冠上的明珠。

目前国际上主流的光刻机制造商有荷兰 ASML 公司、日本 Nikon 公司、和日本 Canon 公司,其中 ASML 公司的照明系统和投影物镜是由德国的 Zeiss 公司提供。

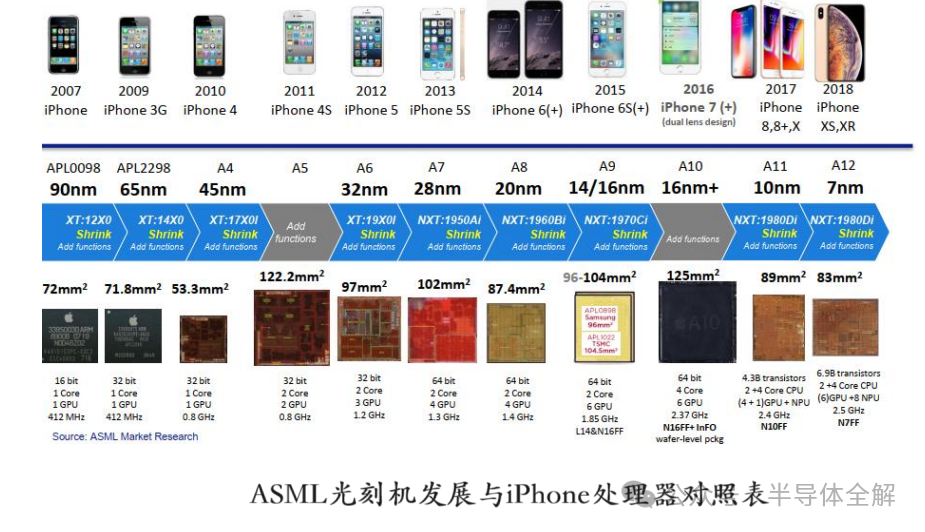

国内的上海微电子装备股份有限公司(SMEE)也能够制造中端步进扫描投影光刻机,但对于 14nm 及以下节点的半导体制程,目前只有 ASML 的光刻机用于芯片的大规模生产。随着集成电路制造要求的提高,光刻机越来越复杂和精密,光刻机的发展和技术水平很大程度上决定了集成电路的发展和技术水平,下图给出了 ASML 公司的光刻机发展与苹果公司微处理器在 2007 年 - 2018 年的对应关系,目前 iPhone 15 Pro 系列采用了最新的 A17 Pro 芯片,已来到成熟的 3nm 制造工艺。

四、光刻机结构简介

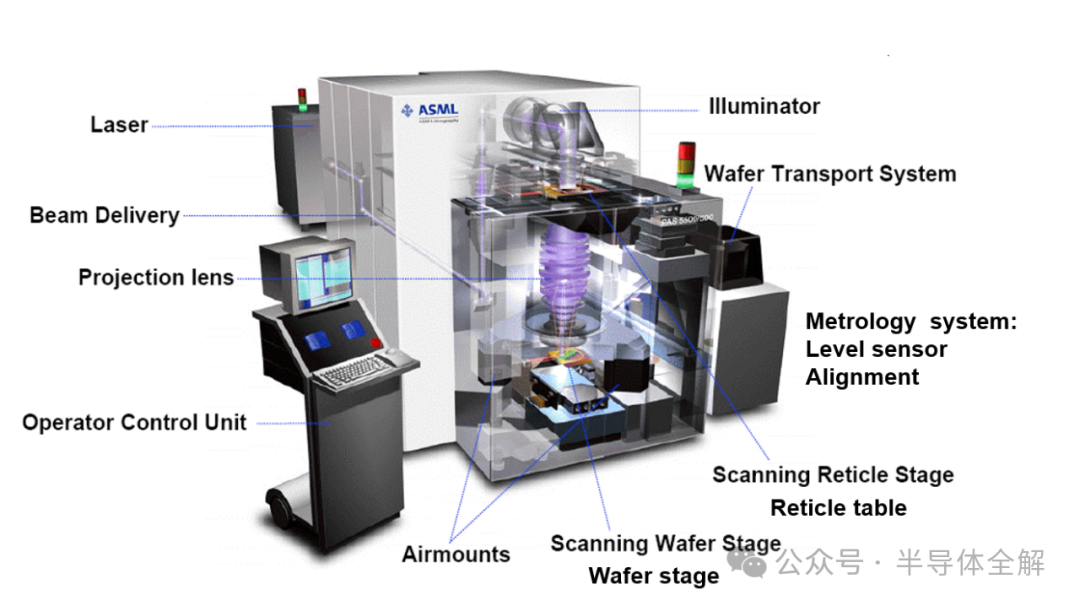

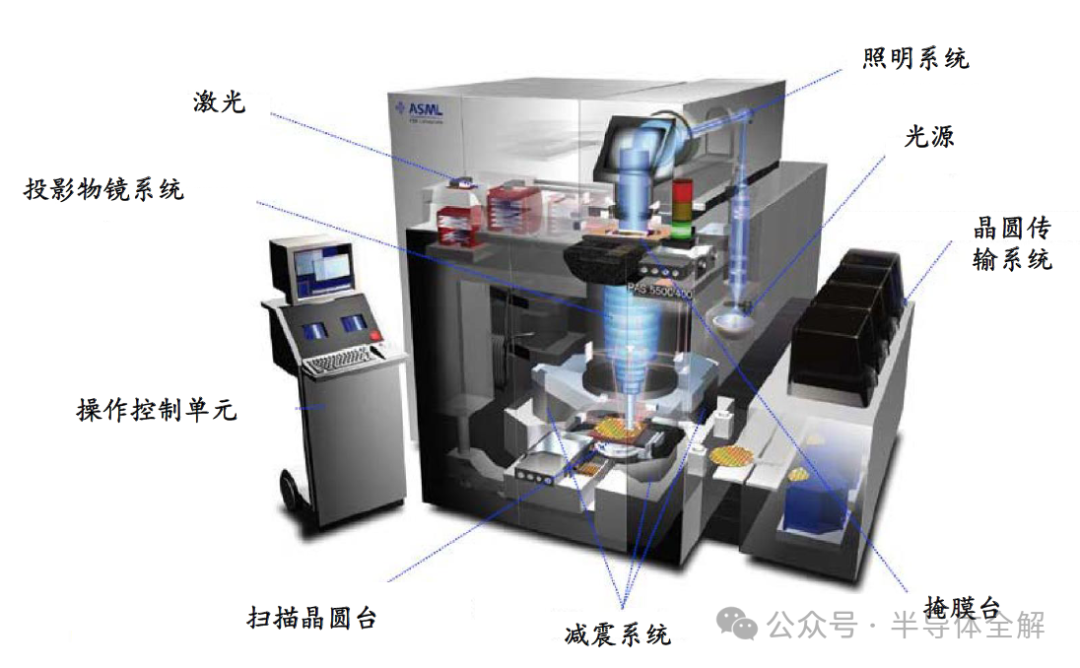

投影光刻机主要由以下几个部分组成:光源、照明系统、掩模台、掩模传输系统,投影光刻物镜、工件台、硅片传输系统,对准系统,调平调焦系统,环境控制系统,整机框架和减振系统,整机控制系统和整机软件等,如下图所示:

其中照明系统和投影物镜又统称为曝光系统(exposure system)。

光刻机的主要评价指标有 3 个,分别是线宽(CD),套刻精度(overlay)和产率(throughput),其中产率又和投影物镜的曝光视场(field size)密切相关。

线宽前文已经介绍过,套刻精度是指硅片上后一次曝光的图形相对于前一次曝光的图形的定位精度,产率一般是指光刻机每小时生产的硅片数量(wafer per hour)可以理解为设备产能,而曝光视场指单次曝光的芯片的大小。

这些项指标均与投影光刻物镜的性能密切相关,特别是线宽代表了集成电路的工艺水平,直接由投影光刻物镜的性能决定,因此投影光刻物镜是光刻机的核心部件,其发展和技术水平又在很大程度上代表了光刻机的发展和技术水平。

在摩尔定律的驱动下,对每个芯片的集成晶体管的数量要求越来越高,这在分辨率不断提高的同时,也要求芯片面积尽可能增加。这样对投影物镜的倍率要求又提高了,随着节点的缩小和芯片尺寸的进一步增加,投影物镜的难度是越来越大了。

这最终促成了光刻机工作原理和结构发生翻天覆地的变化!

由于光刻机发展历程较长,设备结构变化大,光刻机工作原理将在下一个章节中进行介绍!

参考文献:

(1) 尚红波 浸没光刻投影物镜光学设计与像差补偿研究 [D].

(2) 刘志帆 深紫外光刻机照明系统关键检测技术研究 [D].

(3) 李雪平 面向光刻机浸没系统设计的介观尺度流场扰动解析与抑制方法研究 [D].

(4) 彭茂荣 2024 年半导体产业发展议题 [C].

详解光刻机进化史

原创 圆圆 De 圆 半导体全解

一、集成电路生产流程

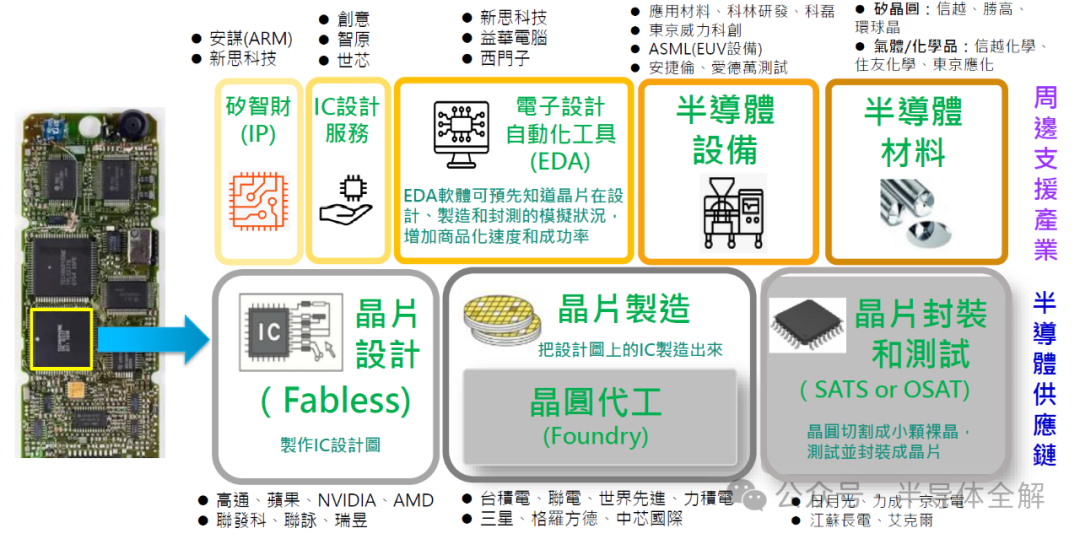

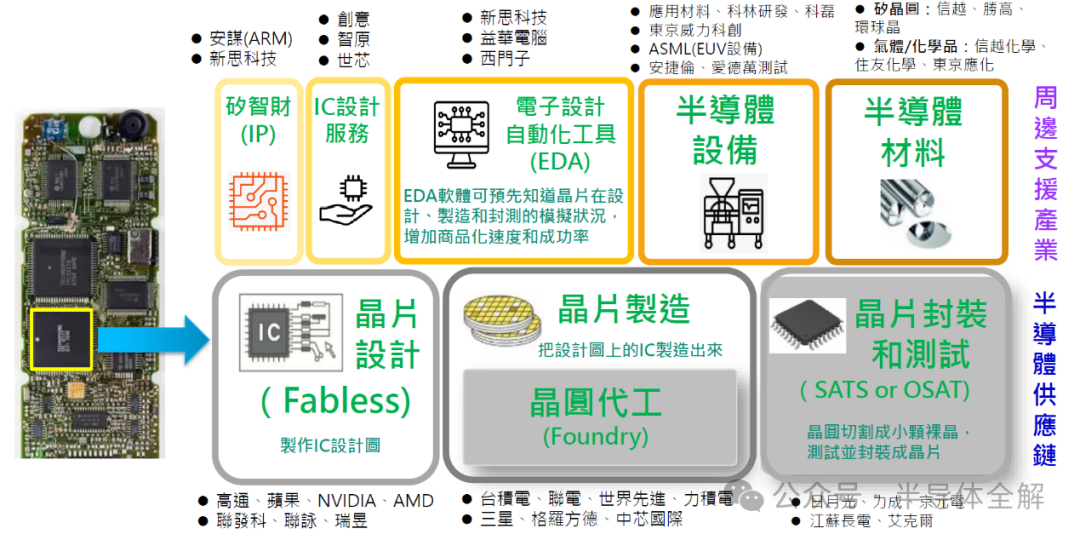

集成电路的生产过程可分为设计、制造和封装测试三个阶段。

其中,集成电路制造决定了集成电路的集成度和特征尺寸。集成电路制造主要分为硅片制 备、硅片制造、硅片测试、装配与封装和终测五个步骤。

硅片制备是通过一系列工艺从石英沙中提炼出高纯度单晶硅锭,得到可用于制造集成电路的硅片。作为集成电路的基底材料,硅片的几何尺寸、表面粗糙度和表面洁净度等因素都会影响集成电路的制造成本。

常见的硅片直径有 6 英寸(150 mm)、8 英寸(200 mm)、12 英寸(300 mm)等规格。

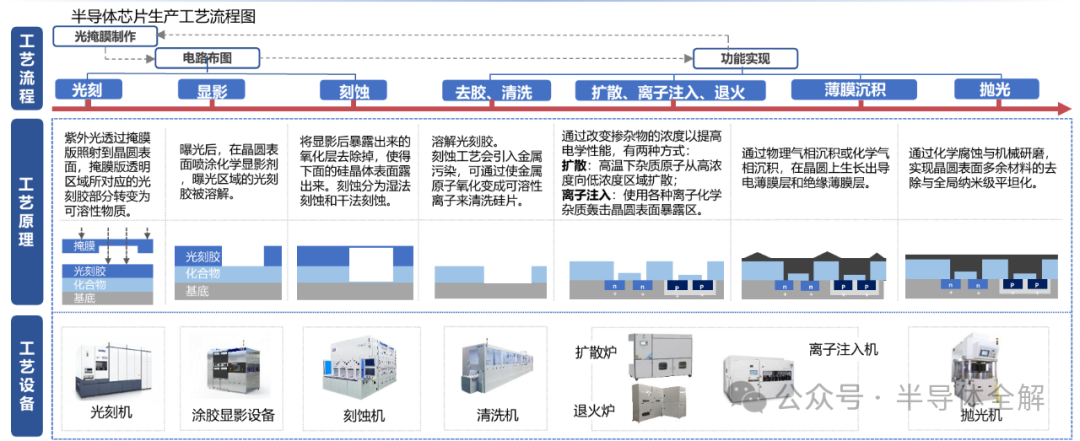

硅片制造过程中涉及到多种工艺的交互操作,如外延沉积、化学 / 物理气相沉积、光刻、刻蚀、离子注入、热处理等。通过上述工艺的交互组合,将集成电路每一层对应的设计图形依次转移到硅片基底上,从而形成芯片的三维微细结构。

硅片测试是指对硅片上每个芯片单元进行电学测试,筛选出合格和不合格的芯片,并作相应的标记。

装配和封装过程将标记为合格的芯片包装在特定的保护管壳内,以提高芯片的抗污能力和连接性能。

为保证芯片满足设计所需要的电学功能和环境要求,完成封装的芯片还需要进行出厂前的终测。

光刻机是极大规模集成电路 (IC) 产业中具有战略意义的制造装备。作为超精密制造领域最高水平的象征,被誉为 “工业皇冠上的明珠”。

光刻机的基本工作原理是在特定剂量的紫外光照射作用下,通过投影物镜将掩模版上放大的图案投影于涂有光刻胶的硅片上,因被照射部分的光刻胶起到刻蚀作用而最终在硅片上实现设计的电路。

二、光刻机设备简介

光刻机主要由以下几个部分组成:光源、照明系统、掩模台、掩模传输系统,投影光刻物镜、工件台、硅片传输系统,对准系统,调平调焦系统,环境控制系统,整机框架和减振系统,整机控制系统和整机软件等,如下图所示,

其中照明系统和投影物镜又统称为曝光系统(exposure system)。

光刻机的主要评价指标有 3 个,分别是线宽(CD),套刻精度(overlay)和产率(throughput),其中产率又和投影物镜的曝光视场(field size)密切相关。

套刻精度是指硅片上后一次曝光的图形相对于前一次曝光的图形的定位精度,产率一般是指光刻机每小时生产的硅片数量(wafer per hour)可以理解为设备产能,而曝光视场指单次曝光的芯片的大小。

视场和线宽这两项指标共同决定了投影物镜能够传递的信息容量,也决定了投影物镜的难度和复杂度。这些项指标均与投影光刻物镜的性能密切相关,特别是线宽代表了集成电路的工艺水平,关键尺寸(CD,critical dimension)是指半导体器件中的最小尺寸。这种最小尺寸往往就是最小刻线的宽度,即俗称的 “线宽”,也被称作为节点(node)。

三、光刻机关键参数

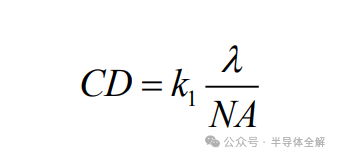

分辨率决定了光刻机可以加工的最小线宽(CD)(也称为分辨率,resolution),是光刻机最主要的性能指标,其计算公式为:

其中 k1 是工艺因子, λ 是工作波长,NA(numerical aperture)是投影物镜的数值孔径。显然提高光刻机的分辨率需要从三个方面考虑,即缩短波长,增大数值孔径和降低工艺因子。

整个光刻机的发展历程基本上也是围绕着这三个因素开展。

工艺因子的降低主要通过投影物镜像差的减小和分辨率增强技术来现。目前 k1 已经越来越接近极限 0.25 了。

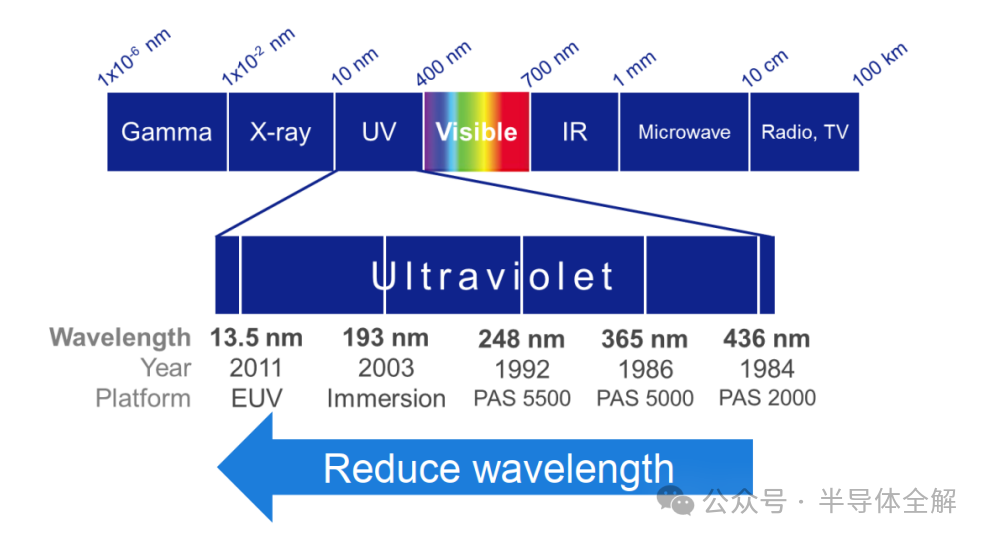

波长的缩短经历了 g 线(436nm)、i 线(365nm)、KrF(248nm)、ArF(193nm)和 EUV。其发展如下图所示。

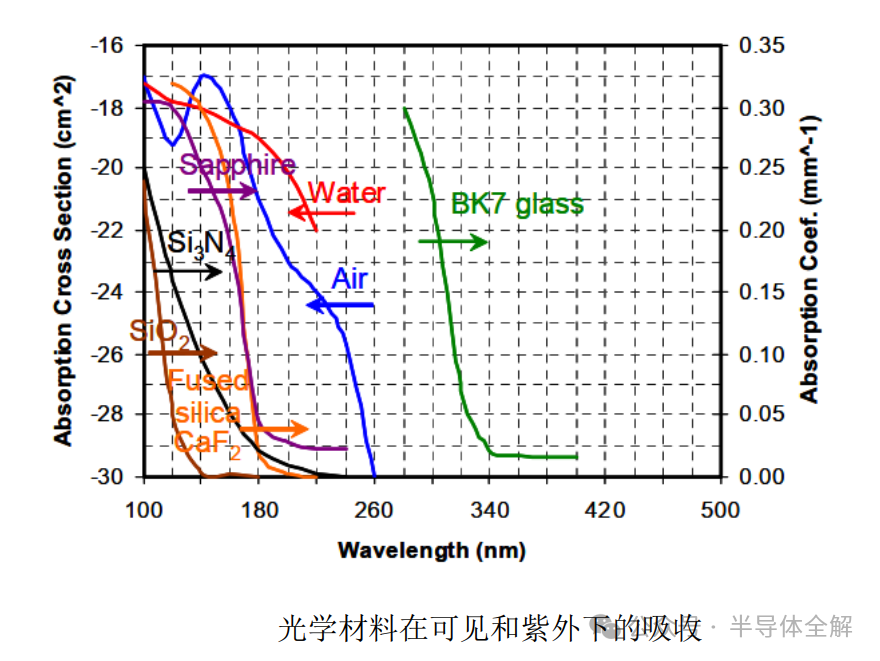

波长的缩短过程中也面临着很多的问题和挑战,包括光学材料,光刻胶材料,光源和投影物镜的设计等。通常这些因素互相耦合和制约,比如随着波长的缩小,光学材料的吸收变大,可以选择的材料类型就减少,这样投影物镜的色差校正就很困难,可能需要采用成本更高的折反射式方案或者降低光源的线宽,而线宽的降低又对光源提出了很高的要求。对于 KrF 和 ArF 波长,可以选择的材料只有合成石英(fused silica)和氟化钙(CaF2)了,如下图所示,这就要求准分子激光器保证一定功率的前提下又要实现非常窄的线宽。

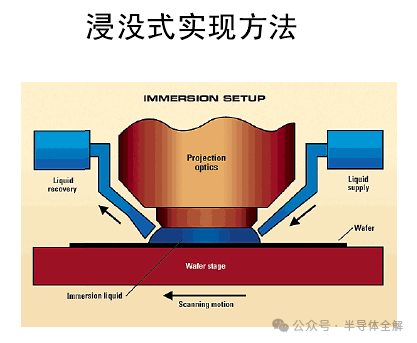

在波长下不断缩短的同时,投影物镜 NA 也在不断的增加,从 20 世纪 80 年代的 NA0.2 左右一直发展到 21 世纪 10 年代的 NA 1.35。数值孔径超过 1 后就需要采用像方浸液设计了,即所谓的浸没物镜(immersion lens)。到现在为止采用的液体是水,实现的最大 NA 是 1.35。虽然也有很多其他浸没介质的研究,但是都因为各种各样的原因不满足实际的使用要求。

四、浸没式光刻机介绍

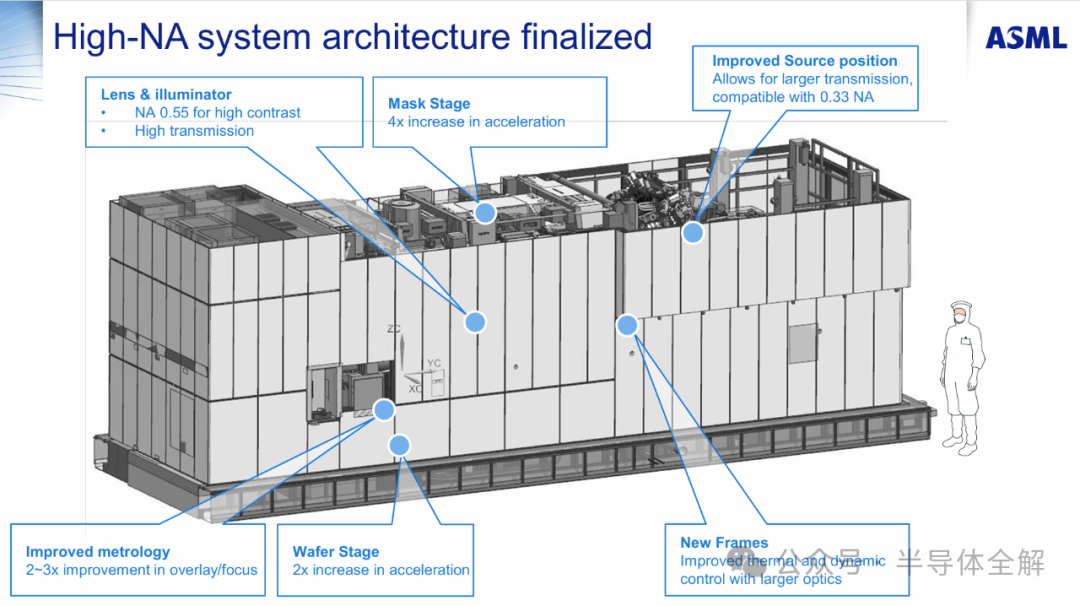

浸没式光刻机是光刻机发展的一个重要转折点,将传统光刻技术中投影物镜镜头与硅片之间的空气介质更换为折射率更大的液体介质以增加数值孔径 NA,使之最大可至 1.35,在继承 193nm 光源干式光刻技术的同时提高光刻的分辨率和焦深。

2007 年 ASML 首先推出了 193nm 光源的浸没式光刻机,成功将分辨率从 90nm 降低至 65nm 以下节点,使其成为 45nm 至 7nm 之间技术节点的主流光刻设备,且相关技术还在持续完善更新中。

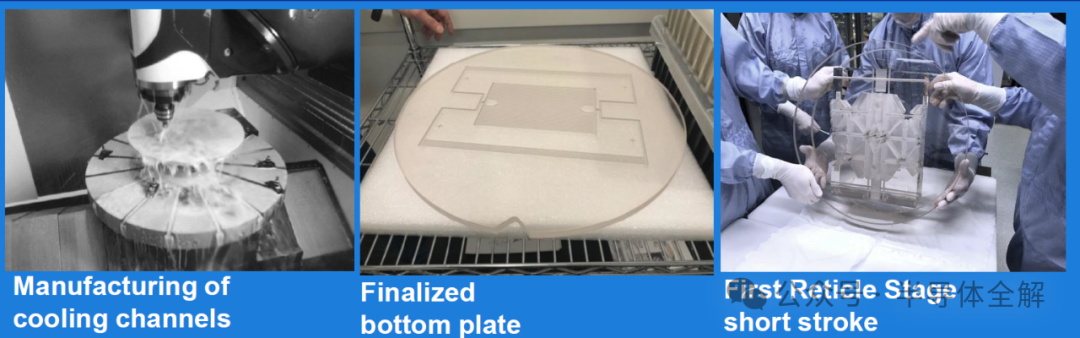

目前,浸没式光刻机的研发是我国光刻机研发征程中亟待攻克的技术难题。

28nm 及以下节点光刻机对曝光系统和定位系统的振动要求极为严苛,其内部世界的超稳定振动环境在 10E-10 (m/s2 ) E2 /Hz 量级,需要辨识出所有的扰动源并尽可能消除或者抑制振动以保证光刻机内部的超稳定环境。

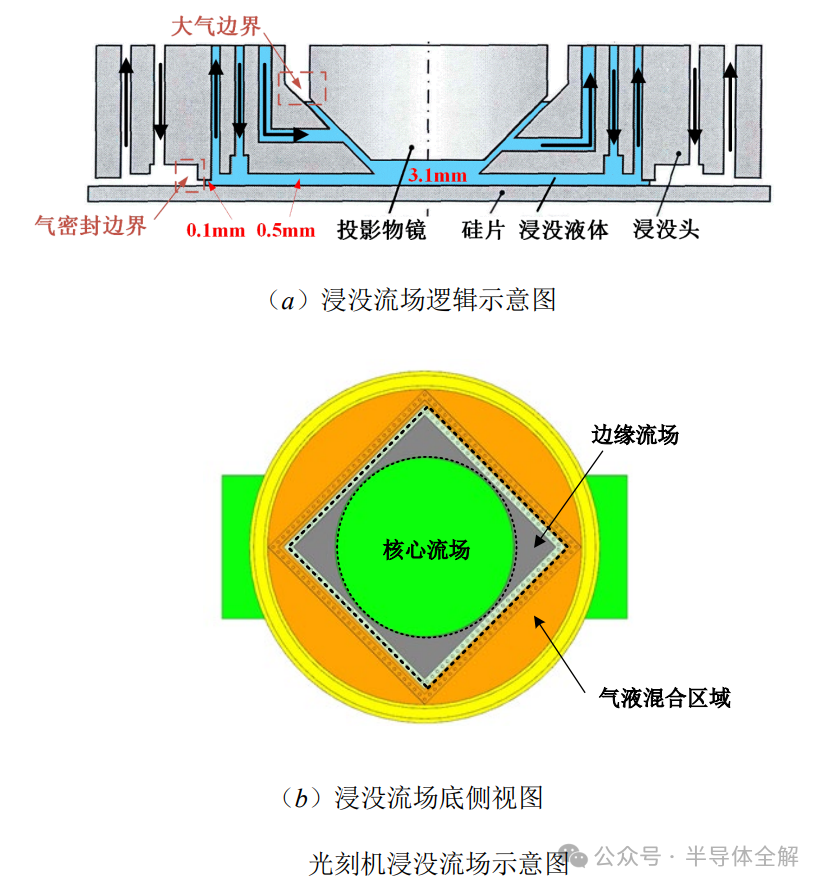

浸没式光刻机通过在投影物镜与硅片之间引入浸没液而提高了分辨率,但为了实现流场密封效果,在硅片和浸没头之间存在百微米级膜厚的浸没液,目前国外掌握浸没式光刻技术的两大公司为 ASML 公司和尼康公司,其浸没单元设计主要差异为 ASML 公司在浸没单元内部采用了注气结构,水平注液回收结构及垂直回收孔形状和排布等方面也略有不同,由于技术封锁,未公开相关技术细节。目前国内浸没式光刻中浸没流体控制结构的主要机构是浙江大学流体控制与机电系统国家重点实验室,经过数年的技术攻坚和积累,对产品进行了更新迭代,掌握了相关的核心技术,所研发的不同结构浸没单元形态如图所示。

五、光刻机发展历程

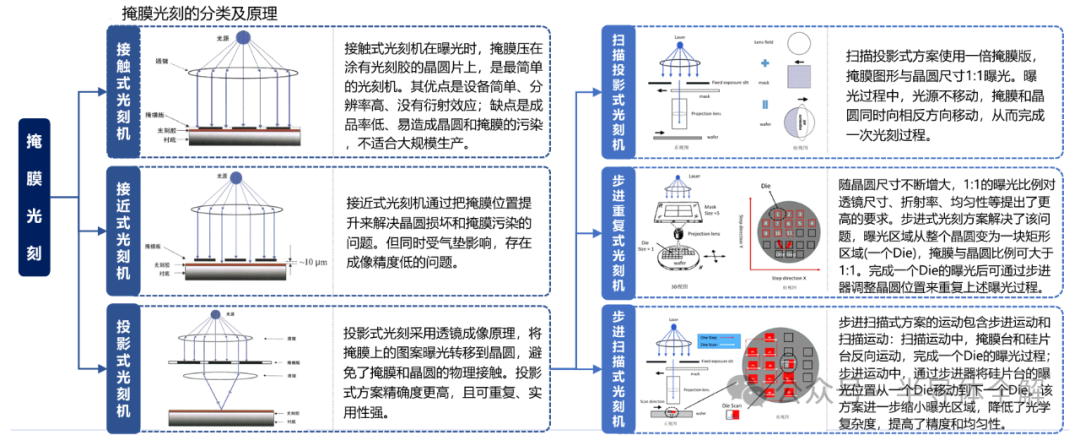

(1) 接触式光刻机

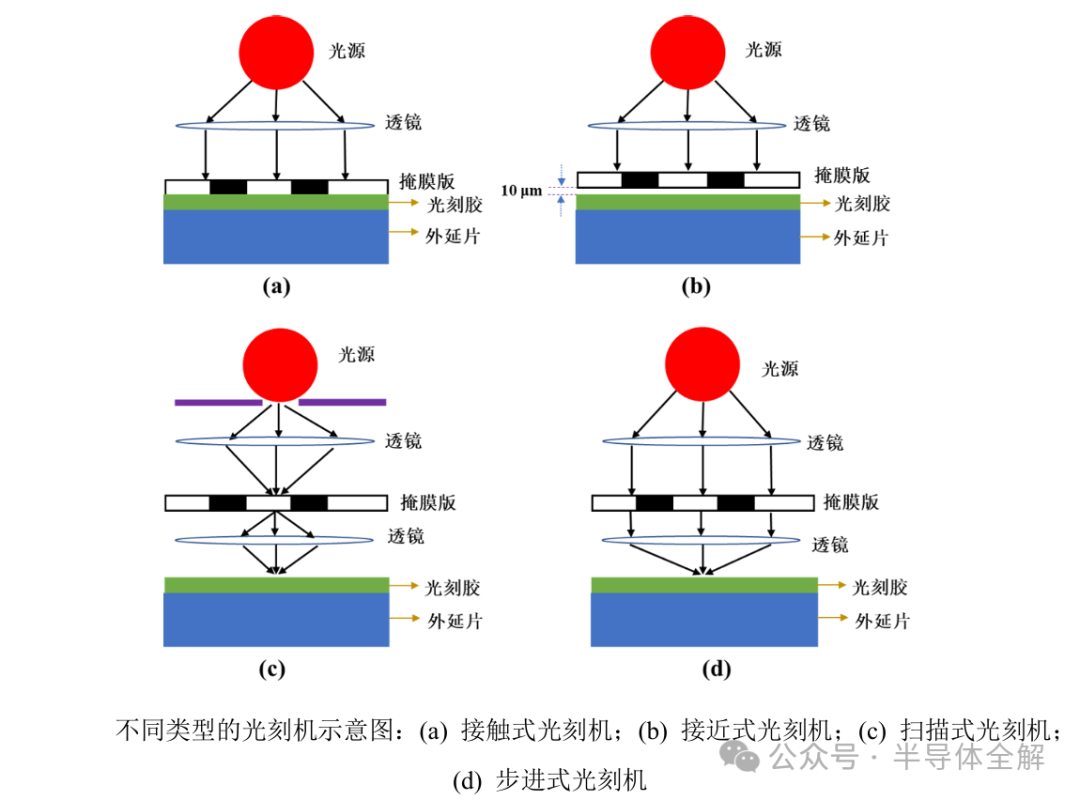

接触式光刻机 20 世纪 60-70 年代集成电路制造中的主要设备。在曝光过程中,掩模版与涂覆有光刻胶的硅片直接接触。如下图所示:

接触式光刻机的缩放比为 1:1,即全晶圆曝光,分辨率可达到 4~5 微米。由于掩模和光刻胶膜层反复接触和分离,随着曝光次数的增加,会引起掩模版和光刻胶膜层损坏、芯片良率下降等不良后果。一般掩模版在完成 15~25 次曝光后就需要进行清洁或更换,掩模版的制造和维护费用增加了光刻成本和芯片制造成本。

(2) 接近式光刻机

接近式光刻机在曝光过程中掩模版和光刻胶膜层之间存在 10~25mm 的间隔,有效减少了掩模版和光刻胶膜层损伤。

相比于接触式光刻机而言,接近式光刻机延长了掩模版的使用寿命,降低了芯片制造成本。接近式光刻机的缩放比近似为 1:1,分辨率可达到 2-4 mm,是 20 世纪 70 年代芯片制造的主要设备。

然而,掩模版和光刻胶膜层之间的微小间距会导致掩模曝光时产生菲涅耳衍射效应,这是制约接近式光刻机分辨率提高的主要因素。

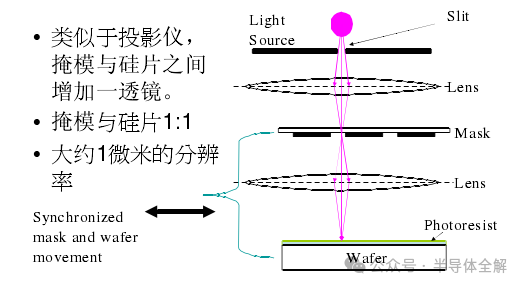

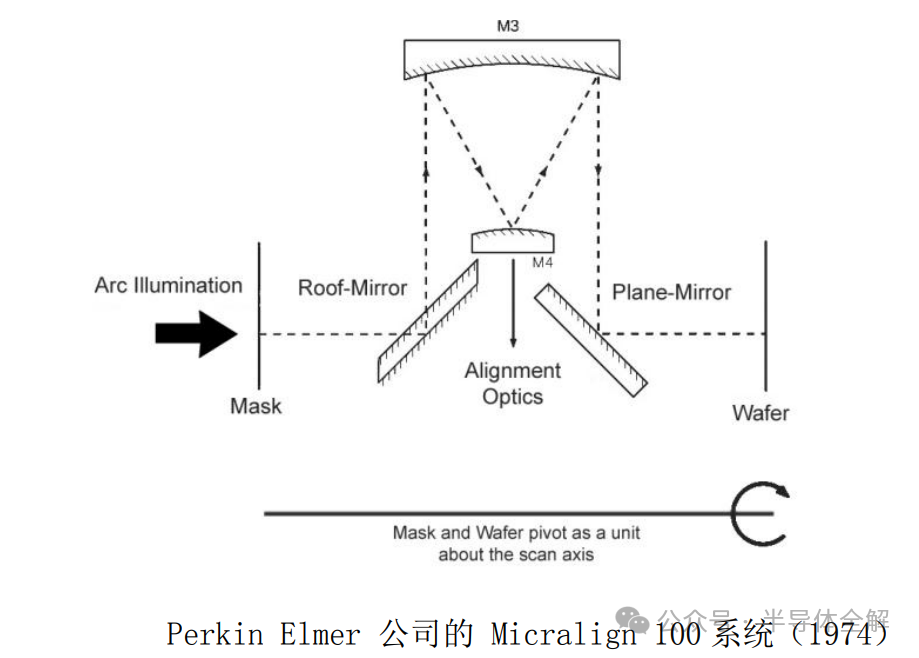

(3) 扫描式投影光刻机

随着对于更大晶圆,更高分辨率和更高产率需要的进一步增加,设备生产商又设计出了扫描(scan)光刻系统。

1973 年美国珀金埃尔默(Perkin Elmer)公司研制出扫描式投影光刻机,型号为 PE 100,PE100 光刻机采用共心全反射式投影系统,缩放比为 1:1,数值孔径达到 0.167。曝光过程中,以 1 mm 宽的弧形狭缝对掩模图形进行全视场扫描曝光。采用深紫外照明光源,并结合折反式投影物镜系统,扫描式投影光刻机可实现 1mm 的光刻分辨率。

投影物镜采用 Offner 结构,为全反射系统,如图所示。

它的有效视场是一个狭窄的环形,长 150mm,宽度只有 1mm。优点是成像质量高,匹兹万场区为零,并且物方和像方都是远心的。缺点是数值孔径最大只能到 0.16,整个系统装 调困难,并且需要高精度的工件台和掩模台扫描实现曝光。即使如此,随着成像要求的提高,Micralign 同样因为不能满足套刻精度的原因而不能满足曝光要求了。虽然光刻设备制造商也提出了一些改进的措施,但是随着对 CD 控制要求的进一步提高和掩模制造成本的增加,缩小倍率成像的步进(Step and repeat)光刻机获得了快速的发展。

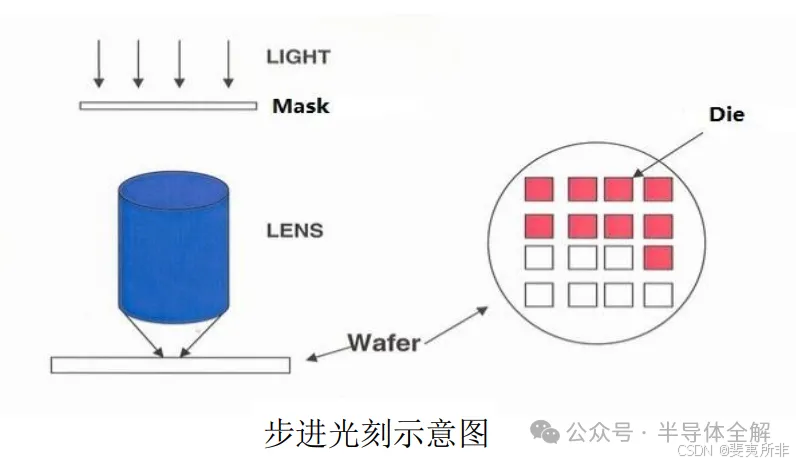

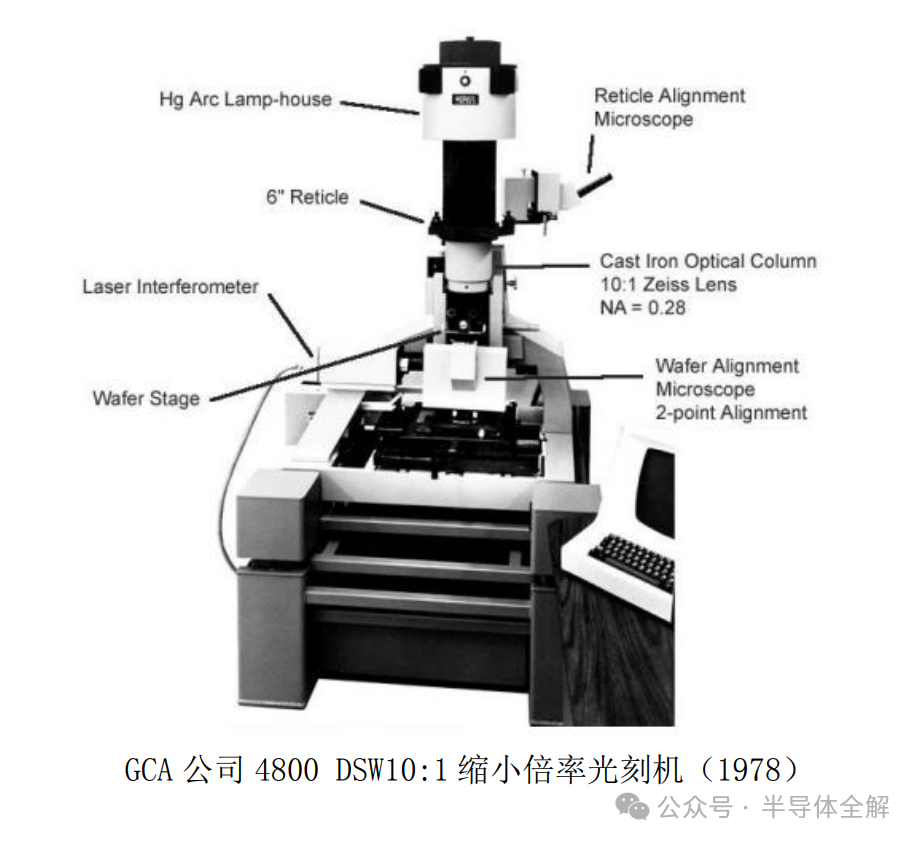

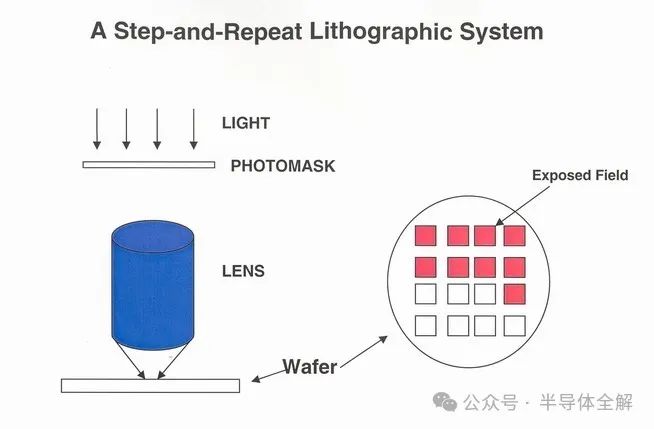

(4) 步进投影光刻机

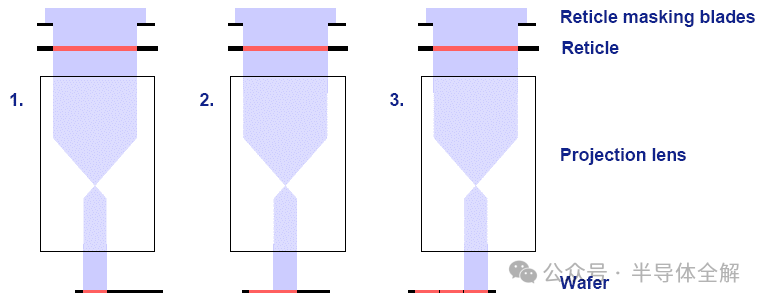

步进光刻机不再是全晶圆同时曝光,而是将晶圆分成了若干个区域(die),每个 die 就是前文所说的一块芯片。每次曝光完成一个 die 后再控制工件台的运动步进到下一个 die 再次曝光,如下图所示。

与全晶圆曝光不同的是,将掩模以缩小的倍率成像在硅片上需要额外增加掩模和硅片对准系统。

最早的步进光刻机是 GCA 公司的 4800 DSW 机型,诞生于 1978 年,数值孔径是 NA0.28,倍率是 10:1,视场是 10mm×10mm,如下图所示。

DSW4800 采用 g 线(436 nm)波长的汞灯光源,投影物镜的数值孔径达到 0.28,缩小比例为 10:1,可适用于特征尺寸为 1.25 mm 的集成电路制造。

分步式投影光刻机采用缩小倍率的投影物镜系统,例如 4:1、5:1 或 10:1,一次曝光将掩模图形转移到硅片的特定芯片区域,通过步进驱动完成全硅片的曝光。当选用波长为 248 nm 的 KrF 准分子激光器作为照明光源时,分步式投影光刻机可实现 180 nm 的光刻分辨率。

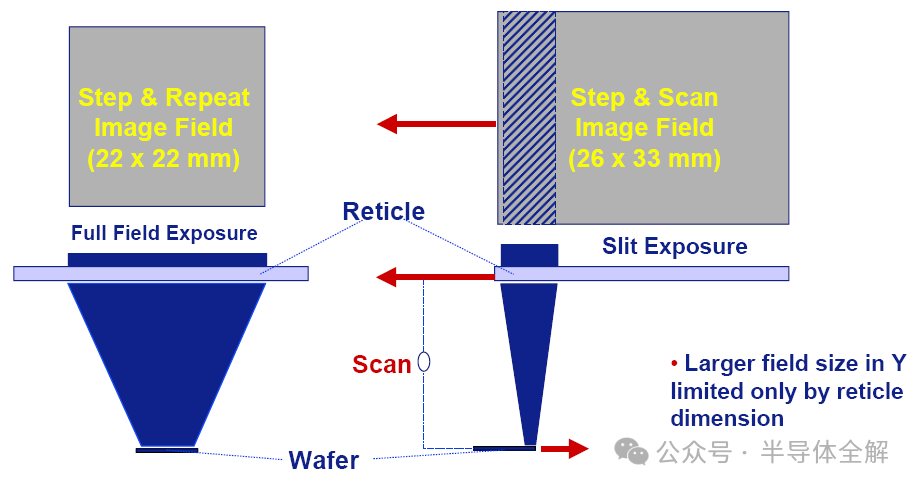

(5) 步进扫描投影光刻机

在摩尔定律的驱动下,对每个芯片的集成晶体管的数量要求越来越高,这在分辨率不断提高的同时,也要求芯片面积尽可能增加。这样对投影物镜的倍率要求又提高了,逐渐从 10:1 发展到 5:1 和 4:1,投影物镜视场也从 10mm×10mm 提高到 14mm×14mm 和 22mm×22mm。

这样虽然最早的步进光刻机对投影物镜的要求降低了,但是随着节点的缩小和芯片尺寸的进一步增加,投影物镜的难度是越来越大了。这最终促成了步进扫描(step and scan)光刻机的发明。

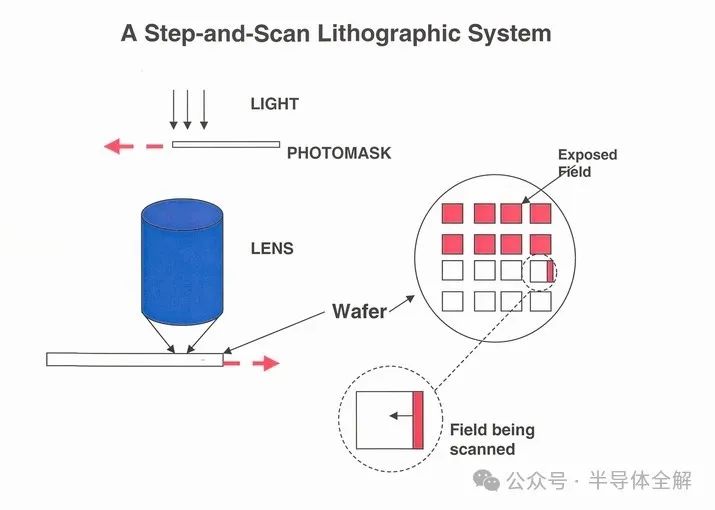

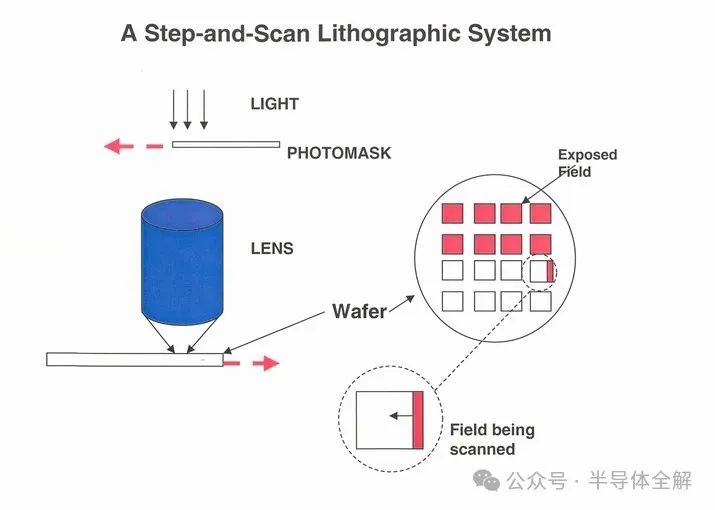

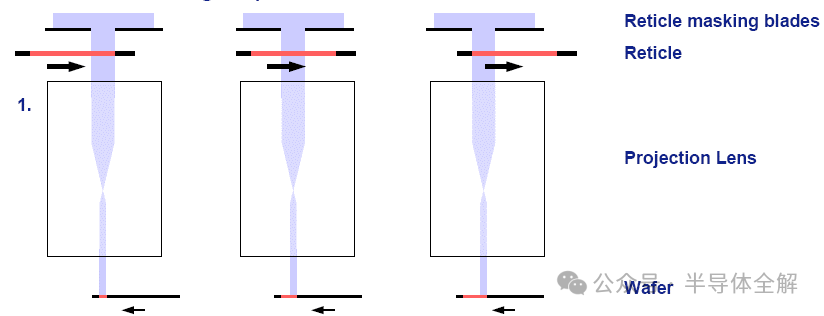

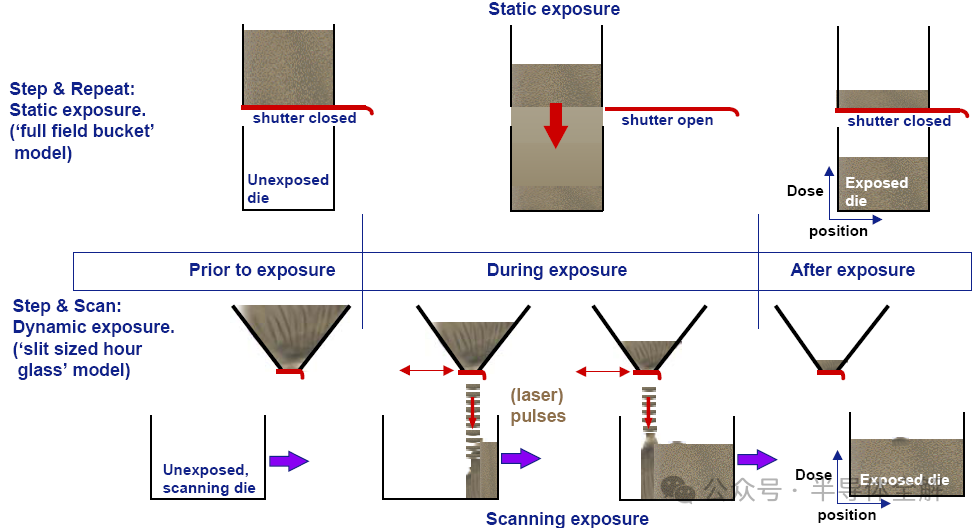

步进扫描光刻机与步进光刻机一个主要的区别是每个 die 不是同时曝光,而是通过掩模和晶圆的同步扫描运动来完成,如下图所示。

步进扫描投影光刻机的进行曝光时,工件台承载涂覆好光刻胶的硅片步进移动到曝光视场位置,然后在扫描狭缝开启的同时,掩模台和工件台开始进行同步运动。当完成曝光后,扫描狭缝关闭,这样便完成一次扫描曝光。之后,工件台步进驱动硅片将下一个待曝光单元移动到曝光视场位置。重复上述步进扫描曝光步骤,直至硅片上所有曝光单元全部完成曝光,再更换新的硅片。

这样在不增加投影物镜复杂度的情况下,可以获得更大的曝光视场,但代价是增加了工件台,掩模台和控制系统等的复杂度。

步进扫描光刻机可以说是为了平衡产率,工件台的复杂度和投影物镜的复杂度而在扫描光刻机和步进光刻机之间做的折中。

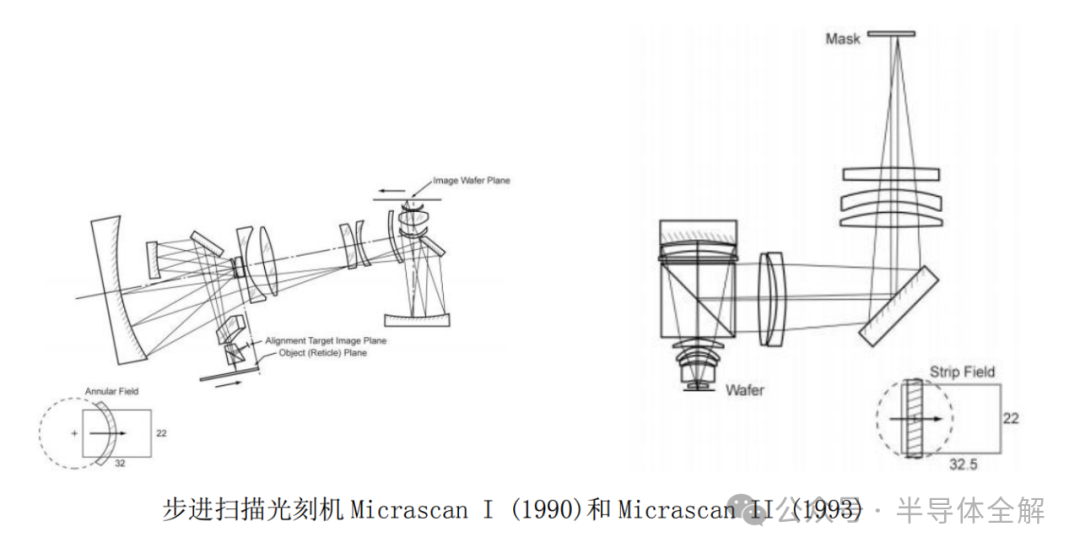

最早的步进扫描光刻机是 Perkin Elmer 公司于 1990 年推出的 Micrascan 系列,如图所示。该机型以 240~255 nm 波长的汞灯为曝光光源,投影物镜系统的数值孔径达到 0.35,光刻分辨率为 0.5 mm。

Micrascan I 是利用环形视场实现 22mm×32mm 的扫描视场,但是因为采用了很多折叠反射镜,装调困难,并且环形视场扫描存在过扫描影响产率,很快就被采用矩形视场扫描 Micrascan II 替代。Micrascan 型号后续系列的扫描视场达到了 22mm×50mm。

目前除了 EVU(extremely ultra violet, 13.5nm) 光刻机外,DUV(deep ultra violet,本文指 248nm 和 193nm)光刻机都是利用投影物镜的矩形视场实现扫描曝光的,虽然不同机型投影物镜的静态视场各有不同,但标准扫描视场基本都是 26mm×33mm。

六、结论:

光刻机是大规模集成电路制造产业的核心装备,而投影光刻物镜又是光刻机的核心部件,其发展水平很大程度上代表了光刻机的发展水平。

为了跟随摩尔定律的要求,投影光刻物镜在不断挑战技术极限,对设计、制造集成和像质补偿的要求在不断的提高。希望国内研发光刻机的科研工作者进一步努力,提升我国集成电路制造业水平!

参考文献:

(1) 尚红波 浸没光刻投影物镜光学设计与像差补偿研究 [D].

(2) 刘志帆 深紫外光刻机照明系统关键检测技术研究 [D].

(3) 李雪平 面向光刻机浸没系统设计的介观尺度流场扰动解析与抑制方法研究 [D].

(4) 彭茂荣 2024 年半导体产业发展议题 [C].

解读光刻工艺及设备原理

原创 圆圆 De 圆 半导体全解

一、光刻工艺简介

光刻工艺在半导体制作工艺过程中占有及其重要的地位,光刻质量的好坏直接影响器件的性能,了解光刻工艺首先要初步了解光刻机。

下图是 ASML 光刻机的主要结构和分布,主要有:光源、照明系统、掩模台、掩模传输系统,投影光刻物镜、工件台、硅片传输系统,对准系统,调平调焦系统,环境控制系统,整机框架和减振系统,整机控制系统和整机软件等,如下图所示:

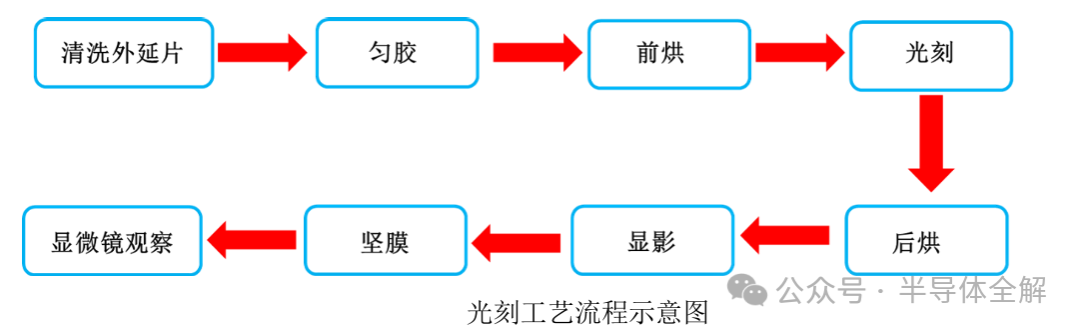

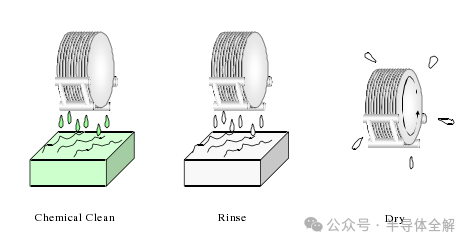

如下图所示,光刻工艺主要步骤包括:清洗外延片、匀胶、前烘、光刻、后烘、显影和坚膜。

在外延片运输过程中,可能会被环境污染,导致外延片表面有污染物。因此在匀胶前要对外延片进行冲洗,去除外延片表面的污染物,以免在制作过程中引入杂质,进而影响器件的性能。清洗后的外延片用氮气枪吹干或者放到热板上烘干,然后将外延片放置在匀胶机内进行匀胶。

为了增加光刻胶和外延片之间的粘性,使光刻胶更好地附着在外延片上,一般在匀涂光刻胶前,在外延片上匀涂一层增粘剂。匀胶机通过真空将外延片吸附,然后进行高速旋转,使光刻胶均匀地附着在外延片上。通过调整旋转转速和匀胶时间,改变光刻胶的厚度。

前烘是将匀胶后外延片放到热板上进行烘烤,将光刻胶内的多余的溶剂挥发,使其固化,使光刻胶更好的粘附在外延片上。

光刻是将前烘后的外延片放到光刻机中,采用曝光的方式,将掩膜版上的图形转移到外延片表面的光刻胶上,实现图形的转移。

为了获得较好的光刻效果,需要摸索不同图形对应的曝光的剂量(曝光时间)和曝光焦点(focus)。

一般在光刻后,需要根据实验条件来确定是否要对曝光后的外延片进行后烘,如果光刻胶为厚胶,后烘会让光刻胶上产生气泡,最终导致光刻失败。

后烘使光刻胶内的活性物质扩散,消除光刻过程中干涉引入的驻波效应,改善的光刻效果。

显影是将显影液和光刻胶进行化学反应,将曝光的部分溶解。一般曝光和未曝光的部分均会和显影液发生反应,因此需要对显影的时间进行摸索。在显影完成后,需要立刻将外延片放到水槽中,用流动的去离子水进行冲洗,去除残留在光刻胶上的显影液。

坚膜是烘烤显影后的外延片,使光刻胶内的溶剂挥发,增加光刻胶和外延片的粘附性。完成坚膜后,使用显微镜对光刻后的图形进行目检,判断光刻效果,判断进行刻蚀还是去胶后重新光刻。

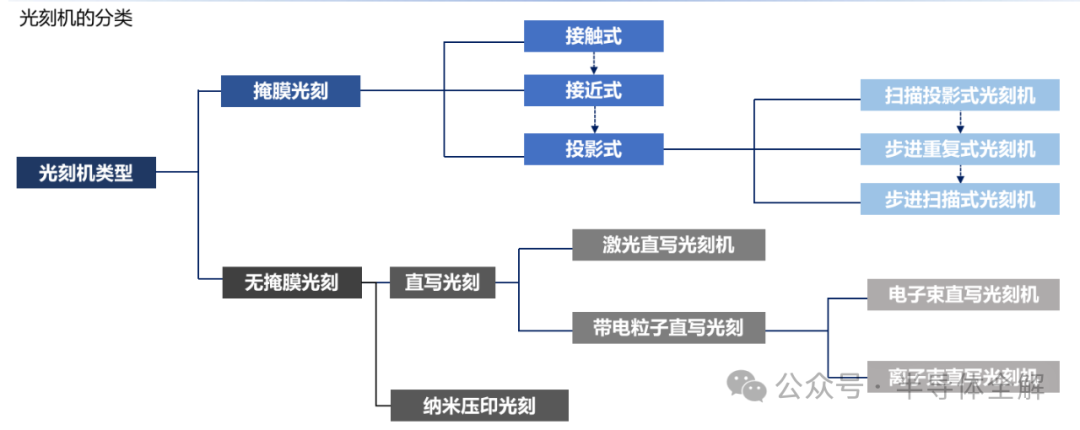

二、光刻机工作方式

根据光刻机的曝光方式的不同,将光刻机分为接触式光刻机、接近式光刻机、投影式光刻机和步进式光刻机,下面将分别介绍不同类型光刻的原理。

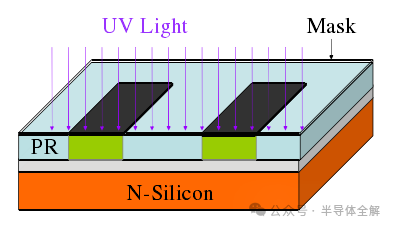

如上图 (a) 所示,接触式光刻机通过掩膜版和光刻胶直接接触进行曝光,结构较为简单,光源位于透镜的焦点处,发出的光经过透镜后变为平行光将整个掩膜版上图形全部转移到光刻胶上。这种光刻机分辨率为微米级,但是由于掩膜版直接和光刻胶接触,大大缩短了掩膜版的寿命。

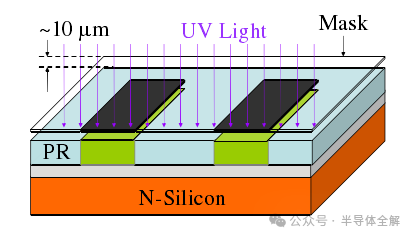

上图 (b) 是接近式光刻机,接近式光刻机和接触式光刻机不同的是,掩膜版和光刻胶并不 是直接接触,掩膜版位于距离光刻胶 10 μm 处,但是光刻胶挥发的溶剂会附着在掩膜版上,进而影响掩膜版的使用寿命。除此之外,接近式光刻机的分辨率低于接触式光刻机,曝光分辨率一般大于 3 μm。

按照光刻机工作台的运动方式,投影式光刻机分为步进投影式和步进扫描式两种。

如图 © 所示,投影式光刻机的掩膜版和待曝光的外延片之间增加了一个透镜,因此掩膜版避免了被光刻胶污染,光刻重复性较好。

步进投影式光刻机曝光的图形的大小和掩膜版上的相同,比例为 1:1,曝光的分辨率约 1 μm。

步进投影式光刻机工作原理见下图:

步进投影光刻机的工作方式见下图:

步进扫描投影光刻机和步进投影式光刻机不同点为:掩膜版上的图形和曝光在外延片上的图形大小之比为 5:1 或者 10:1,即将图形的长宽均按照 5:1 或者 10:1 的比例来进行缩小,其中采用 10:1 的比例来进行曝光具有更高的分辨率,但是曝光时间是 5:1 比例的 4 倍,因此大多采用折中的 5:1 的比例来进行曝光。这种方案的光刻机具有分辨率高的优势,分辨率一般低于 0.25 μm,为目前采用最多的光刻机。

下图是步进扫描式光刻机工作方式:

相比与步进投影光刻机,扫描光刻机运动方式更加复杂,在工作台运动的同时,光刻版也同步反方向运动。

这种运动方式可以增大光刻面积。

如何进一步了解步进投影和步进扫描运动方式的差异呢?

下图是两者工作方式和扫描面积的差异,步进扫描运动方式工作区更大,局部更精密。

如果将两种工作方式以沙漏来举例,步进投影更像是一个矩形漏斗,在光刻时,矩形漏斗里的光同时喷出,一口气完成光刻工作。

步进扫描式光刻机像一个锥形漏斗,在光刻工作时,光一边往下填充,工作台一边运动。对工作台的光照更加均匀细腻。

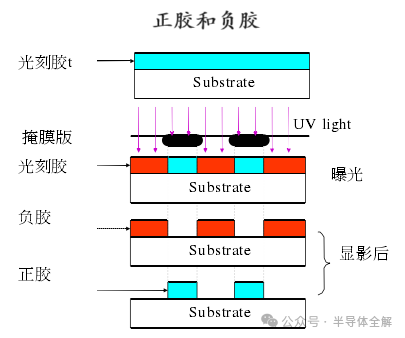

三、光刻胶的正胶与负胶

光刻技术主要是通过光刻机曝光和将曝光后的外延片显影,将掩膜版上的图形转移到光刻胶上。

光刻胶的主要成分有树脂、光引发剂和溶剂等。被曝光后,光刻胶成分中的光引发剂的化学性质发生改变,在显影后完成图形的转移。光刻胶根据曝光显影后的性质分为正光刻胶和负光刻胶。

如下图 (a) 所示,正光刻胶即显影后曝光区域的光刻胶被去除,常用的正光刻胶有杜邦公司生产的 SPR200 等;

与正光刻胶相反,如图 (b) 所示,负光刻胶是显影后曝光区域的光刻胶被保留,常用的负光刻胶有 N244 等。

关于光刻工艺就介绍到这儿,对半导体工艺感兴趣的同学,可以阅读公众号其它文章!

参考文献:

(1) 张功 大功率分布式布拉格反射激光器及其在调频连续波激光雷达中的应用 [D].

(2) 蔡一鸣 高平均功率脉冲光纤激光放大系统研究 [D].

(3) 赵蓉 基于飞秒激光直写光波导的光纤传感技术研究 [D].

(4) 丛阳滋 联合多源点云的激光雷达三维建图与更新 [D].

详解半导体工艺及光刻机技术

原创 圆圆 De 圆 半导体全解

一、集成电路的诞生

1946 年 2 月,世界上第一台电子计算机 ENIAC(Electronic Numerical Integrator And Computer)在美国诞生,它是一个重达 30 吨的庞然大物,使用了 17468 只电子管、7000 只电阻、10000 只电容,耗电量 150 千瓦。

1947 年 12 月 23 日,美国贝尔实验室制造出来了第一个晶体管。晶体管具有电子管的主要功能,并且克服了电子管体积大、耗电量大、结构脆弱的缺点。

1956 年的诺贝尔物理奖授予了晶体管的三位发明者:John Bardeen、William Shockley 和 Walter Brattain。在晶体管发明后,很快就出现了基于半导体的集成电路的构想。

1952 年,英国雷达研究所的科学家 Geoffrey Dummer 在一次会议上提出:如果把电子线路中的分立元器件集成在一块半导体晶片上,则电子线路的体积将大幅缩小,可靠性也会提高。这就是初期集成电路的构想,晶体管的发明使这种想法成为了可能。

下图就是发明晶体管的三剑客和全球首发的晶体管雏形。

在 1958~1959 期间,德州仪器公司的 Jack Kilby 与仙童公司的 Robert Noyce 间隔数月分别发明了锗集成电路和硅集成电路,开创了世界微电子学的历史。

Jack Kilby 获得了 2000 年的诺贝尔物理学奖(Robert Noyce 已于 1990 年去世)。

集成电路是现代信息社会的基石,已经在各行各业中发挥着非常重要的作用,如电视机、计算机、通讯、人工智能、虚拟现实设备等。

二、摩尔定律

1965 年 4 月 19 日,英特尔(Intel)创始人之一、时任仙童半导体公司研究开发实验室主任的 Gordon Moore 应邀为《Electronics Magazine》杂志 35 周年专刊写了一篇观察评论报告,题目是:“Cramming More Components Onto Integrated Circuits” (把更多的元件填进集成电路)。文中预言半导体芯片上集成的晶体管数量将每年增加一倍,这就是著名的摩尔定律。1975 年,摩尔在 IEEE 国际电子组件大会上,根据当时的实际情况对摩尔定律进行了修正,把 “每年增加一倍” 改为 “每两年增加一倍”。后来,时任 Intel 执行主席 David House 综合考虑晶体管数量和增长速度等因素,将该周期更新为 18 个月。摩尔定律更为准确的表述是:当价格不变时,集成电路上可容纳的元器件数目,每隔 18 至 24 个月增加一倍,性能也将提升一倍。在 40 多年内,微处理器上集成的晶体管数目与摩尔定律的预测值相符合。集成电路制造技术是人类科技史上发展最为迅速的一项技术,其性价比在过去的 40 年内提高了 6 个数量级。

在半导体工业中,摩尔定律已被用于指导制定长期的科研与发展计划。微处理器的价格、存储器容量、传感器以及数码相机的像素尺寸等的进步,都与摩尔定律有紧密联系。

通常有三种方法提高集成电路的性能:缩小单个晶体管的特征尺寸、增大芯片的尺寸和优化电路结构。

考虑到电子设备小型化的发展趋势,缩小单个晶体管的特征尺寸是集成电路发展的最主要方法。晶体管尺寸的减小可以降低功耗,提高集成电路的响应速度,增大芯片上单位面积内的晶体管数量。最小特征尺寸(smallest feature size)也称关键线条(critical dimention,CD),还可叫作节点 (node)。

当前,半导体制造行业依然孜孜不倦地挑战摩尔定律极限。芯片龙头制造商以台积电、因特尔、三星为代表,尤以台积电走在最前沿。台积电占据了全球晶圆代工一半以上的市场份额,稳居第一。其 3nm 制程已实现量产,2nm 制程处于研发阶段,而 1nm 制程的研发也已提上了日程。反观老牌龙头因特尔,迟迟无法实现制程的突破,甚至谋求台积电代工,以分得些许高端芯片的全球市场份额。

摩尔定律是一种基于数据统计的推测,而非物理或自然的规律。为了维持摩尔定律,每年需要投入的研发资本将呈指数形式增长,此被称为摩尔第二定律。另外,由于特征尺寸快要达到物理极限,技术节点将难以按照摩尔定律所预测的速率推进下去。业界提出 More Moore 和 More than Moore 两条路径,通过采用新架构或新材料来维持半导体行业的发展。一是遵循摩尔定律,致力于晶体管的不断缩放以提高性能,从而进一步提升性能和降低功耗,即 More Moore。二是拓展摩尔定律,通过电路设计、系统算法优化或封装技术来提高芯片的性能,即 More Than Moore。

三、半导体芯片制造技术

集成电路的制造包括近 800 道物理、化学工序,主要有 5 个制造阶段:晶圆(Wafer)的制备、芯片制造、芯片检测、芯片封装和验收测试。

其中半导体芯片生产主要涉及 IC 设计、IC 制造、IC 封测三大环节。

核心 IC 制造环节是将芯片电路图从掩膜转移至硅片上,并实现对应功能的过程,包括光刻、刻蚀、离子注入、薄膜沉积、化学机械研磨等步骤。

芯片的制造需利用光刻(Lithography)技术。光刻是以一种光敏感聚合物(光刻胶)为主要材料的照相制版技术,目的是将整套集成电路图案刻蚀在晶圆上。

单词 “Lithography” 来源于希腊词语 “lithos” 和 “graphia”,前者意为 “石头”,后者意为 “写”。所以,“光刻” 的字面意思是 “在石头上书写”。在芯片制造过程中,集成电路的信息被写进了光刻胶。

光刻的成本约占整个芯片制造成本的 1/3,耗费时间约占整个芯片工艺的 40-60%,是大规模集成电路制造过程中最复杂、昂贵和关键的工艺。

一般的光刻工艺要经历八道工序:气相成底膜、旋转涂胶、软烘、对准曝光、后烘 、显影、坚膜烘焙和检测。

光刻工序的主要步骤如下:

前处理: 对晶圆衬底的清洗通常用丙酮 (Acetone) 清除污迹,再用酒精处理掉丙酮,最后用去离子水 (DI water) 清洗干净,用氮气吹干样品。

涂胶: 将光刻胶均匀涂抹在晶圆表面。

前烘: 烘干光刻胶,去除其中的溶剂,使之成型。

对准曝光: 将掩膜的图案投影到光刻胶上。有时需要对同一基底进行多次曝光,这要求每次对准的位置十分精准,才能使得多次光刻不会互相影响。

后烘: 目的是减少驻波效应,并使光刻胶的曝光部分易于溶解于显影液(正光刻胶)。

显影: 显影是为了去除掉变性的光刻胶,以形成同掩膜板一样的样品表面。

硬烘(Hard Baking):有四个目的,其一是完全蒸发掉光刻胶里面的溶剂,以免污染后续的离子注入环境;其二是坚膜,以提高光刻胶在离子注入或刻蚀中保护其下晶圆片的能力;其三是进一步增强光刻胶与硅片表面之间的黏附性;其四是进一步减少驻波效应。

刻蚀掺杂: 利用曝光后的样品模式,刻蚀后可形成需要的样品,该过程也称为图形转移(Pattern transfer)。

去胶: 将残余光刻胶清洗干净,之后同样需要烘烤,以形成坚固的成品。

通常,要经过 25 至 40 次的反复曝光和刻蚀,才能将一个包含数百万个晶体管及相应导线的集成电路图案复制到晶圆上。

集成电路发展至今,电路集成度提高了 6 个数量级,主要归功于光刻技术的进步。随着器件和电路特征尺寸的不断缩小,光刻工艺已成为微电子技术进一步发展的主要瓶颈。

四、芯片性能的发展

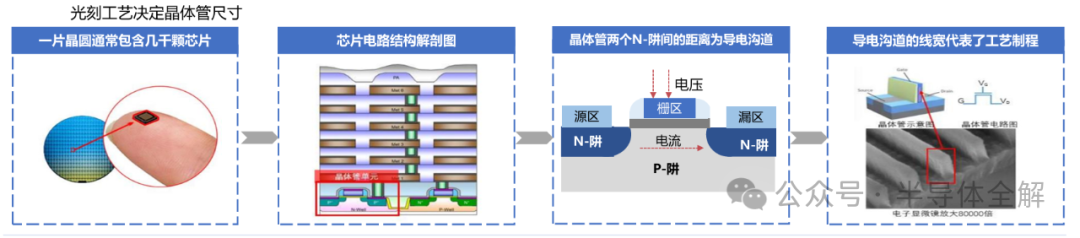

光刻技术之所以重要,因为光刻工艺决定了晶体管尺寸的大小!

晶体管是芯片的基本单元,一片硅片由数千、数万或数亿的晶体管组成。

如上图,在晶体管的栅区和衬底间加上电压后,电流可以从源区传递到漏区,形成电信号,而源区和漏区对应的两个 N— 阱间的距离即为导电沟道的长度,该长度即晶体管的尺寸,即线宽,也就是我们常说的芯片制程。

由于晶体管中的电子一般以饱和速度运行,因此信息传递速度由导电沟道长度决定。晶体管导电沟道越短,则信号传递速度越快,单位时间内芯片处理的信息越多;同时,单位面积芯片的晶体管也更多,成本相应降低。

因此,晶体管线宽指标越小代表了芯片性能越好,即芯片制程有逐步减小的技术需求,而光刻工艺决定了晶体管尺寸的大小及制程技术节点的推进。

下图是晶体管结构及线宽发展路线图:

五、光刻机设备结构

光刻技术实质上是 IC 芯片制造的图形转移技术,该图像转移的过程包括把设计图纸上的图形转移到掩膜基板上,再把掩膜版上的图形转移到晶圆表面光刻胶上,最后再把晶圆表面光刻胶图形转移到晶片上,整个图形转移过程涉及到的光刻机类别众多。

根据工作原理进行分类,按照光刻时是否使用掩膜,将光刻机分为掩膜光刻以及无掩膜光刻。其中,掩膜光刻包含接触式光刻机、接近式 光刻机和投影式光刻机;无掩膜光刻包含激光直写光刻机、纳米压印光刻机等,具体分类如下图所示。

根据曝光时掩膜版与衬底间的位置关系,掩膜光刻可分为接触式、接近式和投影式光刻。其中,在投影式光刻中,根据曝光过程中掩膜和晶圆的移动方式,可进一步细分为扫描投影光刻机、步进重复光刻机和步进扫描式光刻机。

当前中高端光刻机市场,仍然以阿斯麦(ASML)为行业龙头,其市占率高达七成以上。与之相比,尼康虽然在同级别产品中具有很大的价格优势,但业内口碑一般,其全球市场份额也仅为一成,捉襟见肘。

近年来,阿斯麦与其三大股东 —— 英特尔、三星、台积电结成利益共同体,致力于不断挑战并实现摩尔定律。

值得注意的是,阿斯麦非常注重对研发的投入,即使在亏损时期也没有降低研发成本,因此从根本上保证了其前瞻性和延续性。

投影光刻机主要由光源、照明系统、掩膜台、投影光刻物镜和晶圆控制系统组成,如图所示。

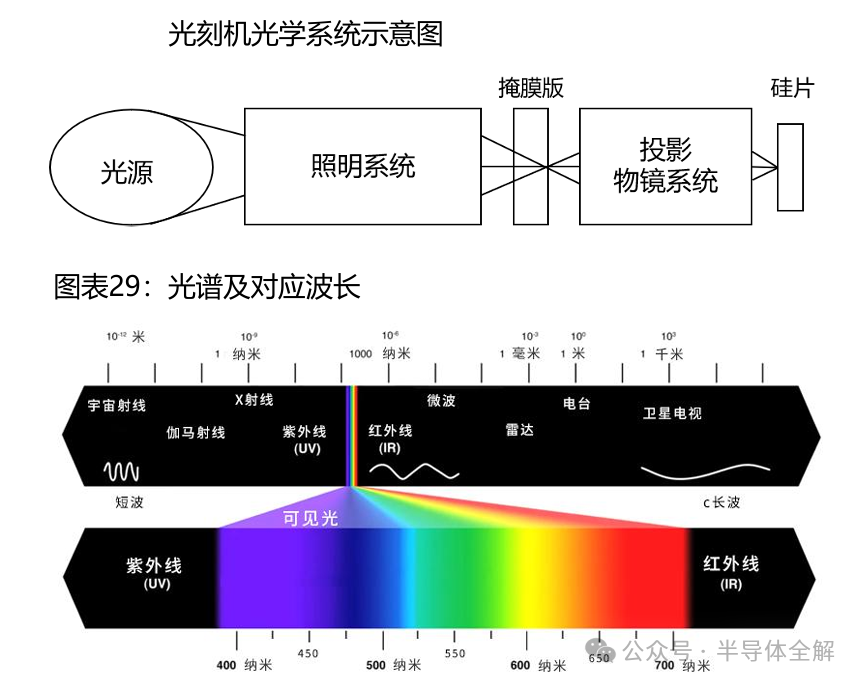

(1) 光源: 光源系统是光刻设备的核心,光源波长决定工艺能力 ,光刻机的技术进步也是波长不断缩短的过程。

光源为光刻机提供稳定频率、能量的光能,光源功率的大小决定了光刻机的产能。Cymer 是光刻机光源的重要供应商之一,已推出一系列产品,包括氟化氪(Krypton Fluoride,KrF)光源、氟化氩(Argon Fluoride,ArF)光源和极紫外光源。

光源波长越短,则晶体管线宽越小,芯片性能越强。光源发出的光束经照明系统后穿过掩膜版,再由投影物镜系统将掩膜版上的电路图形复制到硅片表面。

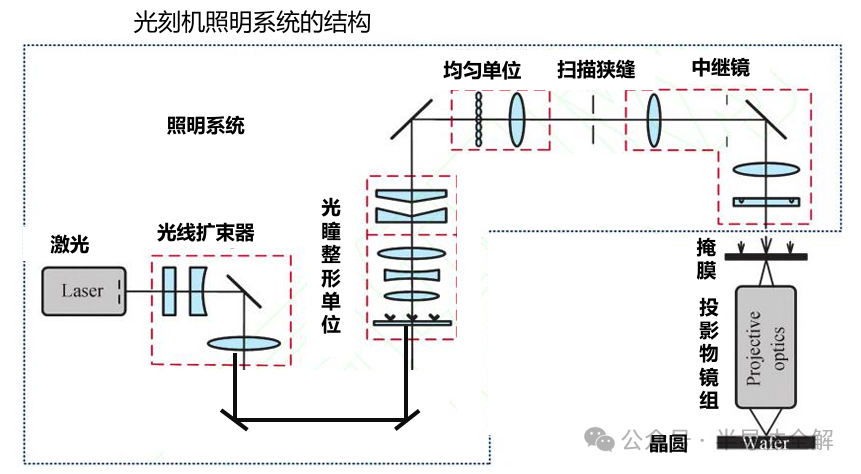

(2) 照明系统: 照明系统作为光刻机的核心部件之一,其作用是将光源发出的光束进行整形匀化后照明掩膜面,再由投影物镜系统将掩膜面上的图形复制到硅片表面。

照明系统光路:光源经过扩束准直与传输后进入光瞳整形单元,然后再经过照明匀化单元来实现特定分布的照明光场。扫描狭缝用来确定曝光视场尺寸和中心位置,控制曝光剂量,并与掩膜台和硅片台完成同步扫描曝光。

中继镜组位于扫描狭缝与掩膜版之间,负责将扫描狭缝上的照明光场中继成像到掩膜面上。

(3) 掩膜台: 即光刻物镜的物面,是放置掩膜板的地方,其能进行多自由度调整,并且在步进 - 扫描(Step and Scan)曝光模式中,与晶圆台配合实现掩模板与晶圆的极高精度的同步步进和扫描。

(4) 投影光刻物镜: 是光刻机的核心部件,将掩膜图案无失真地投影在晶圆上,其成像质量的指标极其苛刻,通常要求波像差与畸变都要在 1nm 左右。

光刻机的分辨率 R 与光源波长 λ 和 NA 的关系可表示为公式。

式中, k1 是工艺因子。随着集成电路特征尺寸的不断缩小,光刻机的分辨率不断提高,投影光刻物镜也向着大 NA、短波长的方向发展。

顺便提一下,越高端的光刻机,遇到的光学问题越复杂,只有对光学研究越深入,才能将设备整体性能提升。

光线是一种电磁波,所以具有波粒二象性。

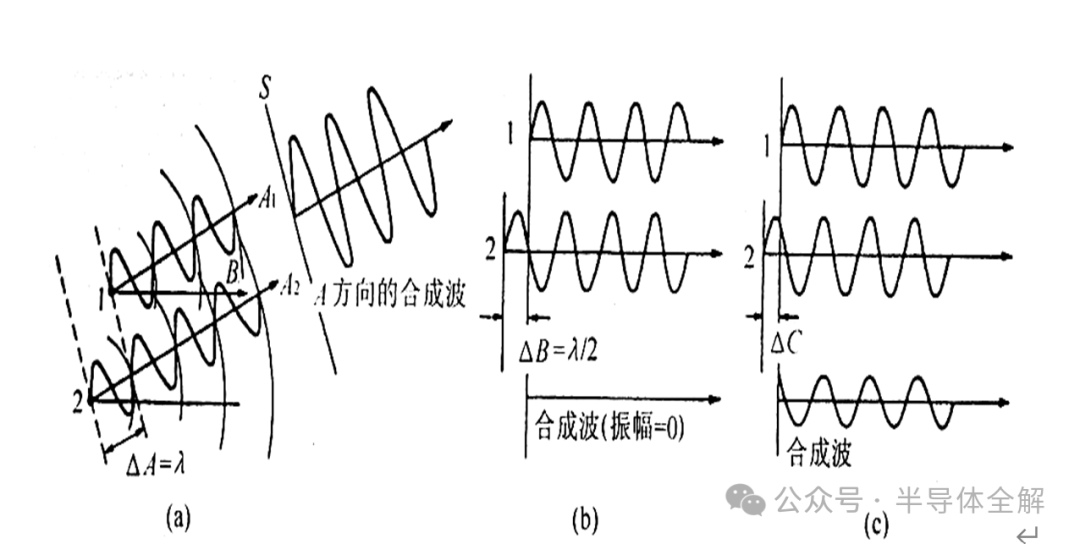

光线在传播过程中有相互影响,可能相互加强,也可能相互减弱:

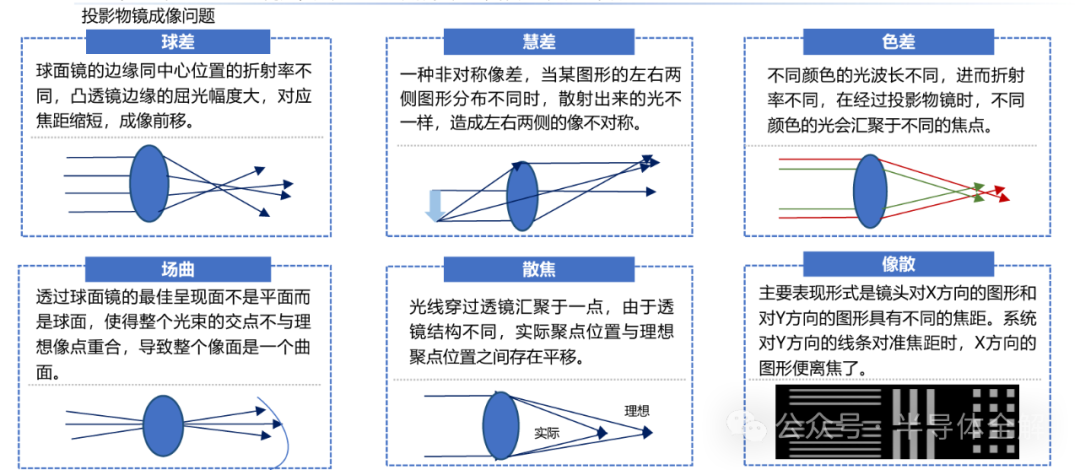

光学镜片投影过程中存在因透镜结构、光线波长等因素造成的球差、彗差、散焦、场曲、色差等问题。随着光刻机的数值孔径增大,分辨率下降,为了能刻蚀尽可能精细的线条,在物镜实际工作过程中,全视场的波前像差均方根至少要小于 0.07λ,像面弯曲要求小于几十纳米,畸变也不能超过几纳米。基于不同的像差、色差等问题,光刻工艺对投影物镜的制作提出更高的要求。

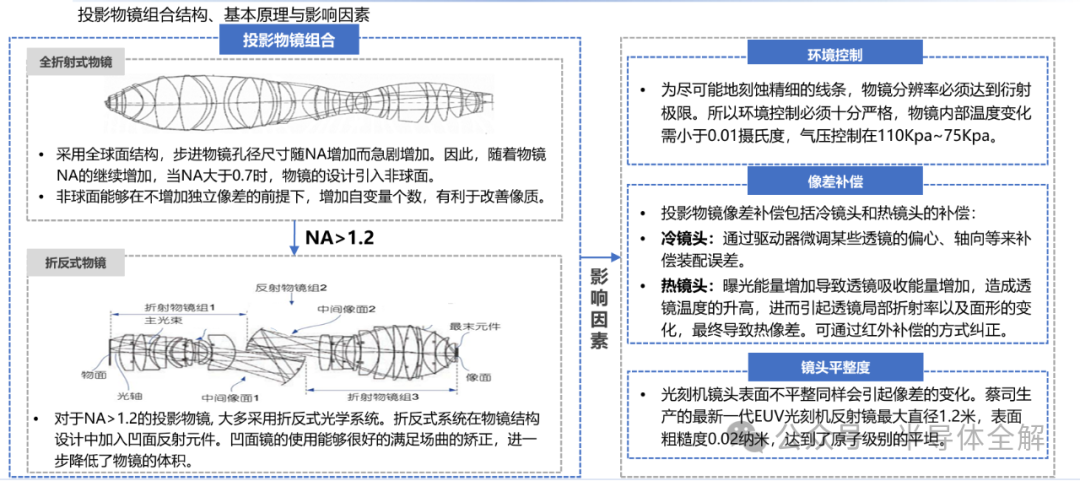

由于单片投影物镜存在球差、色差等问题,因此在实际应用中,需要通过组合投影物镜进行纠正。随着数值孔径的增加,分辨率达到衍射极限,所以对于像差的精准度也相应提高,包括了对环境控制、冷镜头 / 热镜头的像差补偿、镜头表面平整度等的极致要求。

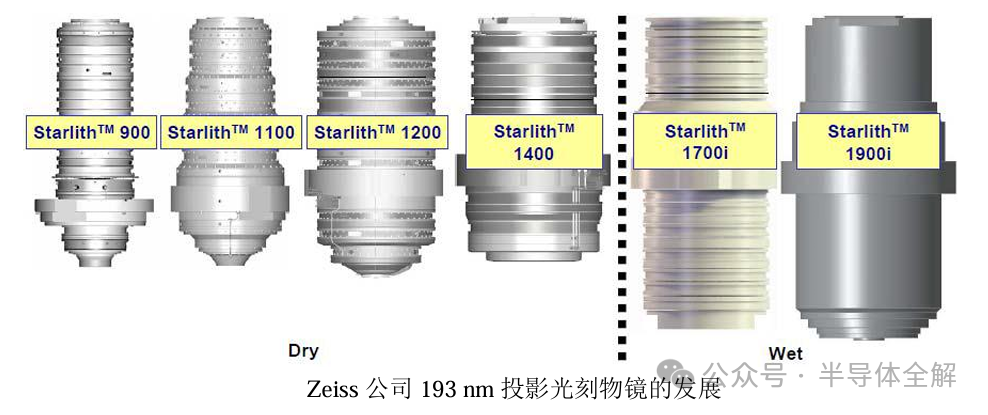

下图展示了 Zeiss 公司的 193nm 光刻物镜的发展,NA 从早期的 StarlithTM900 型号的 0.63 提高至 StarlithTM1900i 型号的 1.35,分辨率从 130 nm 提高至 45nm。

为了实现高 NA,从 StarlithTM 1100 型号起,Zeiss 的光刻物镜开始采用非球面透镜,从 StarlithTM 1700i 型号起,开始采用像方浸液式和折反射式结构。

Nikon 和 Zeiss 两家公司的投影光刻物镜的发展历程,物镜的结构主要经历了以下几种形式:折射式、折射式 + 非球面元件、折射式 + 非球面元件 + 像方浸液、折反式 + 非球面元件 + 像方浸液。

折射式全球面结构形式的 NA 的极限为 0.75 左右,加入非球面可提高到 0.9 左右。如果要在 193nm 波段进一步提高 NA,则需采用浸没式的结构形式,即把像面浸入去离子水中。

浸没折射式能达到 NA1.0 以上,浸没折反射式能到到 NA 1.35。

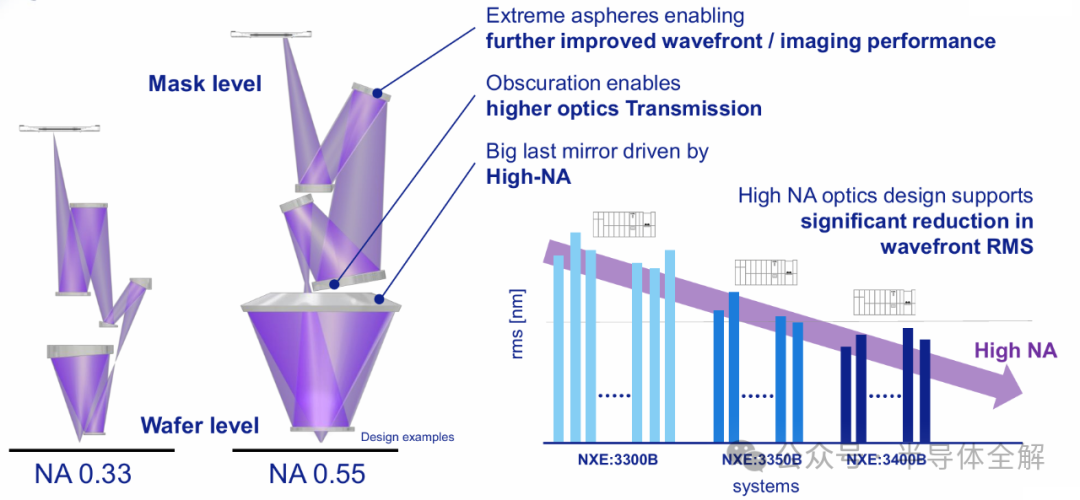

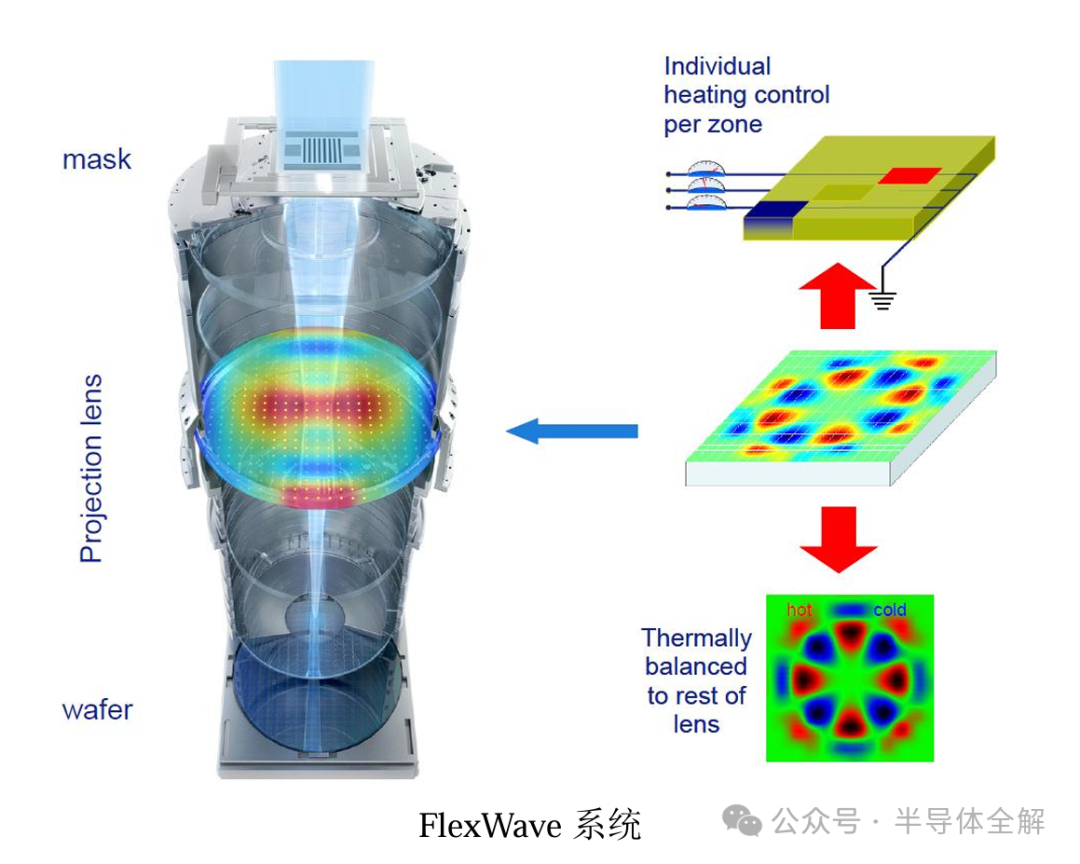

为了更精细地控制光刻物镜的波前,ASML 公司提出了 FlexWave 系统,如图所示。FlexWave 系统包含一个位于光瞳面的光学元件,元件上布置了一系列相互独立的传导和电阻结构,这些结构很微小,不会对光束产生遮挡和散射而影响物镜的成像。通过控制这些传导和电阻结构的电流,可对光学元件的特定区域进行加热,可以使元件上产生可控的温度分布,从而达到补偿像差的目的。

当 FlexWave 工作时,需要对元件进行并行地降温,这是为了使 FlexWave 光学元件上的温度分布平稳恒定,同时保证其热量不会对周围的光学元件造成干扰。

(5) 晶圆控制系统: 晶圆控制系统在光刻机曝光过程中对晶圆进行装载、对准、 步进、扫描、和卸载,是极其精密的机械系统。

六、结论:

光刻机之复杂程度堪称人类科技之巅。一方面,光刻机制造是多学科交织的极其复杂的工程,其研发集成了精密光学、精密运动学、高精度微环境控制、算法、微电子、高精度测控等多学科全球最顶尖工程师和科学家的智慧。

另一方面,光刻机是一整套完整的纳米工业体系,要产出纳米级精度的芯片,需要其背后的光源系统、光学镜头系统、精密运动和环境控制系统、测量系统、聚焦系统、对准系统等模块全部达到纳米级精度,并且高度集成和协同,每一个子系统的技术迭代成果均蕴含了该领域最前沿的高精尖技术。

毫不夸张地说,光刻机是人类工业文明的巅峰之作,是现代工业体系皇冠上的明珠。

参考文献:

(1) 徐象如 高数值孔径投影光刻物镜像质补偿策略与偏振像差研究 [D].

(2) 李晶 高 NA 投影光刻物镜波像差检测技术研究 [D].

(3) 华福证券 光刻机行业深度报告:博采众星之光,点亮皇冠明珠 [C].

(4) 民生证券 掩膜版行业深度报告:光刻蓝本亟待突破,国产替代大有可为 [C].

(5) 尚红波 浸没光刻投影物镜光学设计与像差补偿研究 [D].

(6) 芮大为 光刻照明系统光学设计与补偿策略研究 [D].

(7) 许伟才 投影光刻物镜的光学设计与像质补偿 [D].

(8) 周泽龙 投影光刻物镜偏振像差研究 [D].

(9) 赵磊 投影光刻物镜像质补偿策略与补偿技术研究 [D].

via:

-

一文了解集成电路及光刻技术发展历程 原创 圆圆 De 圆 半导体全解 2024 年 06 月 08 日 18:41 湖北

-

一文详解光刻机进化史 原创 圆圆 De 圆 半导体全解 2024 年 06 月 16 日 09:00 湖北

-

解读光刻工艺及设备原理!原创 圆圆 De 圆 半导体全解 2024 年 07 月 20 日 08:57 湖北

-

一文详解半导体工艺及光刻机技术 原创 圆圆 De 圆 半导体全解 2024 年 10 月 03 日 11:02 湖北

2809

2809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?