下图是某款Sunxi平台的时钟树分布图,输入是24MHZ的晶震源,输出则是很多个不同的频点。

一般来讲,输出频率和输入频率满足如下的关系:

这篇文章讨论这个公式的原理和来历。

下图所示的是PLL的基本结构,这是一个负反馈电路,生成时钟信号的核心部分是压控振荡器(Voltage-Controlled Oscillator, VCO),VCO能够根据所加的电压调整频率的振荡器,从图中可以看到,兼相器可以比较外部输入的基准时钟和VCO自身输入的时钟间的相位差,如果两个时钟一致则维持VCO电压,如果不一致就需要通过控制电路对VCO电压进行调整,VCO主频过高则降低电压,反之则提升电压。

使用按上述过程得到的电压值直接控制VCO, 可以让输出时钟和基准时钟达成一致,但是这样得到的时钟不稳定,因此反馈时钟信号还要用一个低通滤波器去掉高频成分在输入VCO,这样就可以稳定地生成和外部输入时钟相同的频率,相同相位的时钟信号。这就是PLL的工作原理。

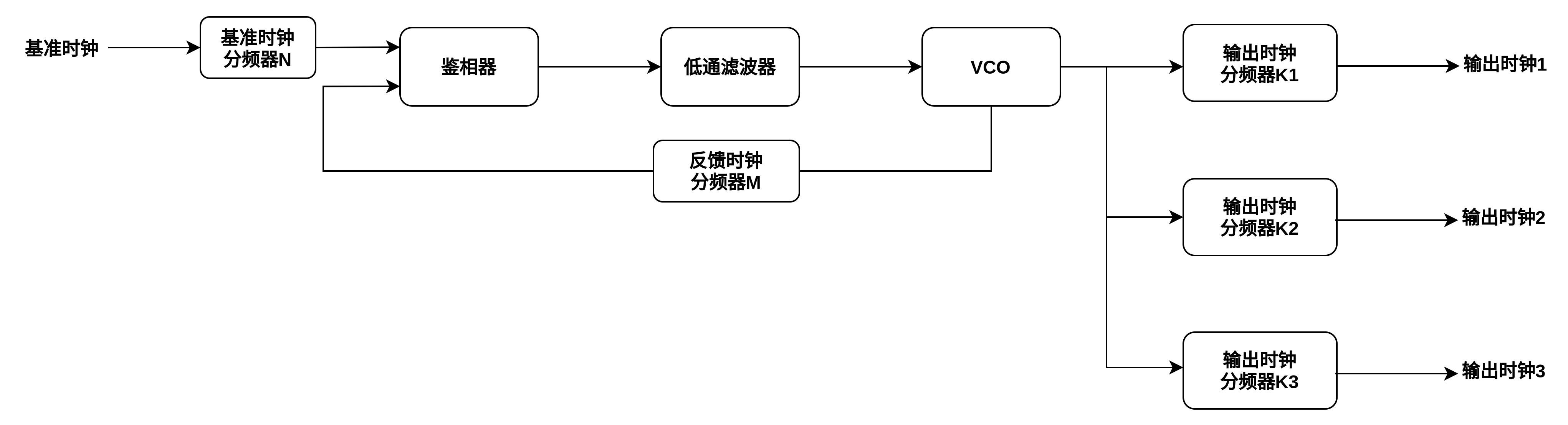

实际的ASIC中实现的电路有很多,工作时钟频率也不尽相同, 需要能够产生各种各样频率的时钟信号,因此基于上图的基本结构,再添加几个可以编程的分频器的PLL块情况更为常见,典型的结构它如下图所示:

基准时钟在输入鉴相器之前要通过分频器,如果分频比为N,VCO的目标频率就为基准频率的1/N,另外反馈VCO的输出时钟到鉴相器的路径也追加了分频器,当这里的分频比为M时,反馈控制的目标就是让VCO振荡频率的1/M和目标频率一致,因此,基准时钟的频率和VCO的震荡频率的关系可以表示为:

ASIC的PLL使用的是可编程的分频器,可以自由设定M和N的值,通过设置反馈时钟的分频比,还能使VCO以高于基准频率的频率震荡。

从图中可以看出,典型的PLL块中VCO后端也有分频器,可以将VCO震荡生成的时钟信号再次分频,并且VCO后接的多个独立输出都有分频器,这样从一个VCO时钟可以生成多个不同频率的时钟。它们的关系是:

依据这个公式设置适当的M,N,和K值,就可以根据从外部输入的基准时钟信号生成各种频率的时钟信号。

PLL是一个以外部输入的基准信号为目标,因VCO振荡频率为控制对象的负反馈控制系统,当然,在启动,复位或者基准时钟大幅变动时,反馈系统需要一定的时间才能让VCO的震荡稳定下来,因此在PLL的输出时钟稳定之前,由该时钟同步的用户电路可能会发生无法与预测的动作。

为了防止这种情况的发生,PLL块中还有对基准信号和反馈信号进行监测的机制,当VCO输出稳定并和基准时钟吻合时,我们称PLL为锁定状态,外部电路利用锁定输出来判断此时的时候是否可以信赖,例如,在PLL锁定之前让用户电路保持复位,就可以规避不稳定时钟引起的无法预测的动作。

拓展:

数字电路中,在每个时钟脉冲之后,CPU内部的信号线需要一些时间才能稳定到新状态。也就是说,每条信号线必须完成从0到1或从1到0的转换。如果在此之前的下一个时钟脉冲到来,则结果将不正确。在过渡过程中,一些能量被浪费为热量(大部分在驱动晶体管内部)。当执行引起许多转换的复杂指令时,时钟频率越高,产生的热量就越大。过热可能会损坏晶体管。

时钟和晶体管之间功耗的关系用下面公式描述:

微处理器内部的能耗和功率

对CMOS芯片,一次(0->1或1->0)的能耗:

动态能耗 = 1/2 * 容性负载 * 电压²

每个晶体管的功率:动态功率 = 1/2 * 容性负载 * 电压² * 开关频率

目前处理器已经达到了风冷散热极限。

对于时钟来说,以占空比为%50为例,时钟信号本身是50%占空比的周期方波型号,不管频率怎么变,从时域分析来看,其实能量都是一样的,平均电压是不变的,受影响的是受时钟信号控制的晶体管,它们的能量消耗受频率控制,晶体管按开关次数计算能量,而电阻按照电压持续时间计算能量,所以频率加快可以提高晶体管能耗,但是提高不了电阻的能耗,区分电阻模型和晶体管模型的区别。

PLL(锁相环)是一种负反馈电路,用于生成与外部输入基准时钟同步的时钟信号。通过M和N分频器,它可以产生不同频率的时钟。M值决定了VCO(压控振荡器)的反馈频率,N值确定了输出与基准频率的关系。通过适当设置M和N,可以根据基准时钟生成所需频率。在PLL锁定状态下,其输出时钟稳定,适合外部电路使用。

PLL(锁相环)是一种负反馈电路,用于生成与外部输入基准时钟同步的时钟信号。通过M和N分频器,它可以产生不同频率的时钟。M值决定了VCO(压控振荡器)的反馈频率,N值确定了输出与基准频率的关系。通过适当设置M和N,可以根据基准时钟生成所需频率。在PLL锁定状态下,其输出时钟稳定,适合外部电路使用。

1267

1267

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?