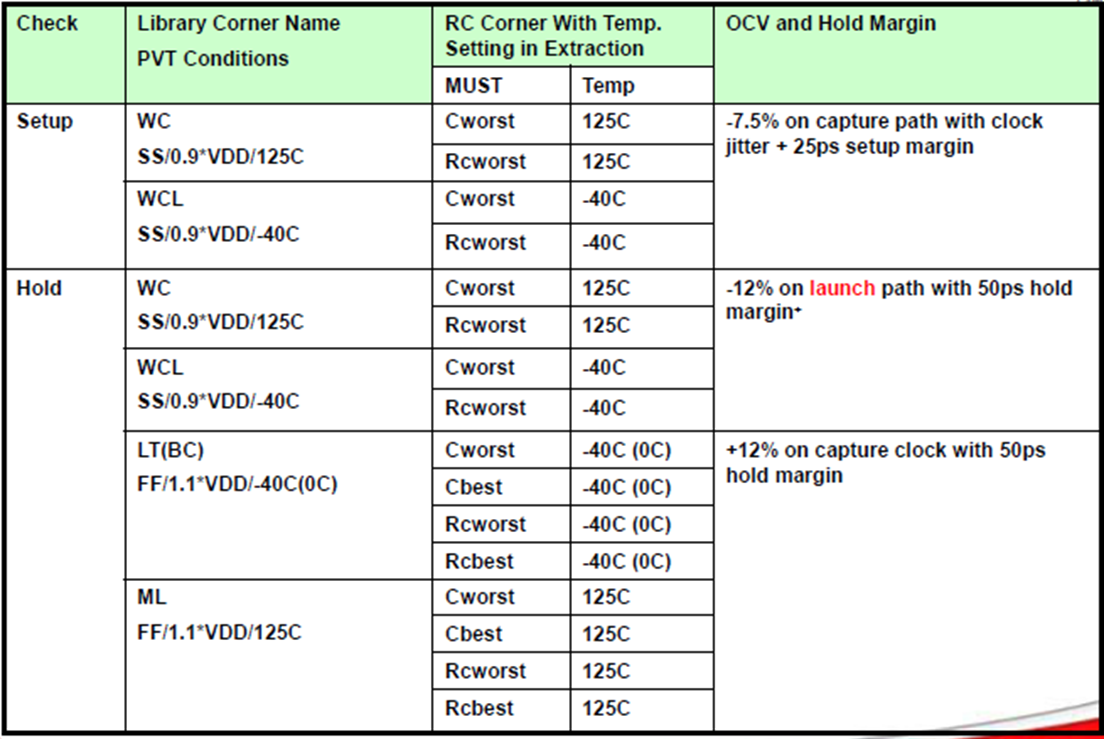

TSMC sign off guideline如下图所示:

可以看出来:signoff corner一共16个,setup有4个,都在慢速低压下;hold一共12个,在高速高压下8个,另外在慢速低压下也可能出现hold最差的情况,与setup一样还有4个。

setup uncertainty = clock jitter + margin

hold uncertainty = margin,且hold margin可以加在launch或capture path上。

T40项目中,timing signoff对setup加的uncertainty为100ps,对hold的uncertainty为50ps。

一般后仿用的WC(慢速低压高温)和LT(高速高压低温)。

那么问题来了

1、为什么hold check不需要考虑jitter呢?

2、为什么hold check需要考虑慢速低压的情况?

3、为什么在hold check,需要分别在launch和capture clock上加正负两种margin?

-

先看第一个问题

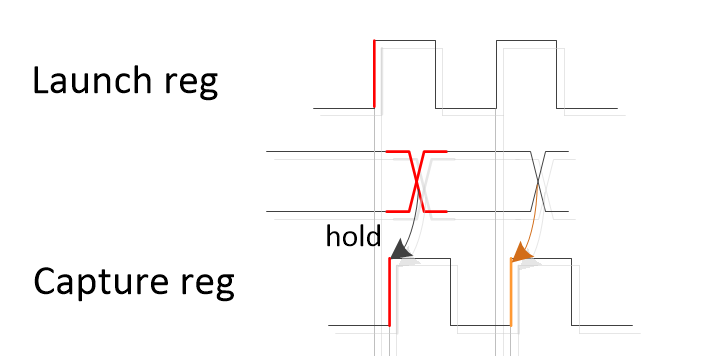

如果launch edge从红色沿发出,那么hold是看capture reg的红色沿还是黄色沿呢?

来看一条hold路径就知道了

很清楚了,hold capture edge也是同周期的红色沿。

jitter来自于时钟源的固有抖动,对作用于不用寄存器的同周期的沿,jitter施加的影响一致,所以对hold来说,jitter天然不存在,uncertainty中只需要加margin,不需要考虑jitter。

而对于setup check,capture edge(橘色)在launch reg发出后的下一周期 ,jitter会对两个沿施加不同影响,所以uncertainty中除了margin还需要考虑jitter。

-

再看第二个问题,从data path上看,一般ss下setup最差,ff下hold最差,那么什么情况下,ss会触发hold violation?

clock skew会导致capture clock比launch clock慢得多,那么hold slack就出现了最差情况。clock skew在ff下会更好,而在ss下会出现偏移。所以hold check增加ss corner是考虑了clock skew。

-

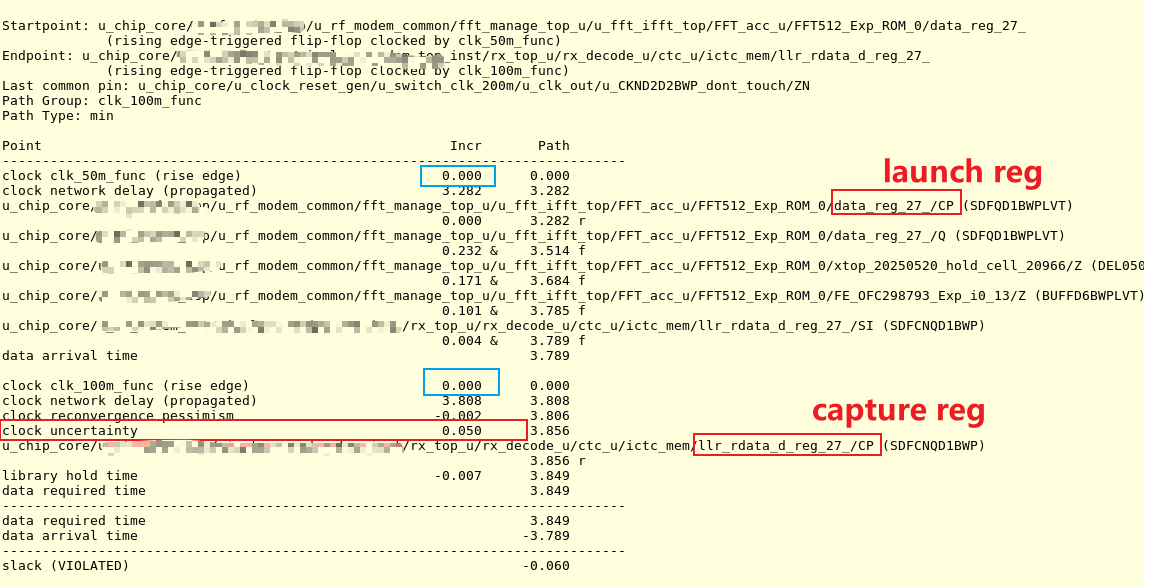

再看第三个问题,对launch/capture clock加margin为何区别对待?

首先,众所周知,launch data提前和capture clock延迟都是减少hold slack的行为。

在launch edge上加-12%的 hold margin,那么数据输出的沿(红色)也会相应提前,从而进一步减少hold slack。在capture edge上加12% hold margin,此为采样时钟延迟。

至于为什么分别加在ss和ff corner,可否交换,ss下+12% margin@capture clock,ff下-12% margin@launch clock?个人认为也是可以的,因为不管在哪个corner下,hold slack都是capture clock time - launch clock time - data delay

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?