1、多级存储概念

| 特性 | SRAM | DRAM | FLASH |

|---|---|---|---|

| 存储原理 | 触发器(6T/4T结构) | 电容(1T1C结构) | 浮栅晶体管(1T结构) |

| 易失性 | 易失,断电丢失 无需刷新 | 易失,断电丢失 需定期刷新(64ms) | 非易失,断电保留 无需刷新 |

| 读写速度 | 1-10ns | 10-100ns | 读快,写慢 NOR快,NAND慢 |

| 用途 | CPU cache(L1~3) | 主内存DDR | NAND:SSD、U盘 NOR:固件存储 |

2、 cache物理结构

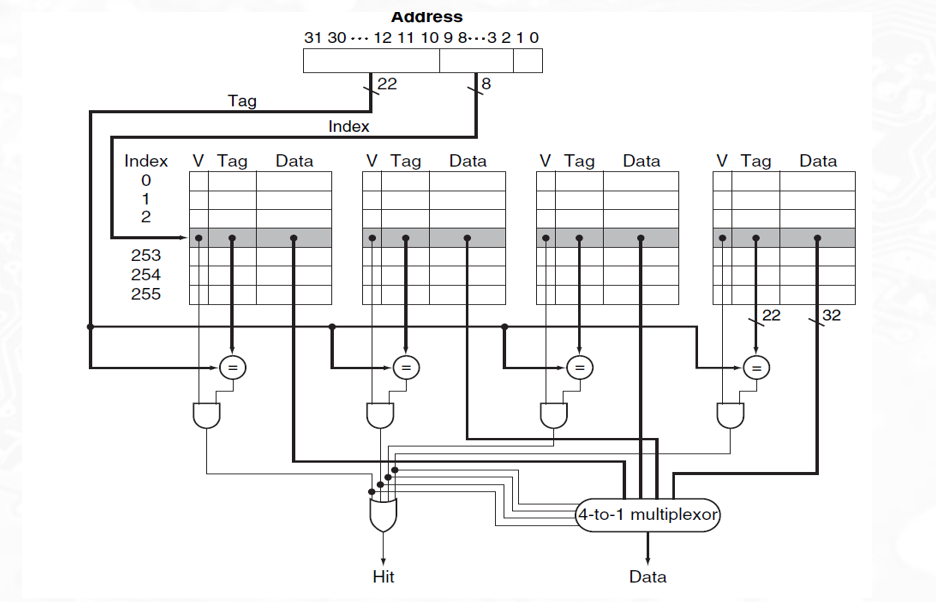

对于同一个index可以索引出4条cacheline。该4条cacheline不可能都要用,因此还需要地址中的高段tag位域和cache中存的tag做比较,如果两者都相等,并且当前cacheline的“valid”有效,则证明命中该cacheline。一个cacheline其实是存储了一段datablock(32B or 64B),具体要用该段data block中的哪块数据,还要根据地址中的低位“offset”进行选择。至于cache line是否有效,则由valid位来判断,如果该cache line不存在内存映射时,就是无效的。

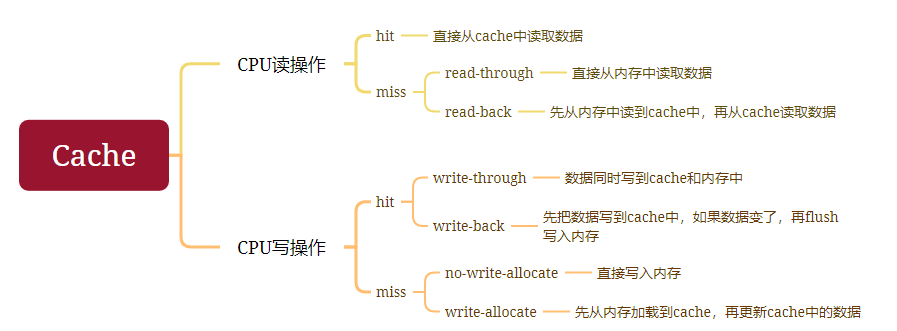

命中分写命中和读命中,命中只关心CPU的目标地址是否有效的存在于cache中,与数据是否保持一致性无关。

3、cache一致性

两种局部性

- 【write-back】数据写入cache时,不会同步写入下一级存储单元(可能L2,也可能直接就是内存),只有在cache中的数据需要被更新时,才会将(旧)数据写入下级存储。(先cache后mem,变了才写回mem)

- 【write-through】不管数据变不变,通通写入cache和mem。

- 若写miss,两种方式:

- 【no-write-allocate】直接写到内存。

- 【write-allocate】也称为写时取(fetch on write),即先从内存加载到cache,再按照指定的hit策略(write-back or write-through)继续更新cache中的数据。一般选择write-back,因为write-back+write-allocate的组合可以提升处理器性能,而write-through+write-allocate的组合对提升处理器性能没有帮助。

4、cache使用场景

-

对于单CPU,不操作外设,只对内存读写,可以放心的使用cache。对于其它情况,有两种办法:

1)手动更新cache,这需要对外设的机制较为了解,且要找到合适的时机刷新(将cache里的数据flush到内存里)或无效(Invalidate,将cache里的内容清掉,下次再读取的时候需要去内存里读最新的内容)

2)将内存设置为non-cacheable -

从应用角度看会cache更结合实际、更容易理解

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?