目录

前言

用FPGA实现SPI主机

一、SPI 特性

1.1同步

发送数据时钟+发送数据

1.2速率

I2C协议v2.1规定了100K,400K和3.4M三种速率(bps)。

具体到产品中SPI的速率为系统时钟频率的1/2。

1.3全双工

两根数据线

二、数据接口

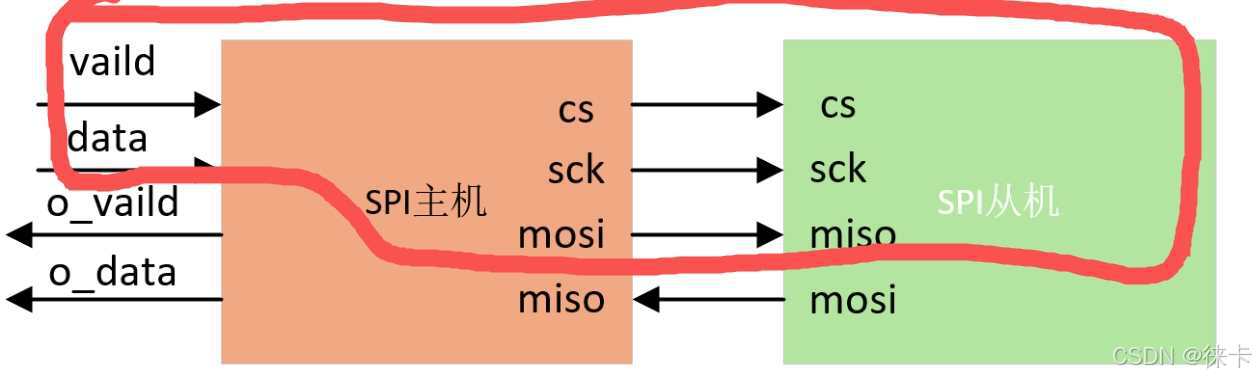

2.1主从机连接

2.2传输模式

| MODE | CPLO | CPHL |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

二、难点

2.1 难点1:SPI数据是在下降沿变化,上升沿保持

解决思路:对系统时钟产生二分频计数器,既可以指示spi_clk上升下降沿,又可以在spi_clk时钟下降沿改变数据,上升沿数据保持。

2.2 难点2:串并转换

思路:串转并移位寄存器往里填数,并转串移位移位寄存器往外溢数

always@(posedge i_clk)begin

if(i_rst)

ro_spi_mosi <= 'd0;

else if(w_user_active)

ro_spi_mosi <= i_user_data[cnt];//并转串

else

ro_spi_mosi <= ro_spi_mosi;

end

always@(posedge ro_spi_clk,posedge i_rst)begin

if(i_rst)

user_data <= 'd0;

else

user_data <= {user_read_data[6 : 0],i_spi_miso};//串转并

end

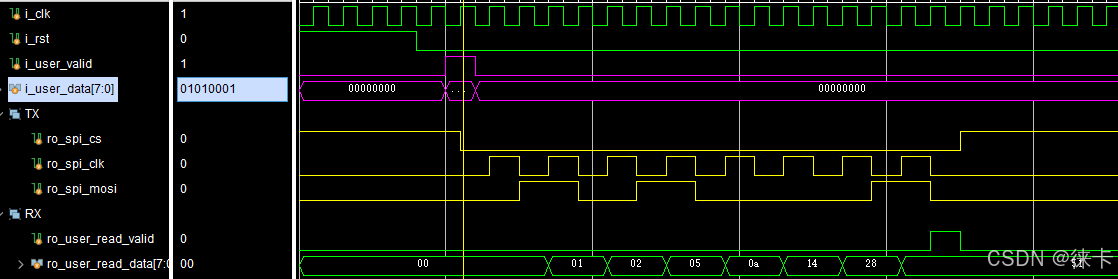

3 仿真

简单仿真验证一下逻辑,输出信号下降沿变化,对应从机就是上升沿读取数据,没啥问题,ok

备注

仅用于记录日常学习,侵权必究

2048

2048

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?