前言

7系列 Bank划分,参考链接https://www.bilibili.com/read/readlist/rl205277?spm_id_from=333.1369.opus.module_collection.click

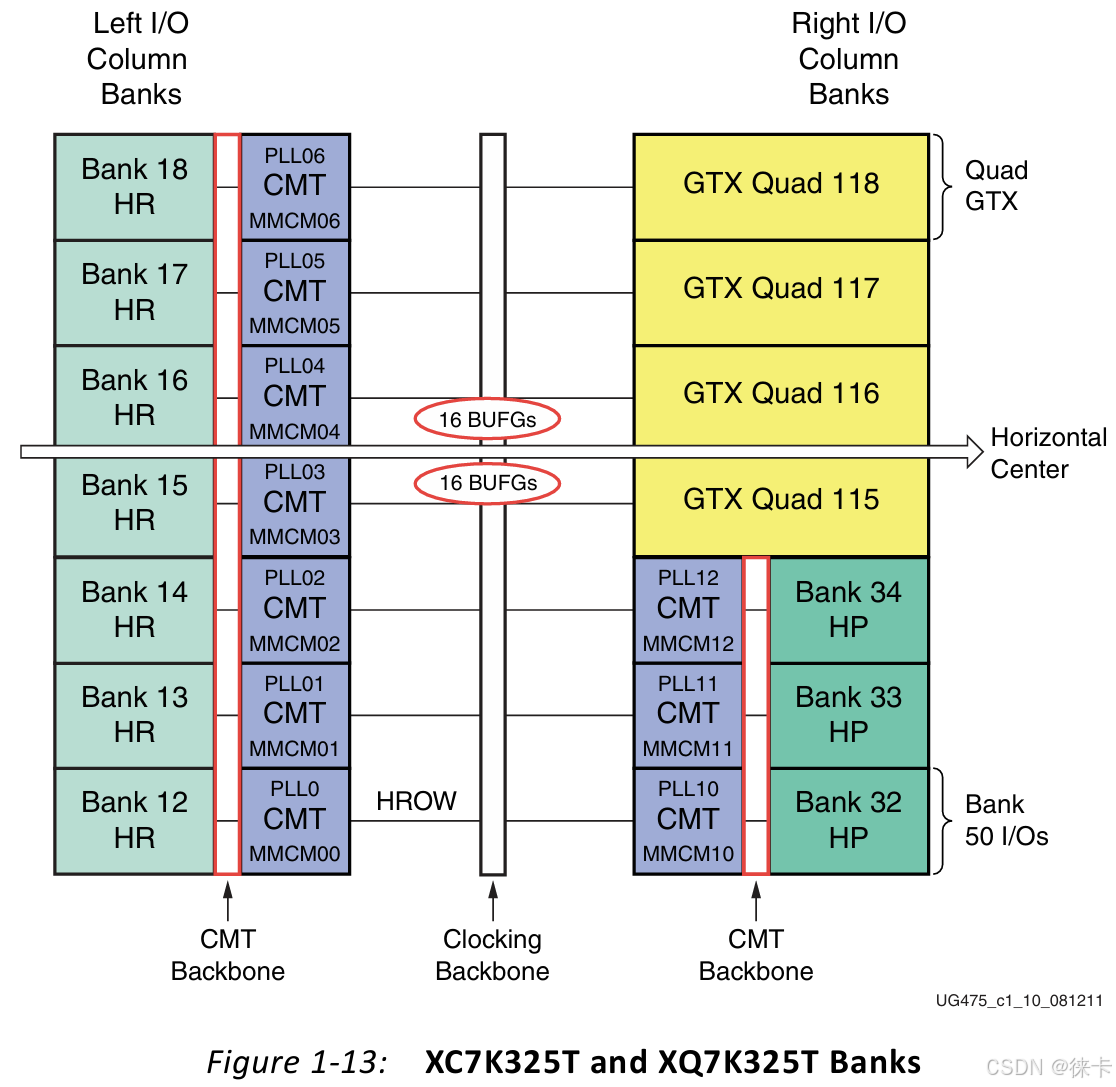

一、Xilinx 7系列 Bank划分

划分bank的原因:1、为了可以扩展多种IO口电平 2、IO口逻辑资源绑定

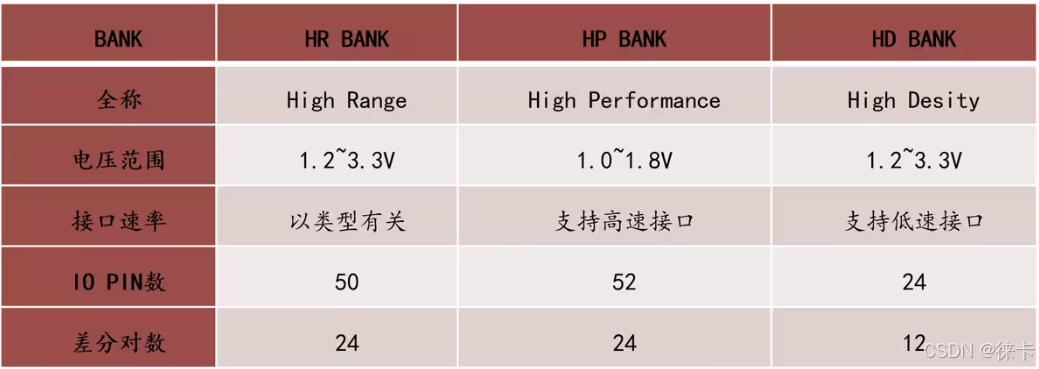

HP:High Performance,应用于高速场景,比如DDR或其他高速差分线

HR:High Range,应用于宽范围I/0,最高能够支持到3.3V的电压。

HD:High Density,应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V.

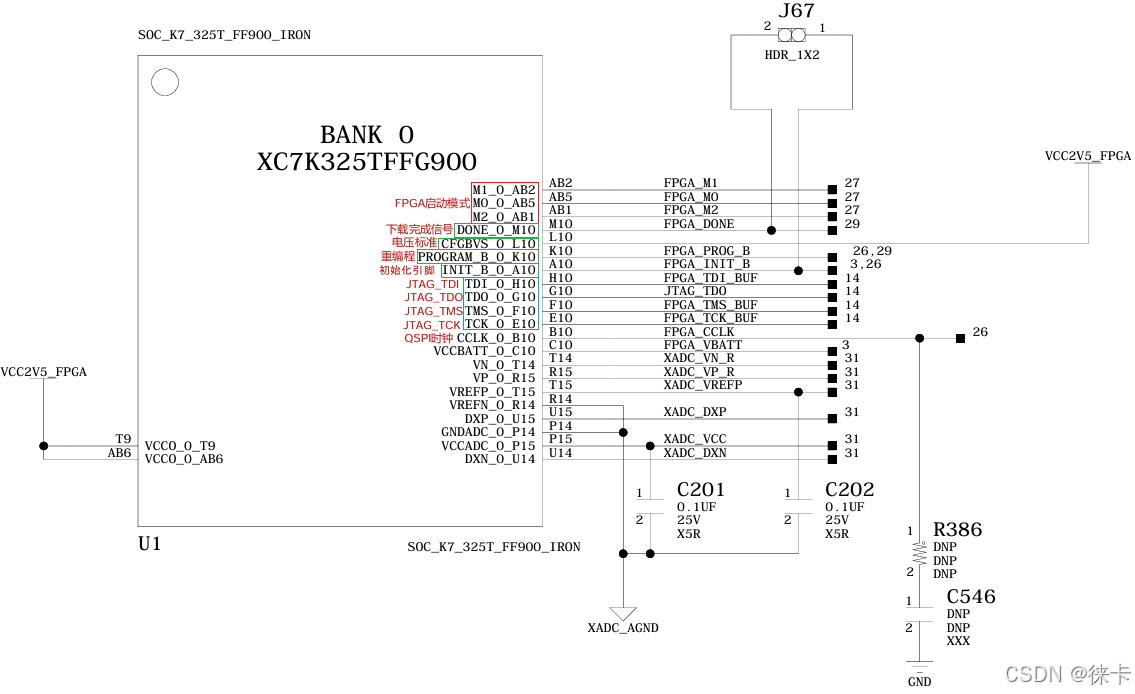

二、配置BANK0

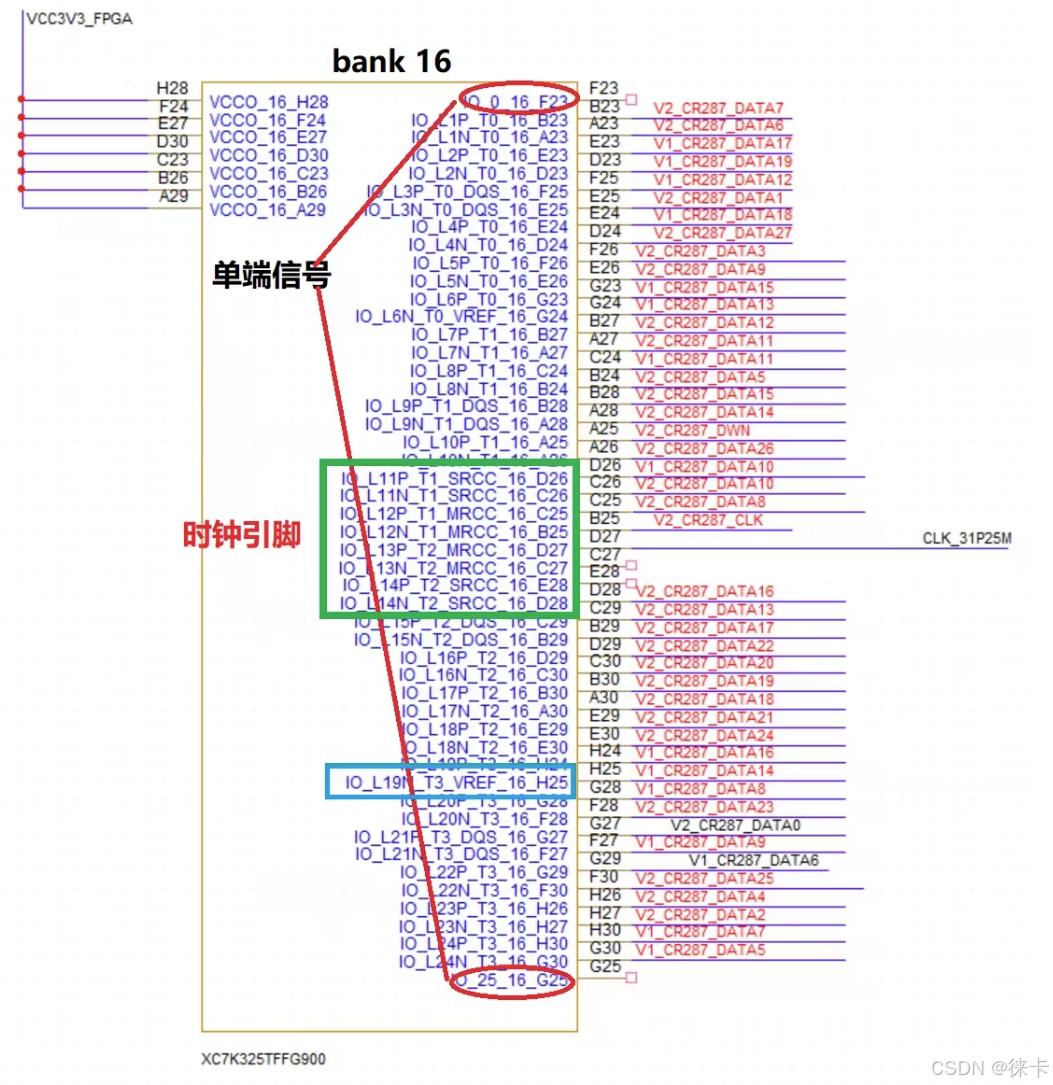

三、用户BANK(HR_HP)

FPGA的器件管脚按照Bank进行划分,每个Bank独立供电,以使FPGA I/O适应不同电压标准,增强I/O设计的灵活性。

每个用户Bank包括50个I/O管脚或者24对差分对管脚(48个差分信号),顶端和底端各一个单端管脚。

红色圈住的为两个单端信号,绿色圈住的管脚不用作时钟输入时,可以作为用户I/O来使用。

蓝色标记的VREF管脚,当该BANK I/O用作DDR内存接口时,需要提供伪差分所需的阈值电压,此时_VREF_管脚需要接DDR外设要求的参考电压。

RCC引脚为时钟专用引脚,分为MRCC(全局时钟)与SRCC(单端)

三、K7系列 IO速率与bank有关,通常高速在HP bank

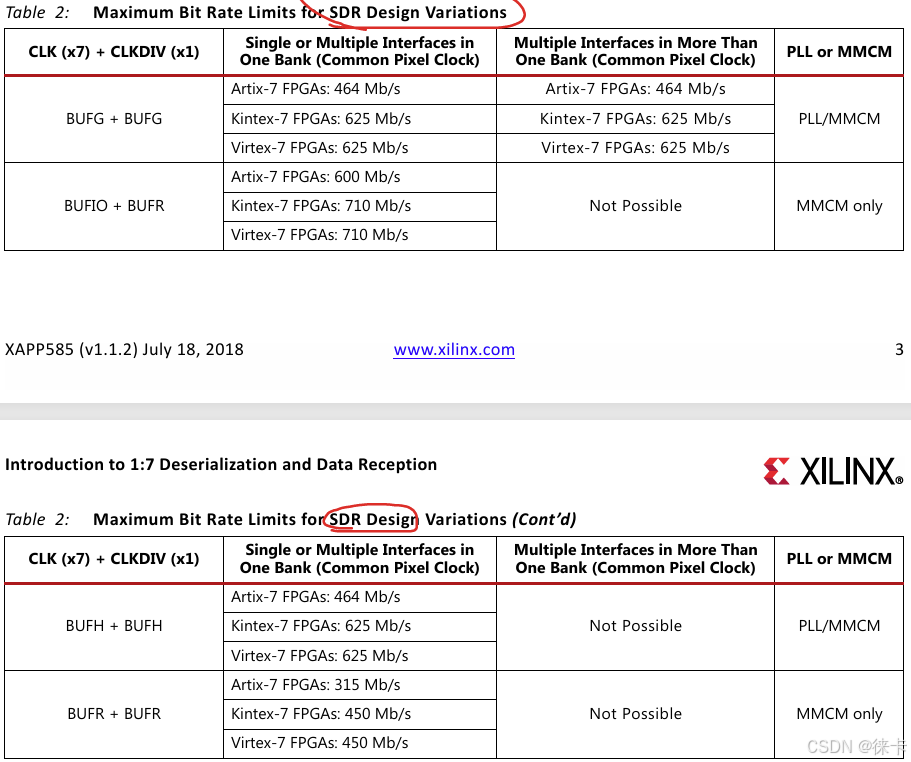

3.1单边沿

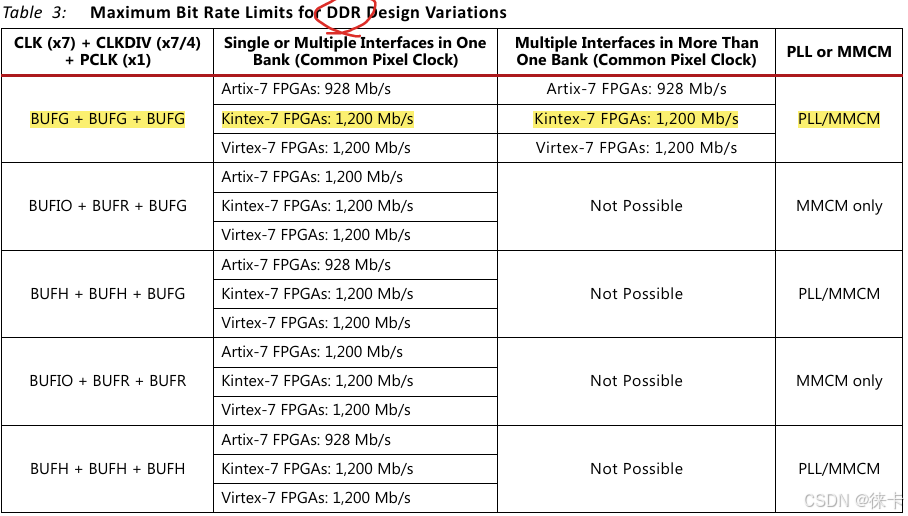

3.2双边沿

总结

仅供个人学习

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?