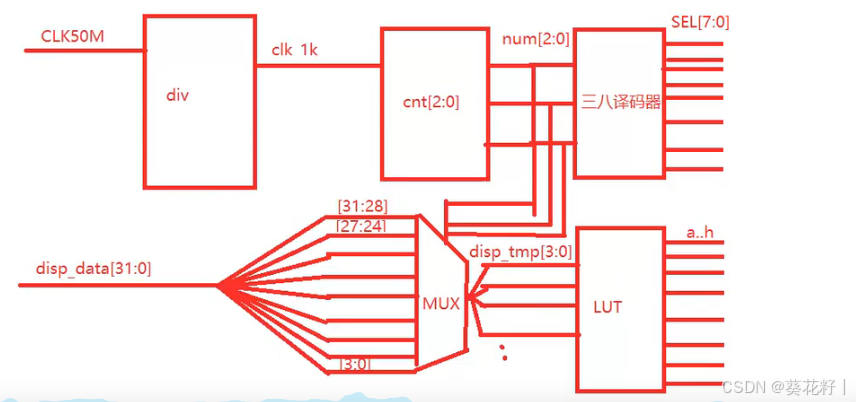

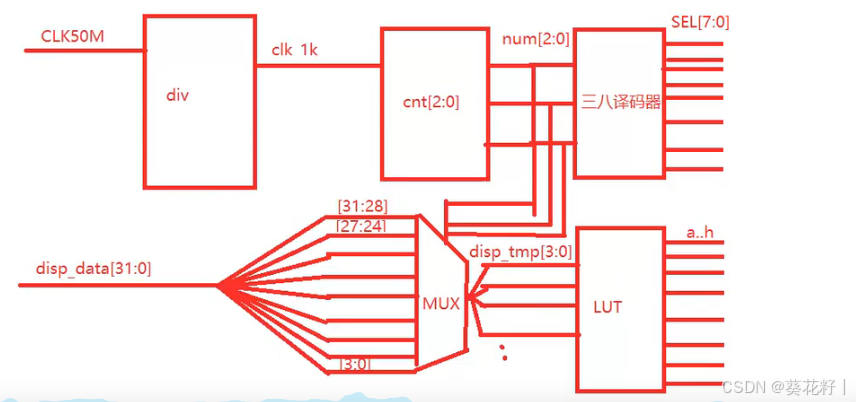

分析

逻辑代码:

module nixie_tube(

clk,

rst_n,

disp_data,

sel,

seg

);

input clk;

input rst_n;

input [31:0]disp_data; //输入需要显示的数据

output reg[7:0]sel; //选择数码管

output reg[7:0]seg; //8个数码管;seg[0]=a,seg[1]=b,...seg[7]=h

reg clk_1k;

reg[15:0]div_cnt;

always@(posedge clk or negedge rst_n)

if(!rst_n)

div_cnt <= 0;

else if (div_cnt >= 49999)//计数1ms

div_cnt <= 0;

else

div_cnt <= div_cnt + 1;

//产生1K的使能时钟

always@(posedge clk or negedge rst_n)

if(!rst_n)

clk_1k <= 0;

else if(div_cnt == 49999)

clk_1k <= 1'b1 ;

else

clk_1k <= 0;

reg [2:0]num_cnt; //选择数码管计数

always@(posedge clk_1k or negedge rst_n)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7575

7575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?