DDS基本原理

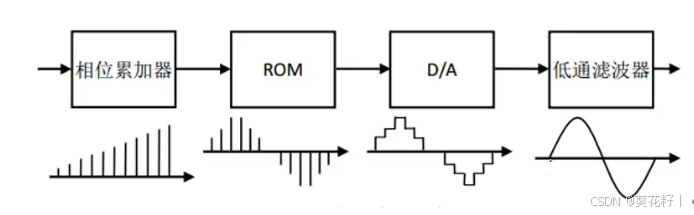

DDS(Direct Digital Synthesizer)即数字合成器,是一种新型的频率合成技术,具有相对带宽大,频率转换时间短,分辨率高,相位连续性好等优点。比较容易实现频率、相位以及幅度的数控调制,广泛应用与通信领域。

DDS的功能:产生一个高精度的信号源,如正弦波,三角波,方波等。

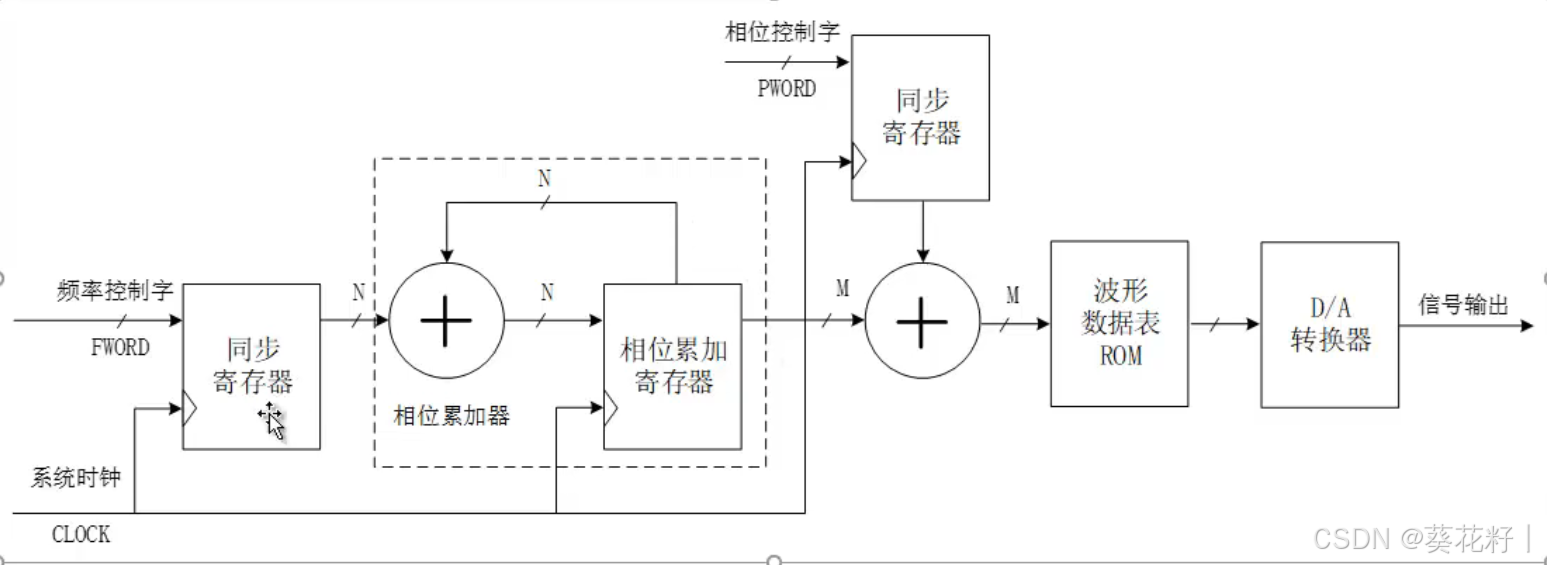

DDS的基本结构

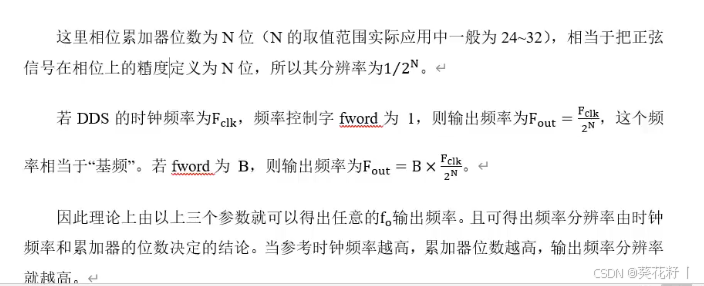

频率控制字:采样间隔

相位控制字:取ROM地址时加的偏移地址

使用Mif精灵生成数据表

参考我的上一篇文章

FPGA学习:使用Mif精灵初始化BOM,生成波形数据表-优快云博客

DDS正弦波实现

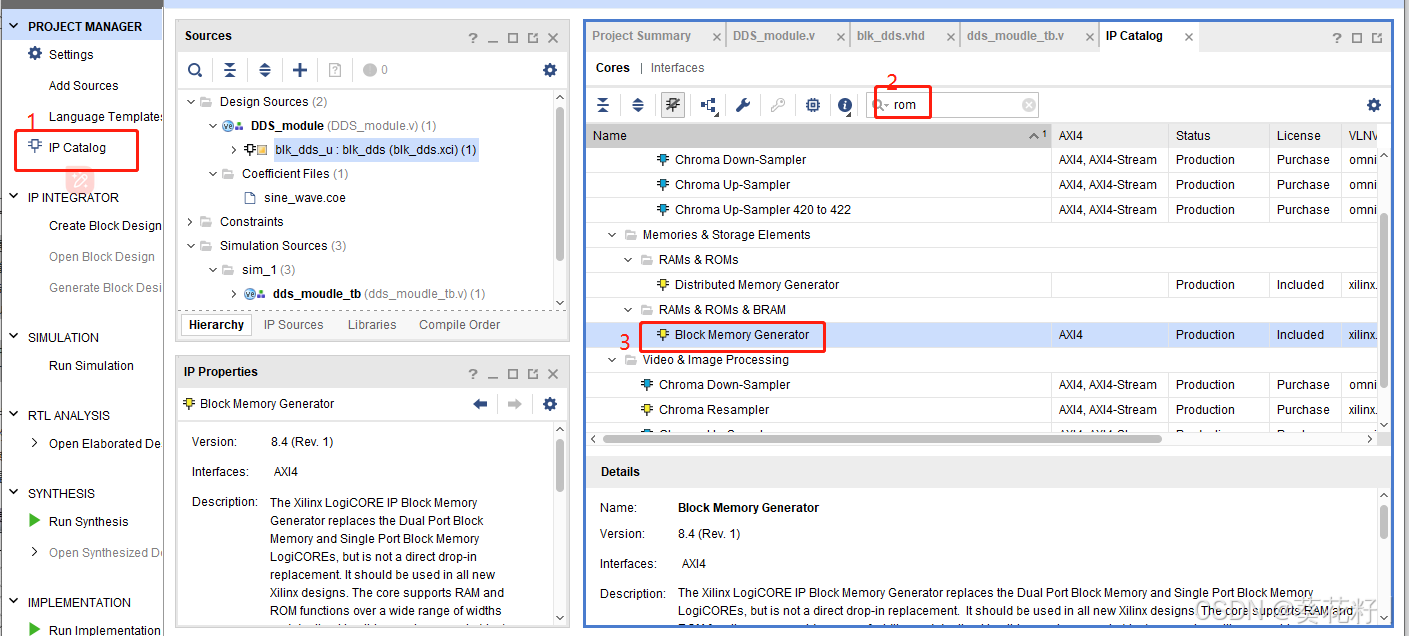

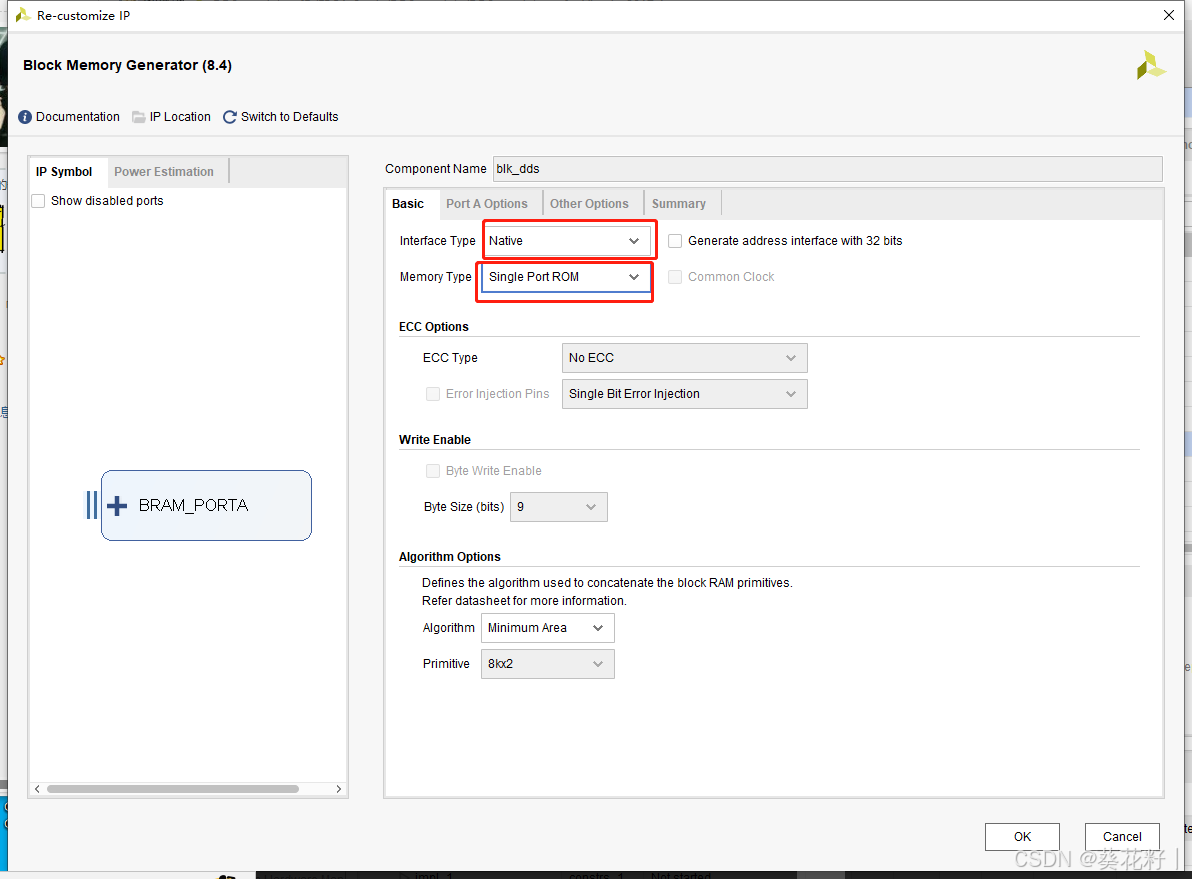

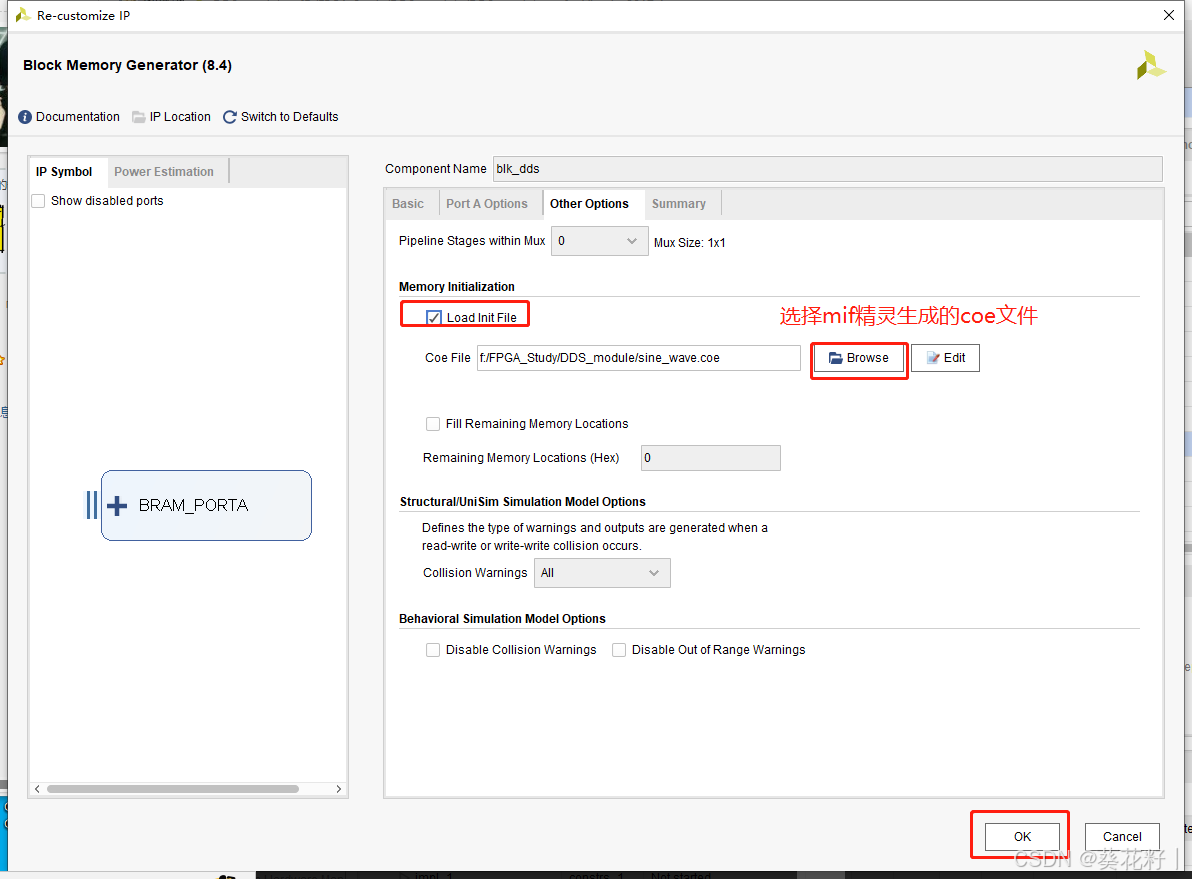

调用ROM ip核

一、

二、

三、

四、

逻辑代码

module DDS_module(

clk,

rst_n,

Fword,

Pword,

data

);

input clk;

input rst_n;

input [31:0]Fword;

input [11:0]Pword;

output [13:0]data;

//频率控制字同步寄存器

reg [31:0]Fword_r;

always@(posedge clk)

Fword_r <= Fword;

//相位控制字同步寄存器

reg [11:0]Pword_r;

always@(posedge clk)

Pword_r <= Pword;

//相位累加器

reg[31:0]Freq_ACC;

always@(posedge clk or negedge rst_n)

if(!rst_n)

Freq_ACC <= 0;

else

Freq_ACC <= Fword_r + Freq_ACC ;

//波形数据表地址

wire [11:0]Rom_Dddr;

assign Rom_Dddr = Freq_ACC[31:20] + Pword;

blk_dds blk_dds_u(

. clka (clk),

. addra(Rom_Dddr),

. douta(data)

);

endmodule

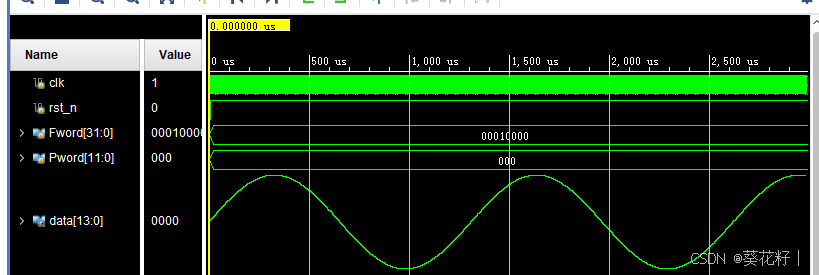

仿真

`timescale 1ns / 1ps

module dds_moudle_tb(

);

reg clk;

reg rst_n;

reg [31:0]Fword;

reg [11:0]Pword;

wire [13:0]data;

DDS_module DDS_module_u(

.clk (clk),

.rst_n (rst_n),

.Fword (Fword),

.Pword (Pword),

.data (data)

);

initial clk =1;

always #10 clk = ~clk;

initial begin

rst_n = 0;

Fword = 65536;

Pword = 0;

#201

rst_n = 1;

#20000000;

Fword = 65536 * 1024;

#20000000;

Fword = 65536 * 32;

#20000000;

$stop;

end

endmodule

1238

1238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?