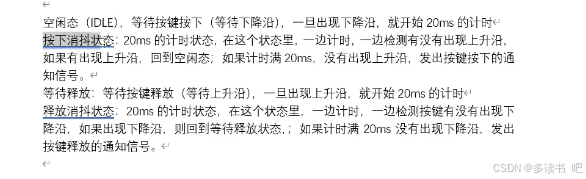

分析:

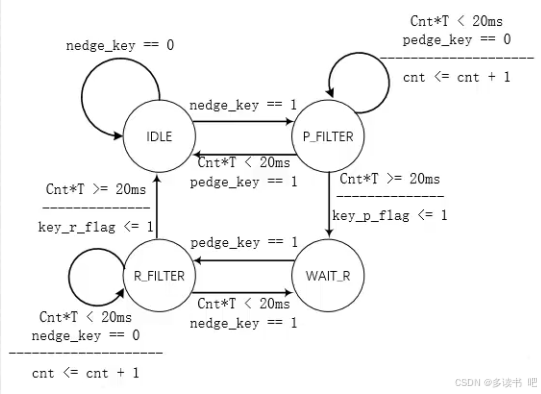

状态转移图:

逻辑代码:

module key_flier(

clk,

rst_n,

key,

key_p_flag,

key_r_flag

);

input clk;

input rst_n;

input key;

output reg key_p_flag;

output reg key_r_flag;

parameter TIME =20'd1000_000;//clk=50M,TIME=20000000/20=1000000

reg[1:0]state;

reg [19:0]counter;

wire nedge_key;

wire pedge_key;

reg key_dly;

always@(posedge clk )

key_dly <= key;

assign nedge_key = ((key == 0)&&(key_dly == 1));

assign pedge_key = ((key == 1)&&(key_dly == 0));

always@(posedge clk or negedge rst_n)

if(!rst_n)begin

counter <= 0;

key_p_flag <= 0;

key_r_flag <= 0;

state <= 0;

end

else case(state)

2'd0 : begin

if(nedge_key)begin

state <= 1;

key_r_flag <= 0;

end

else begin

state <= 0;

end

end

2'd1 : begin

if(counter < TIME - 1)

if(pedge_key)begin

counter <= 0;

state <= 0;

end

else begin

counter <= counter + 1;

state <= 1;

end

else begin

key_p_flag <= 1;

counter <= 0;

state <= 2;

end

end

2'd2 : begin

if(pedge_key) begin

key_p_flag <= 0;

state <= 3;

end

else begin

key_p_flag <= key_p_flag;

state <= 2;

end

end

2'd3 : begin

if(counter < TIME - 1)

if(nedge_key)begin

counter <= 0;

state <= 2;

end

else begin

counter <= counter + 1;

state <= 3;

end

else begin

key_r_flag <= 1;

counter <= 0;

state <= 0;

end

end

default : begin

counter <= 0;

key_p_flag <= 0;

key_r_flag <= 0;

state <= 0;

end

endcase

endmodule

仿真:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/11/20 16:45:51

// Design Name:

// Module Name: key_filter_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module key_filter_tb( );

reg clk;

reg rst_n;

reg key;

wire key_p_flag;

wire key_r_flag;

key_flier key_flier_u(

.clk (clk),

.rst_n (rst_n),

.key (key),

.key_p_flag (key_p_flag),

.key_r_flag (key_r_flag)

);

initial

clk = 1;

always #10 clk = ~clk;

initial begin

rst_n = 0;

key = 1;

#201;

rst_n = 1;

key = 0;

#201;

key = 1;

#2000;

key = 0;

#21000000;

key = 1;

#21000000;

key = 0;

#2000000;

$stop;

end

endmodule

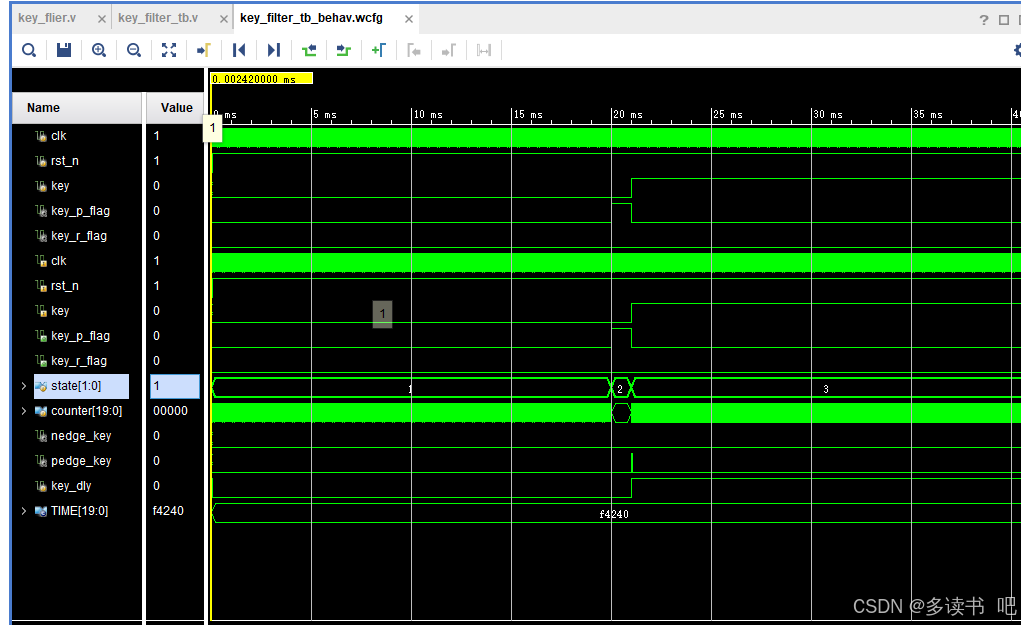

仿真结果:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?