一、概述

TileLink是一个芯片级互连标准,允许多个主设备,以支持一致性的存储器映射方式访问存储器和其他从设备。TileLink的设计目标是为片上系统提供一个具有低延迟和高吞吐率传输的高速、可扩展的片上互连方式,来连接通用多处理器、协处理器、加速器、DMA以及各类简单或复杂的设备

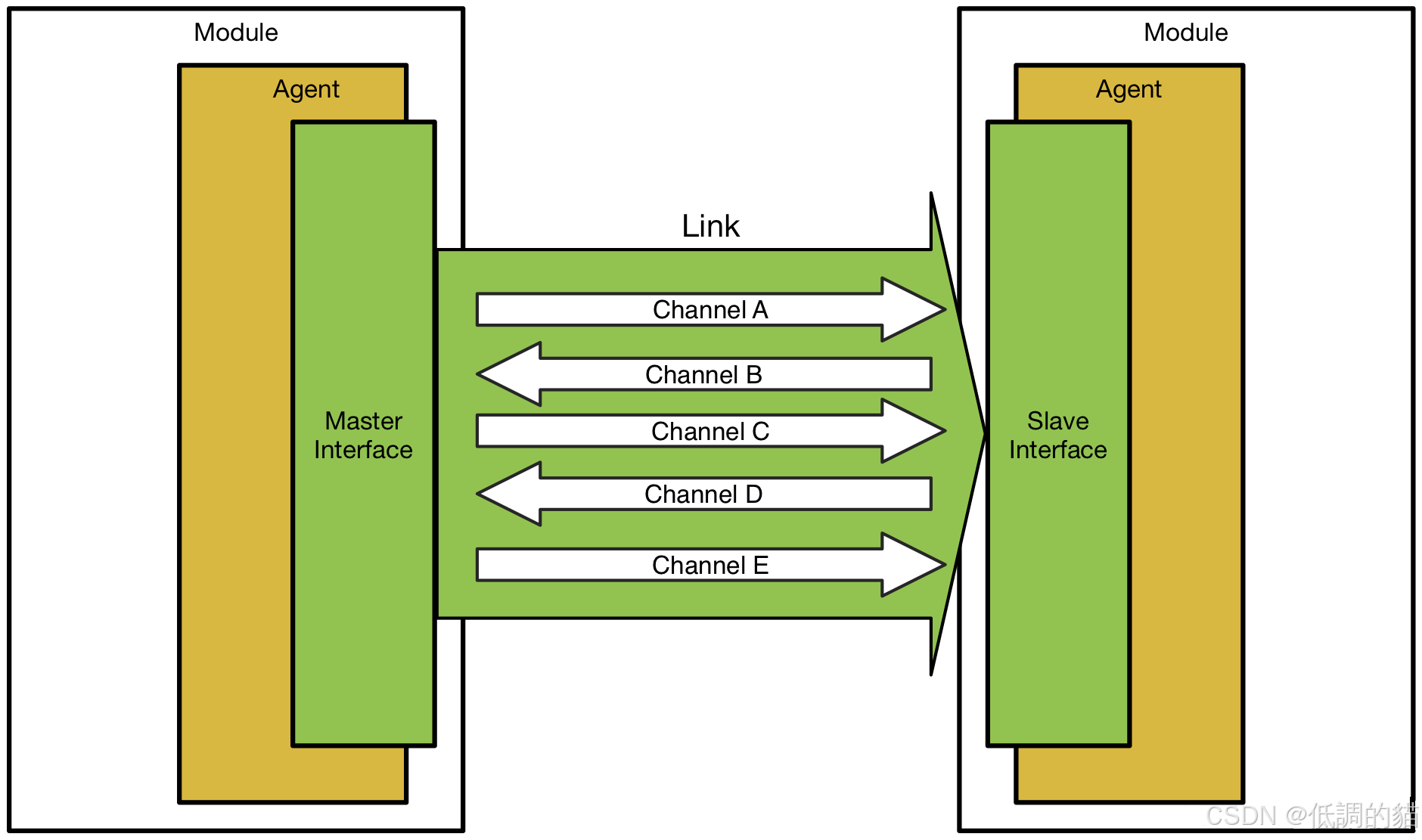

TileLink 协议一共有3种,TL-C 包括A、B、C、D、E所有5个通道,TL-UL和TL-UH 只包含A和D两个通道。

访问存储器操作需要两个最基本的通道,

通道A:发送请求,访问指定地址范围或对数据进行缓存操作。

通道D:向请求者传送数据回复响应或是应答消息。

最高协议兼容层TL-C需要额外包含另外三个通道,具备管理数据缓存块权限的能力,

通道B:传输请求,对主代理已缓存的某个地址上的数据进行访问或是写回操作。

通道C:响应通道B的请求,传送数据或是应答消息。

通道E:传输来自请求者的缓存块传输的最终应答,用于序列化。

各个通道传递消息的优先级顺序是 A<B<C<D<E,设置优先级保证了消息在TileLink网络的传输过程中不会进入路由环路或是资源死锁。

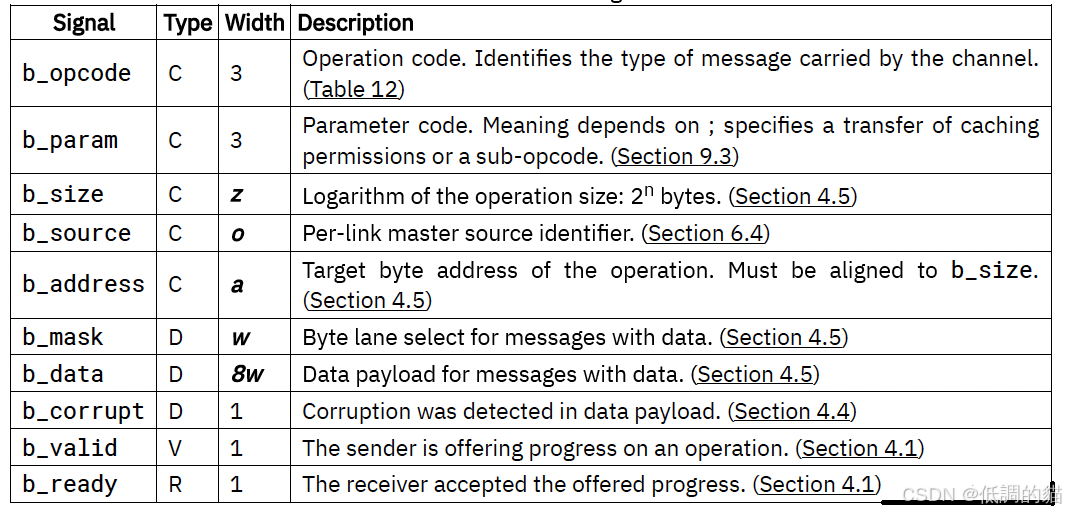

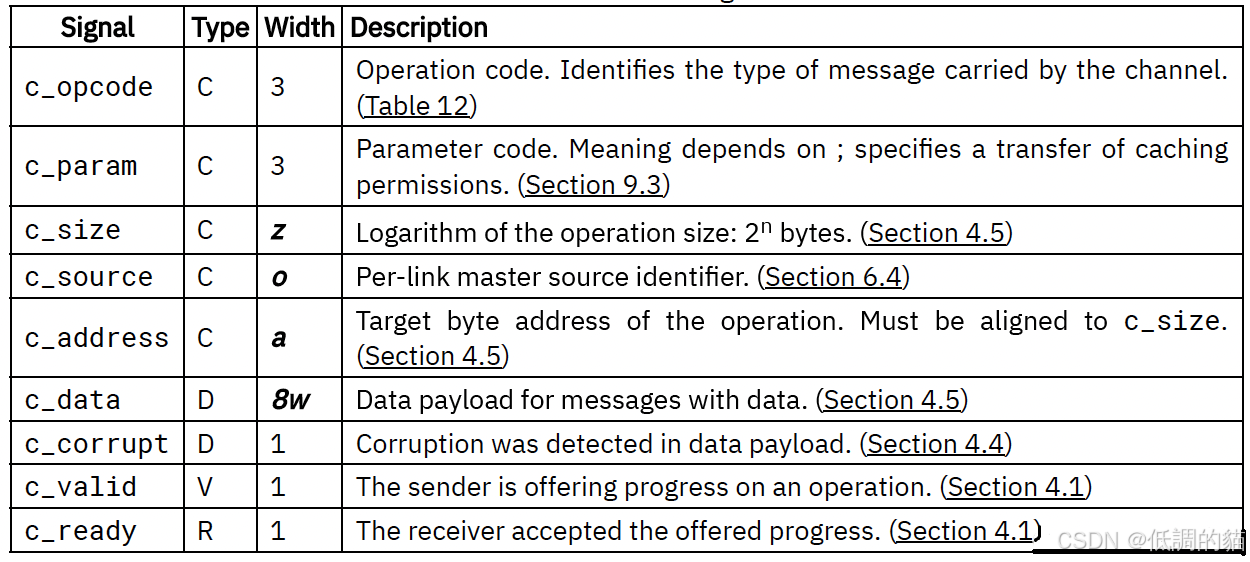

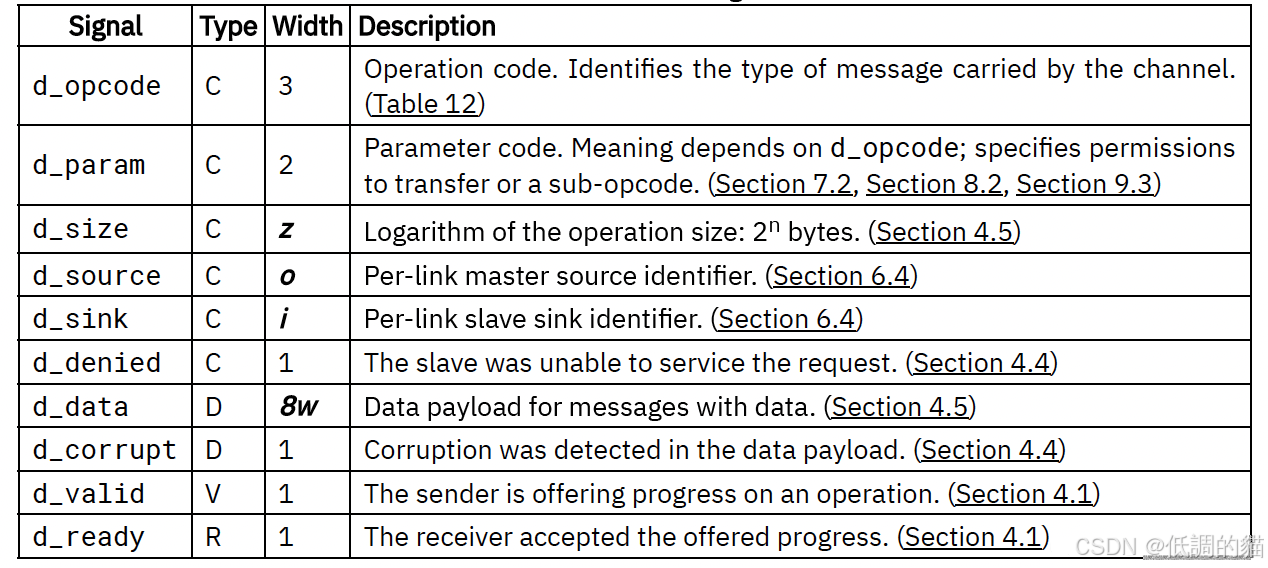

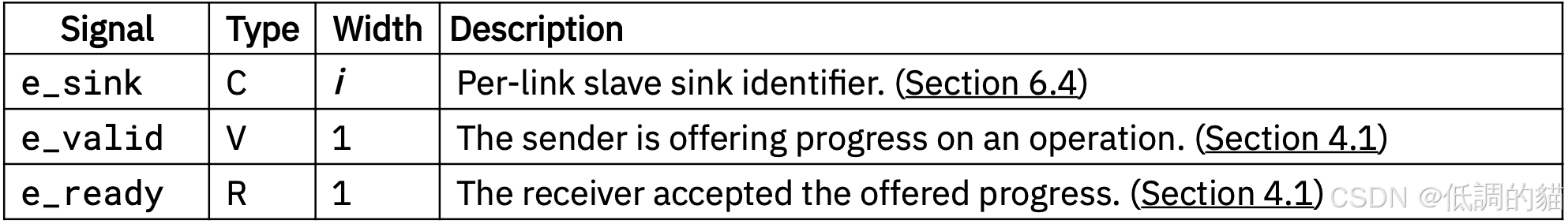

二、信号描述

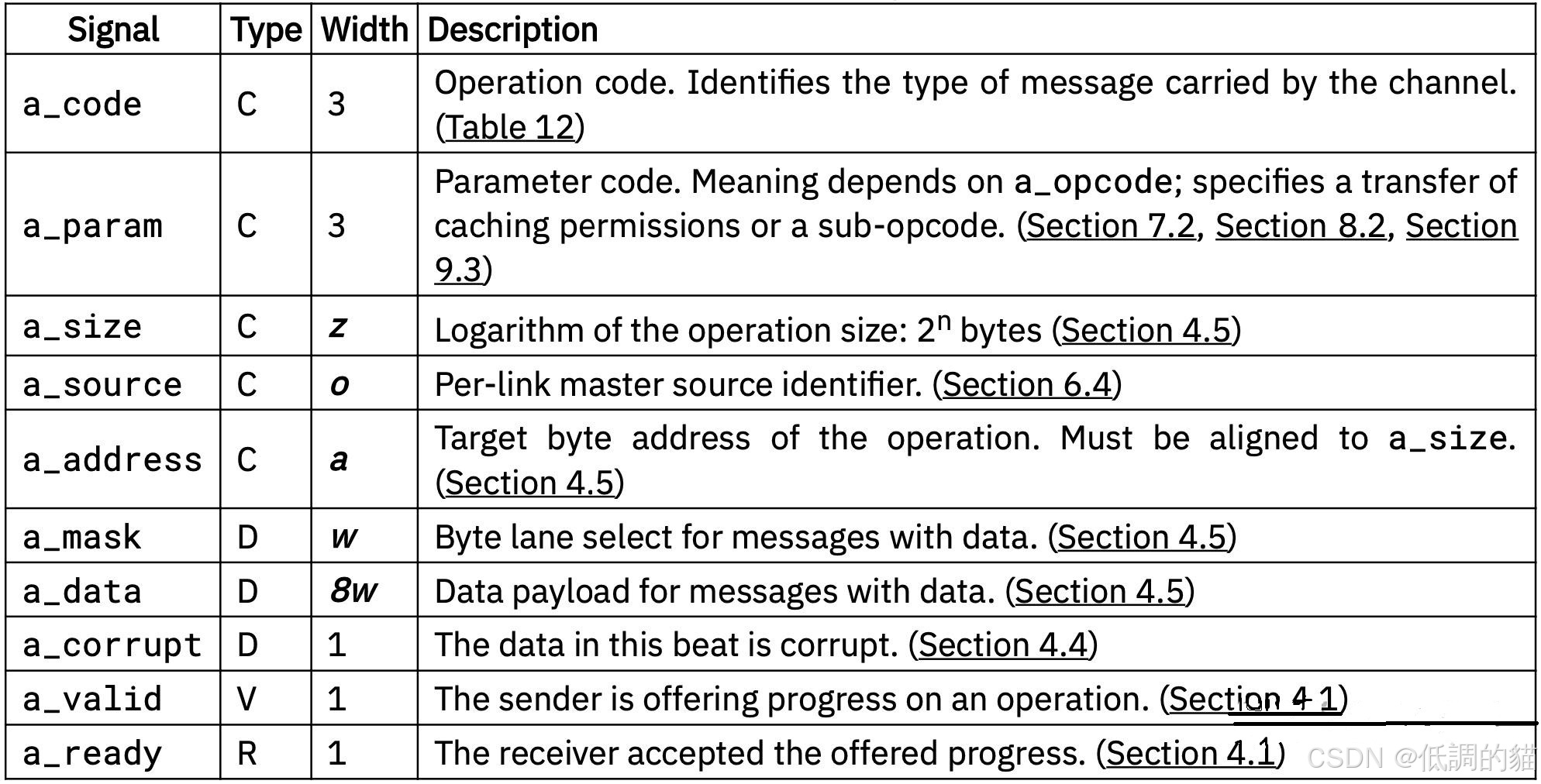

通道A是从主接口到从接口,发送到一个地址的请求消息。

通道B是从接口到主接口,用于向保存一个特定缓存块的主代理发送请求消息。

通道C是主接口到从接口,携带对通道B请求作为响应的消息发送给一个特定缓存数据块,也被用于自发地写回脏缓存数据。

通道D是从接口到主接口,携带对通道A发送到特定地址请求作出响应的消息,还携带了对于通道C自发写回的应答。

通道E是主接口到从接口,携带是否收到通道D响应消息的应答信号,用作操作序列化。

三、序列化

TileLink消息大多包含有效的数据载荷,根据消息和数据总线的大小,可能需要多个时钟周期才能完成,多拍信息被称为突发传输(burst)。没有数据载荷的消息会在单拍内完成。TileLink禁止在一个通道中插入来自不同消息的任何数据。一旦一个burst开始,发送方在burst的最后一个数据被接收方接收之前,都不得发送任何来自其他消息的任一个数据。

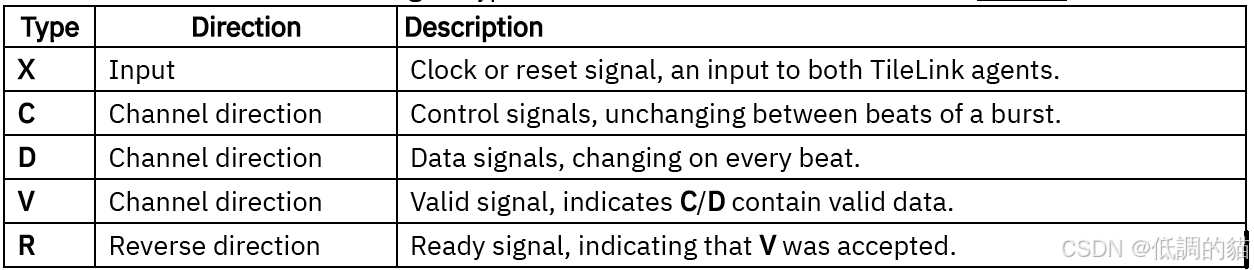

TileLink接收方拉高ready信号表示接收方可以接收数据,接收者拉低ready信号表示接收方正忙不能接收数据。数据的发送者拉高valid信号表示通道内的数据有效。只有当ready和valid同时被拉高时,数据才能被成功接收。

需要注意的是,ready和valid信号必须满足如下规则:

valid必须与ready信号独立,当发送方发送一个数据,必须拉高valid信号,同时该valid信号必须与接收方的ready信号独立。

从ready到valid信号以及任何数据和控制信号之间不能存在任何组合逻辑路径。

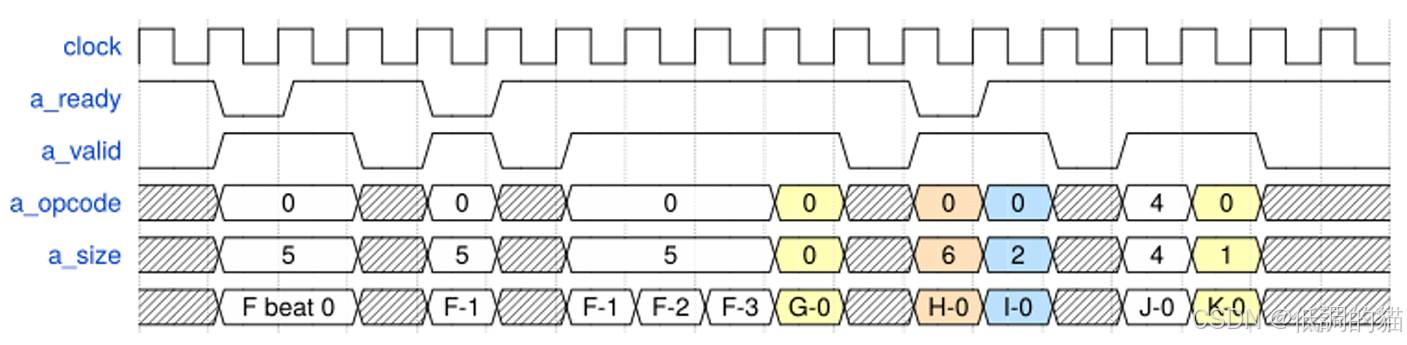

如下图所示为一个64bit的A通道中,6个消息的ready-valid信号实例。

这六个消息分别为F、G、H、I、J、K。

1. 消息F长度为2ˆ5=32字节,opcode标识了操作类型为PutFullData,表示消息F携带数据载荷。通道A一个时钟周期可以传输8个字节,故需要传输4个时钟周期才能完成,即F-0、F-1、F-2、F-3。一旦F-0被接收方成功接收后,发送端就必须发送剩余的数据直到最后一个数据F-3被成功接收。

2. 消息G长度为2ˆ0=1字节,opcode标识了操作类型为PutFullData,表示消息G携带数据载荷。1字节的数据载荷适合于传输单时钟周期数据,并立即发送,并被接收方成功接收。

3. 消息H长度为2ˆ6=64字节,opcode标识了操作类型为PutFullData,表示消息H携带数据载荷。需要传输8个时钟周期才能完成。由于发送方发送的第一个数据H-0被接收方拒绝接收,burst传输未被启动,故发送方放弃信息H的传输,接下来选择发送信息I。

4. 消息I长度为2ˆ2=4字节,opcode标识了操作类型为PutFullData,表示消息I携带数据载荷。4字节的数据载荷适合于传输单时钟周期数据,并立即发送,并被接收方成功接收。

5. 消息J长度为2ˆ4=16字节,opcode标识了操作类型为Get,表示消息J不携带数据载荷。因此单个时钟周期即被接收方成功接收。

6. 消息K长度为2ˆ1=2字节,opcode标识了操作类型为PutFullData,表示消息K携带数据载荷。2字节的数据载荷适合于传输单时钟周期数据,并立即发送,并被接收方成功接收。

四、传输实例

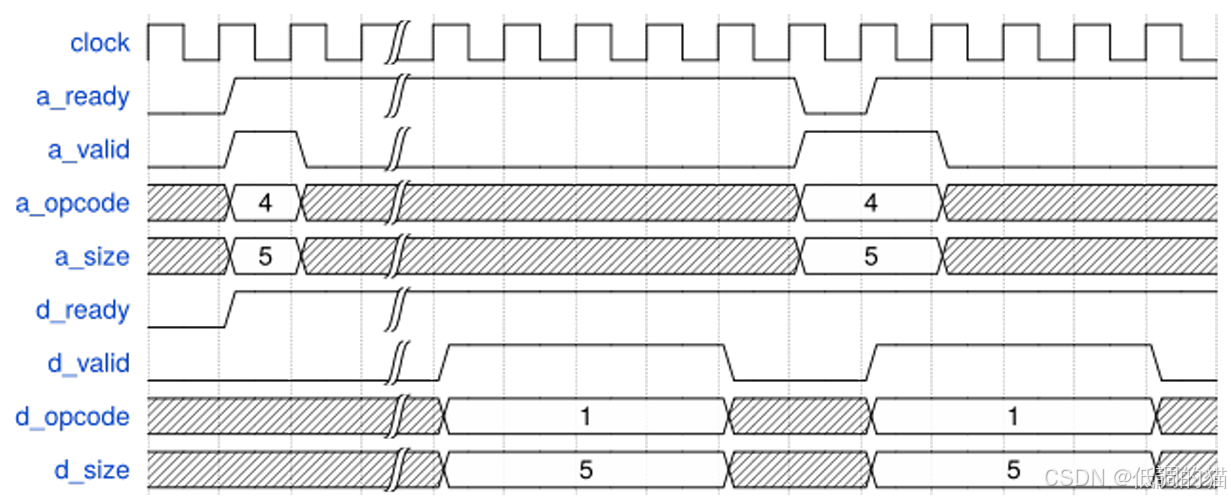

1. Get(4)和AccessAckData(1)在64bit宽度总线上的最小和最大延迟

Get操作从通道A发出,访问32字节,经过一定延迟后,AccessAckData回复的消息到达通道D。主端接收方必须能够无限期等待回复消息,因此TileLink网络中不存在超时设定。

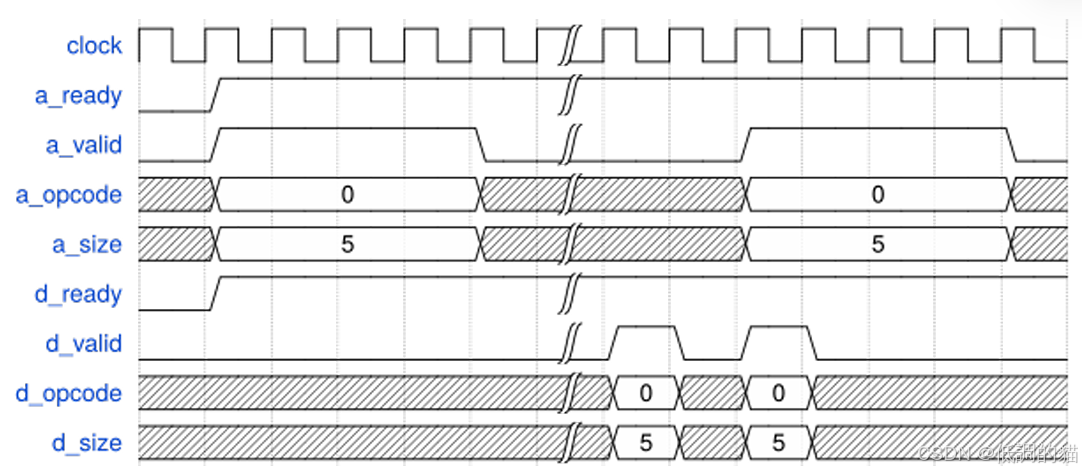

2. PutFullData (0) 和 AccessAck (0) 在一个64bit宽度总线上的最小与最大延迟

PutFullData操作请求消息在通道A发出,请求的AccessAck回复消息在通道D返回,AccessAck消息没有数据载荷。

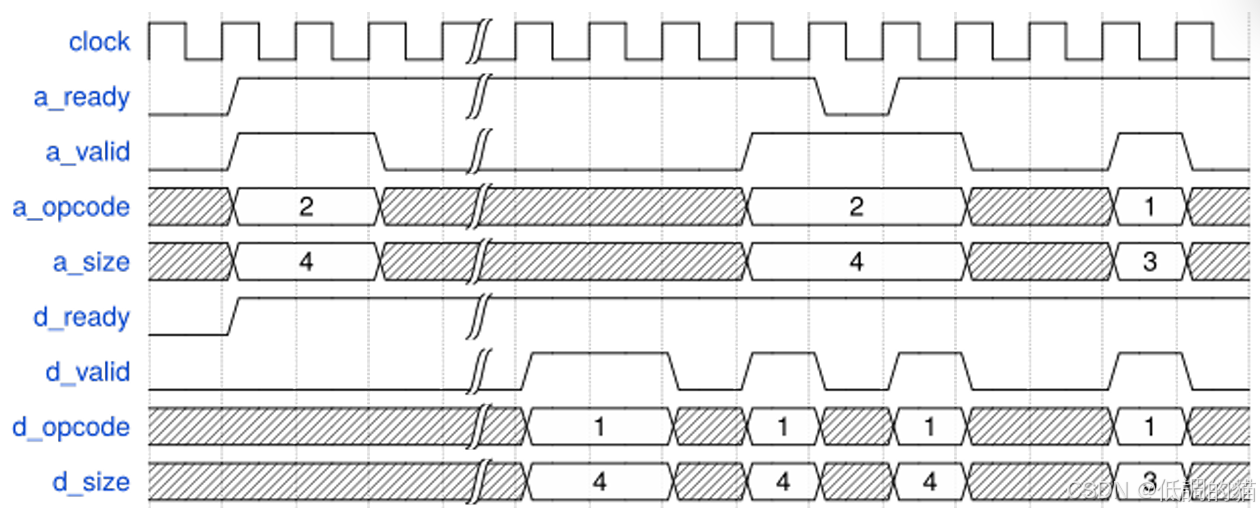

3. ArithmeticData (2) 和 AccessAckData (1) 在一个64bit宽度总线上的延迟

下图为携带有数据载荷的请求和响应消息的原子性操作。对于第一个16字节的请求消息,响应消息可能会在一定延迟后出现在通道D。

1009

1009

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?