在DC综合,PrimeTime静态时序分析之后,需要进行形式化验证,通过对比原始设计的*.v和DC综合后的门级网表*_netlist.v,输出对比结果。

1 启动Formality

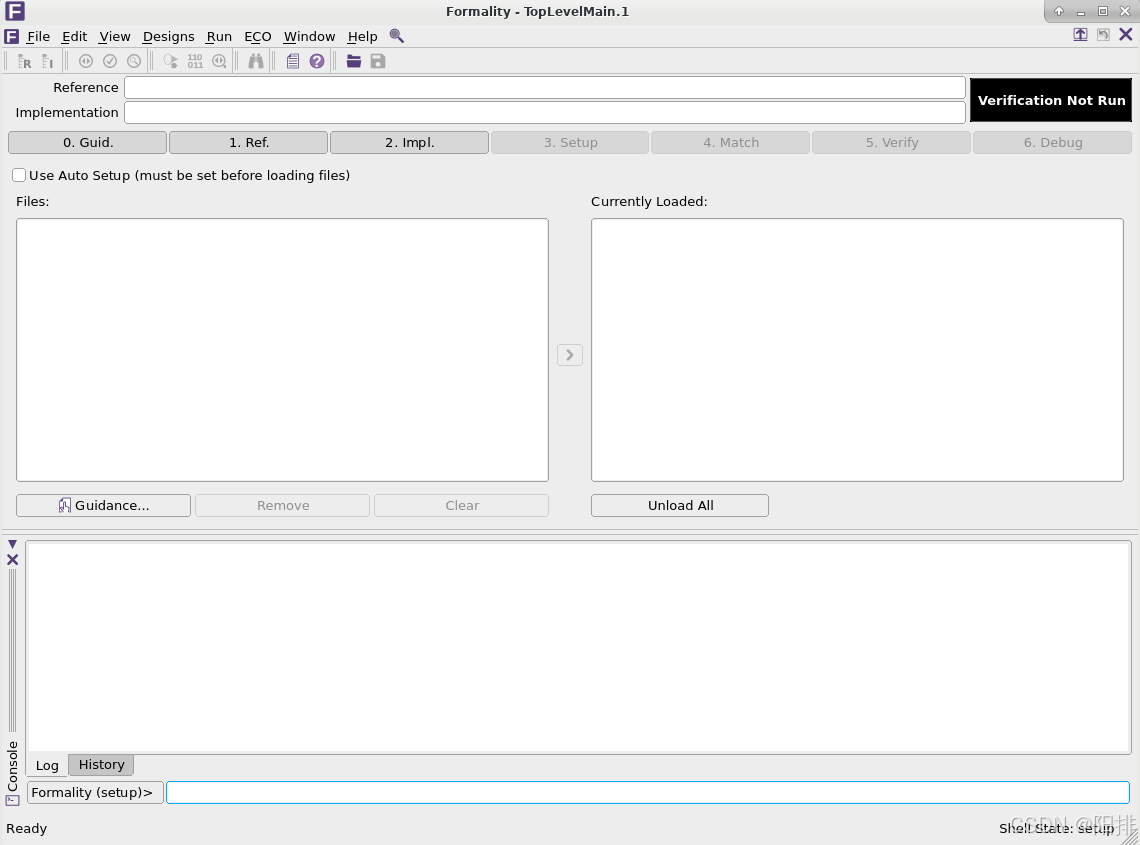

终端输入:Formality,打开图形化界面。

2 文件准备

1、GTECH库或者厂商提供的综合库:typical/slow/fast.db

2、原始设计文件:*.v/.vhd/.db等等

DC输出命令:write -format verilog -hier -output top_netlist.v

3、DC综合后的门级网表:*_netlist.v

4、DC综合过程中生成的*.svf文件。

DC中的命令为:set_svf output/$design_name.svf

3 软件使用

0. Guid.

1、点击Guidance,添加.svf文件。

2、选中svf文件,点击Load File。

1. Ref.

-

Read Design Files

选择对应的原始设计文件,需要选择所有的。

如果是*.v文件,则点击Verilog,然后将所有*.v文件Load Files。 -

Read DB Libraries

可以不进行操作。 -

Set Top Design

选择设计的顶层文件,然后点击右侧的Set Top。

2. Impl.

-

Read Design Files

选择DC综合后的网表文件。

如果是*_netlist.v文件,则点击Verilog导入,然后将该Load Files。 -

Read DB Libraries

必须进行操作,将厂商提供的typical/slow/fast.db导入。然后点击向右的箭头将该库Load。 -

Set Top Design

选择设计的顶层文件,然后点击右侧的Set Top。

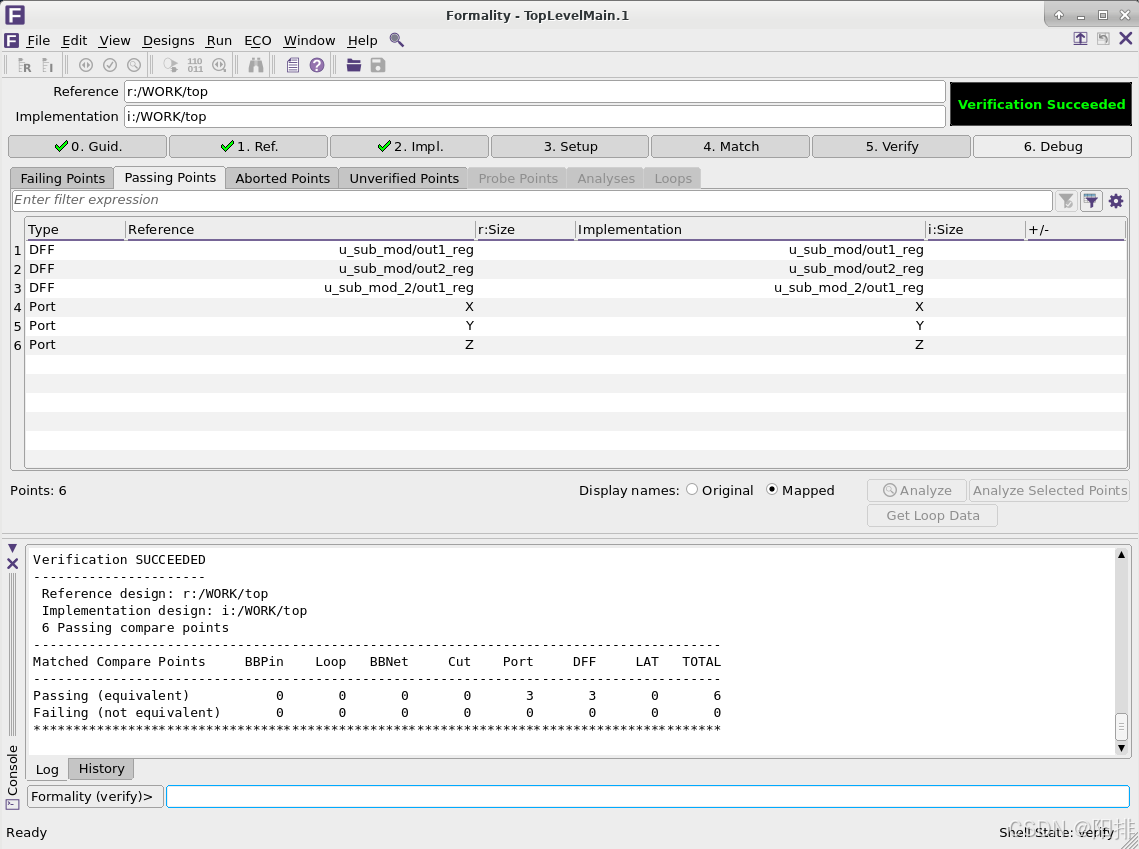

3. Setup

可以查看Failling Points、Passing Points、Abroted Points、Unverified Points。

4. Match

点击Run Matching,对Reference Design和Implementation Design的比较点进行匹配。

会输出matched和unmatched的点数。成功的话,unmatched的点数为0。

5. Verify

点击Verify All进行验证。

成功后会输出Verification succeeded。

6. Debug

略

4 脚本使用

每次验证都需要一项一项点击就比较麻烦,可以写一个run.tcl脚本,每次只需要source一下就能直接运行验证。

set_svf -append { ../test.svf }

read_verilog -container r -libname WORK -05 { ../src/sub_mod_2.v ../src/sub_mod.v ../src/top.v }

set_top r:/WORK/top

read_verilog -container i -libname WORK -05 { ../output/top_netlist.v }

read_db { ../lib/slow.db }

set_top i:/WORK/top

match

verify

file mkdir report

report_status > ./report/report_status.txt

report_designs > ./report/report_design.txt

report_hierarchy > ./report/report_hierarchy.txt

report_failing_points > ./report/report_failing_points.txt

#quit

在formality(setup)>命令行中输入:source run.tcl,即可运行形式化验证,然后在report中查看验证情况。

参考文章

https://blog.youkuaiyun.com/qq_42922513/article/details/131305494

https://blog.youkuaiyun.com/weixin_66225643/article/details/144558013

7620

7620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?