提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

提示:以下是本篇文章正文内容,下面案例可供参考

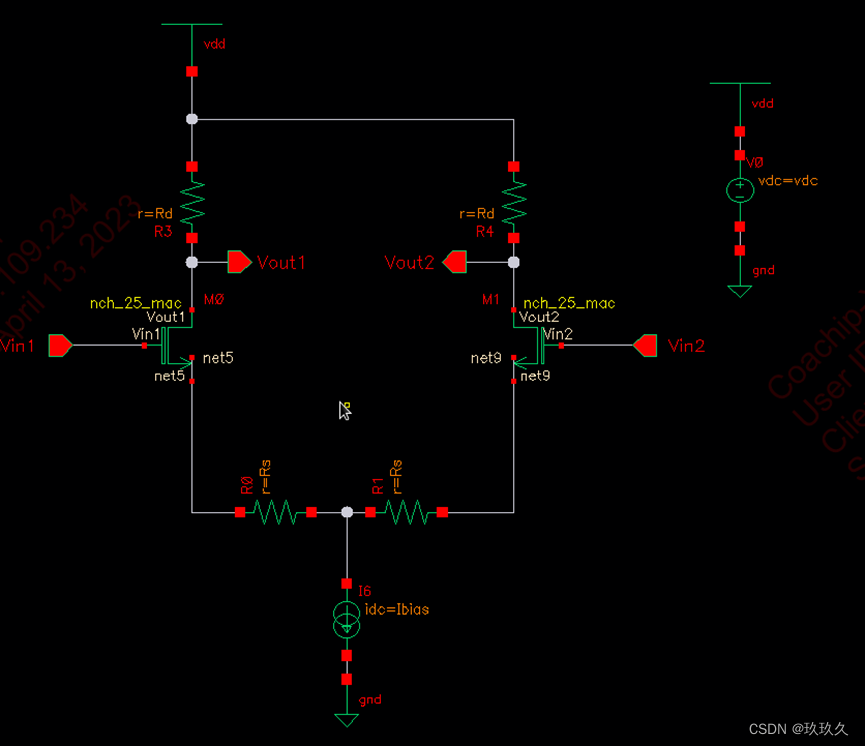

1. 电路原理图

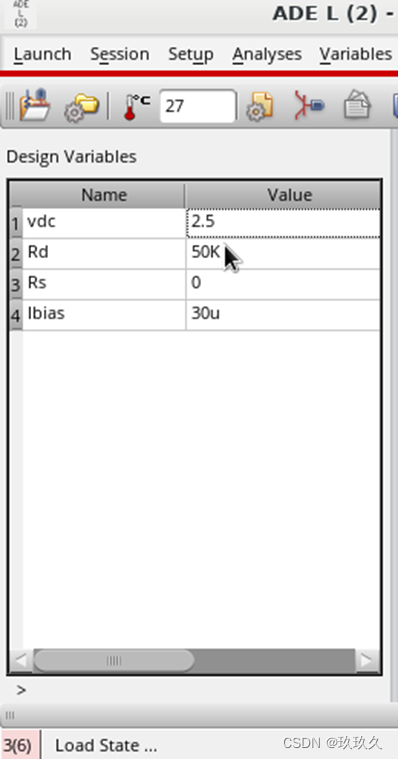

2. 仿真设计

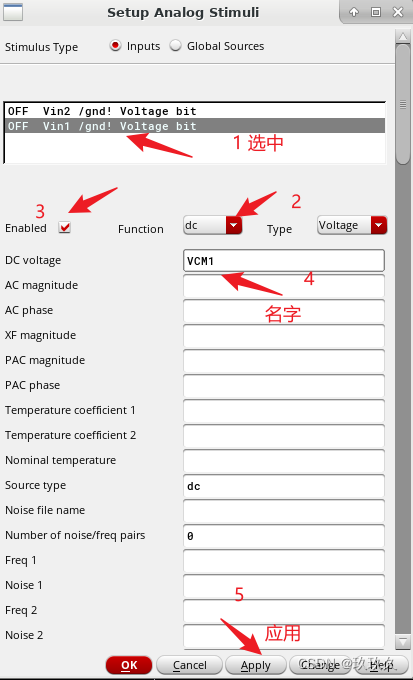

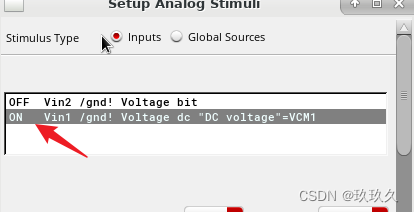

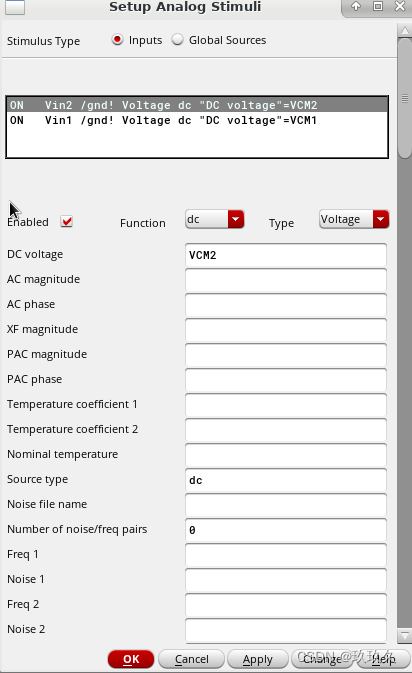

设置PIN端Vin1,Vin2为变量

说明 Vin1的直流电压是VCM1,同理设置Vin2

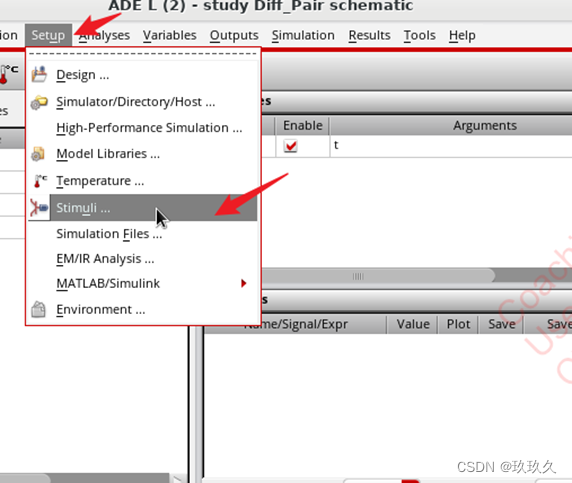

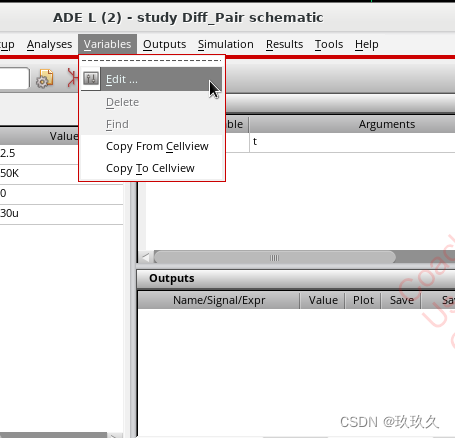

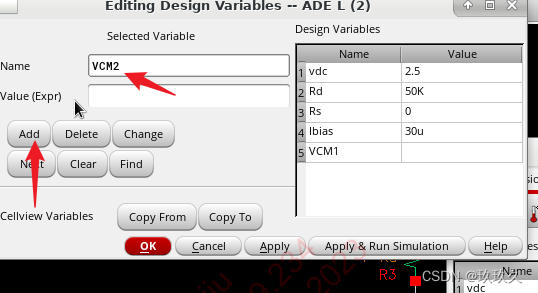

怎么加入变量呢

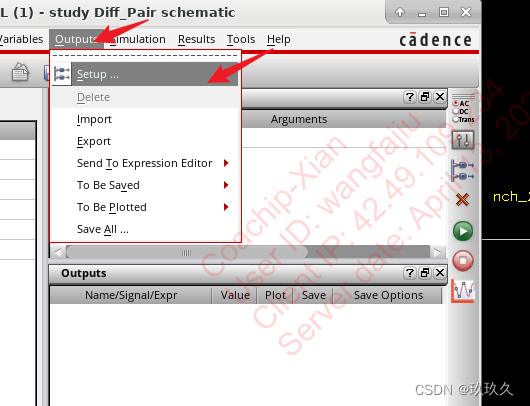

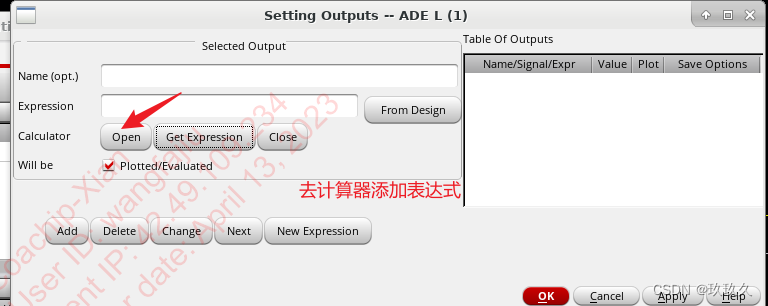

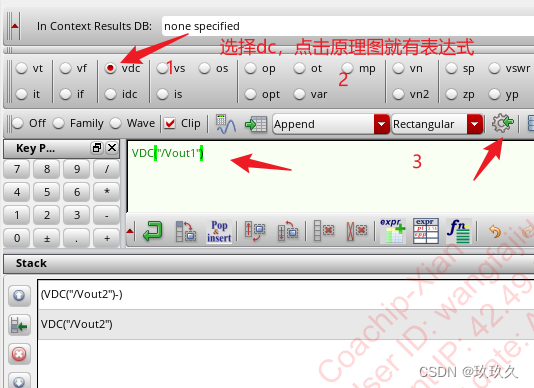

3. 建立输出

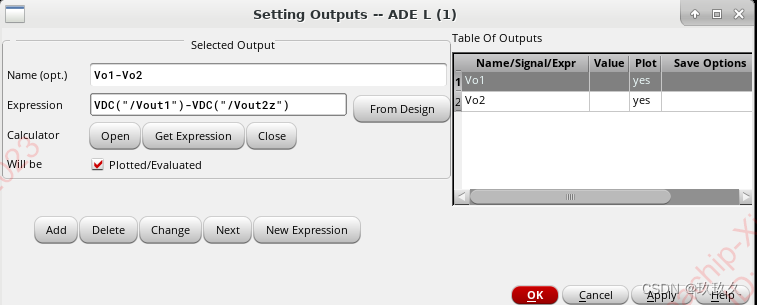

现在定义Vo1 - Vo2

同样添加输出就在里面设计,复制改数字就完了

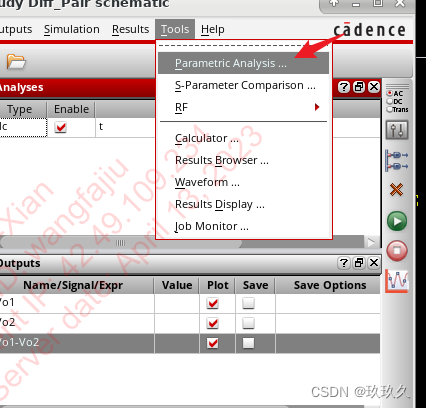

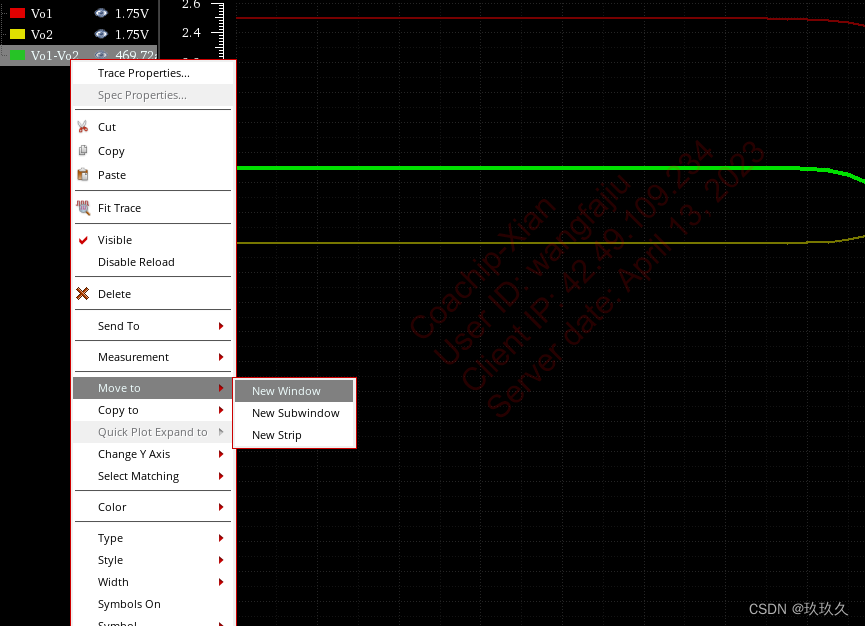

4. 参数扫描

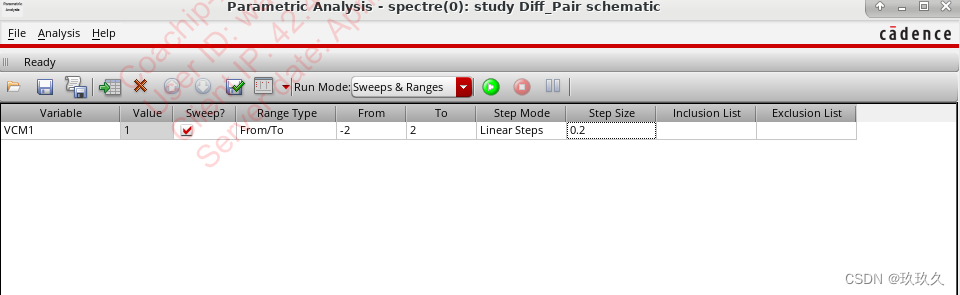

给VCM1一组值来仿真一下输出输入

V出现直线 可以按q矫正点位

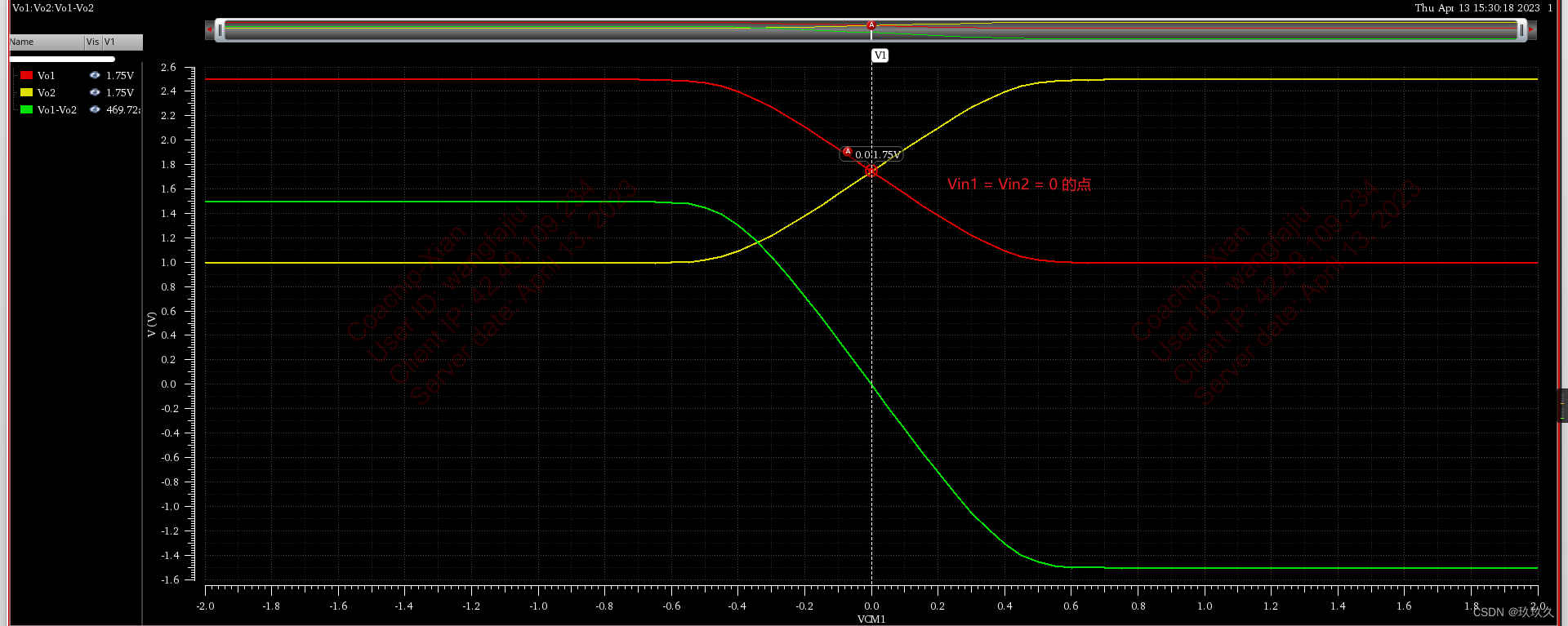

如何移出曲线

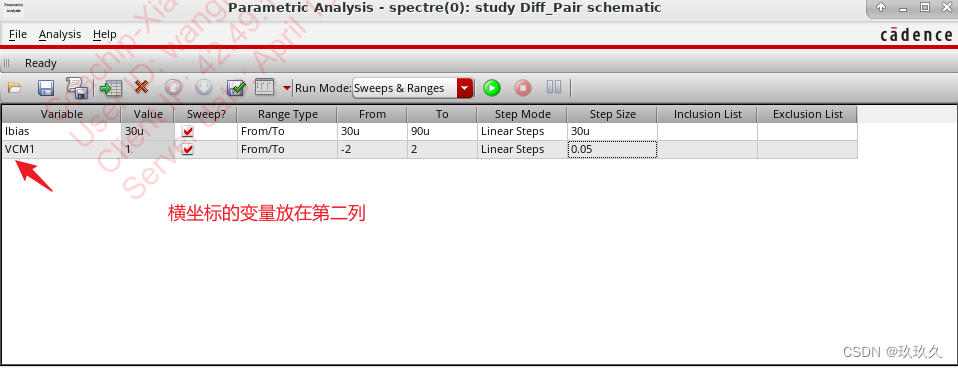

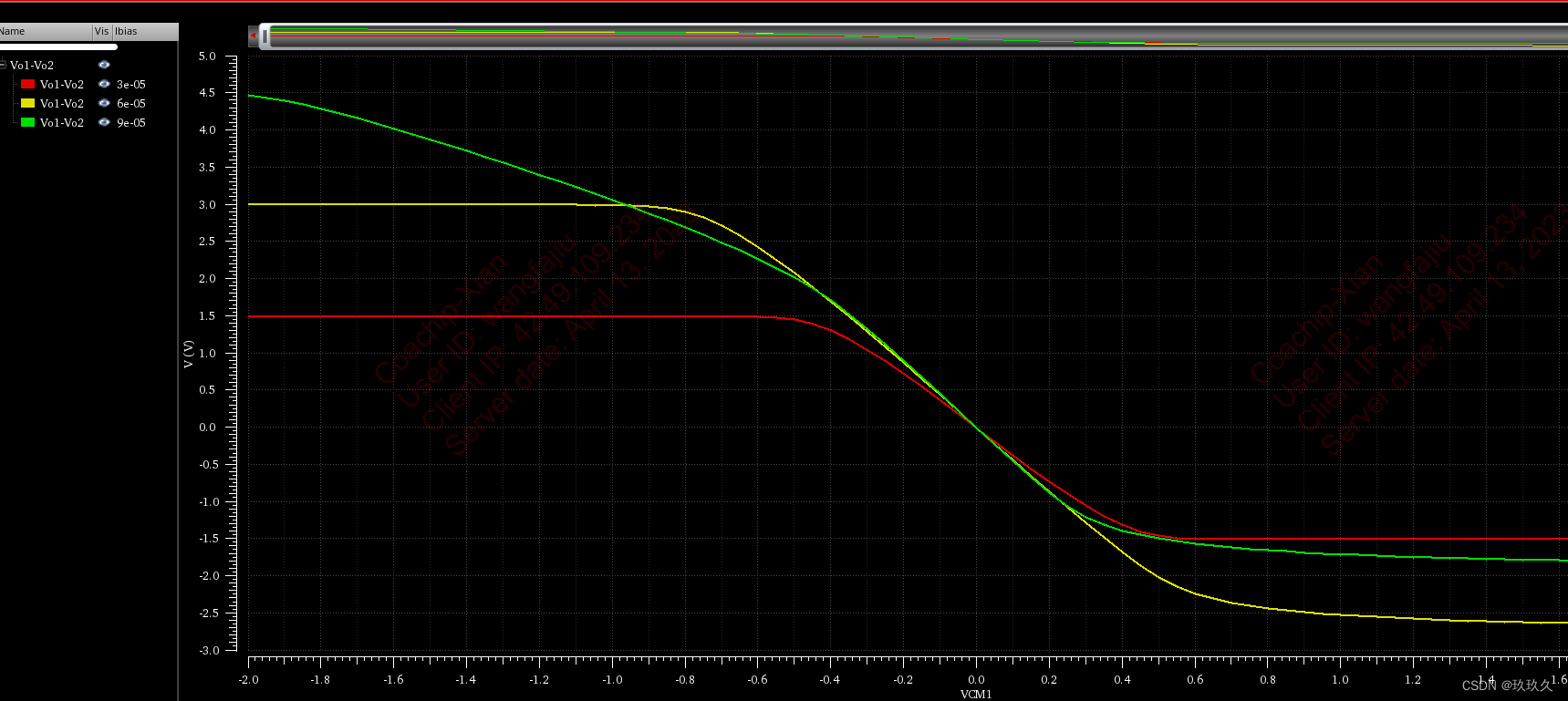

现在观察尾电流不同时,输入输出关系,横坐标的变量放在第二列

我们设置VCM2 = 0 ,实际上VCM1就是差模输入电压 .也就是差模电压放在横坐标,看电流源不同的曲线

我在想如果VCM2不是0,而是一个变化的值,该怎么样设计呢?是要在直流仿真Design Variable设计VCM2,再去参数扫描VCM1吗?这样当VCM1 = VCM2就是共模电压了

1043

1043

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?