本节主要介绍uvm启动过程和phase机制实现原理。介绍的方式将从整个环境的入口函数run_test开始。

1、top_tb:run_test

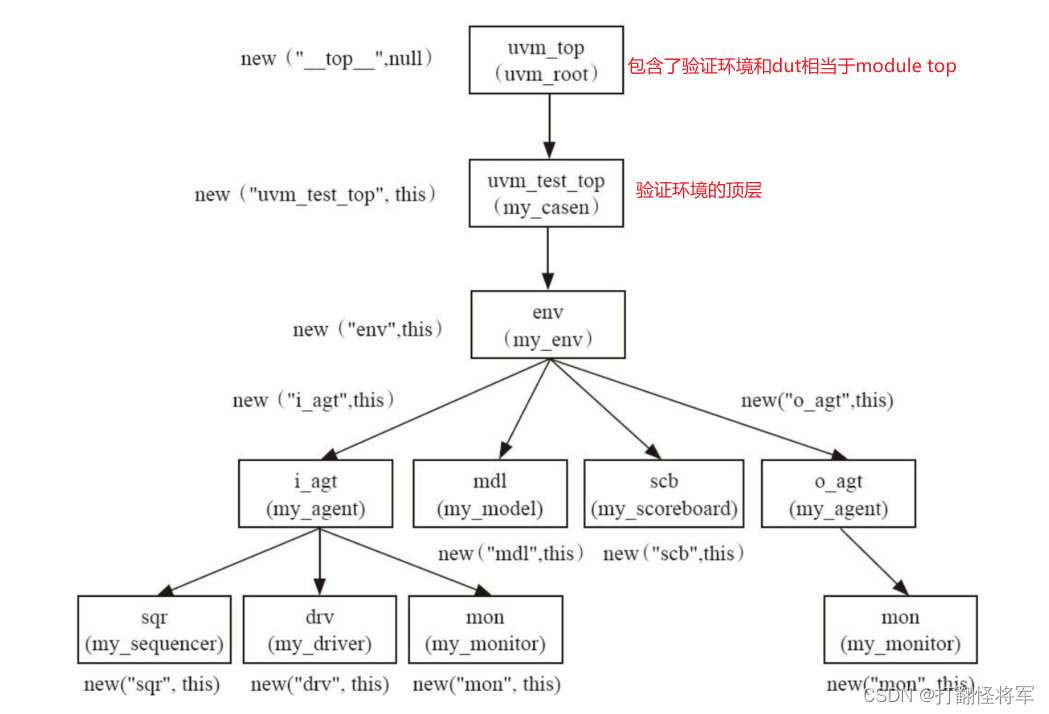

我们的验证最顶层就是top_tb(harness), 在内部实例化dut,然后调用run_test函数,他会实例化一个脱离了top_tb层次结构的实例uvm_test_top,建立一个新的层次结构。这是uvm验证平台最顶层的入口。

module top();

import uvm_pkg::*;

......

initial begin

run_test();

end

......

endmoudle

这儿补充一下。无论传递给run_test什么参数,创建的实例名都为uvm_test_top。

但此处函数中没有参数,因为UVM提供对不加参数的run_test的支持。

UVM会利用UVM_TEST_NAME从命令行中寻找测试用例的名字,

创建它的实例并运行。 如下所示的代码可以启动my_case0:

<sim command>

… +UVM_TEST_NAME=my_case02、uvm_root::run_test

这个run_test不是一个类的成员函数,是一个global task,内部调用uvm_root::run_test

//uvm_global

task run_test (string test_name="");

uvm_root top;

top = uvm_root::get();//创建了整个uvm_root,得到了uvm_topd顶层

top.run_test(test_name);//调用uvm_root::run_test

endtaskuvm_root::run_test中,根据UVM_TESTNAME创建uvm_test_top对象,并且调用静态方法m_run_phases,开启了uvm_phase的启动。

$cast(uvm_test_top, factory.create_component_by_name(test_name,"", "uvm_test_top",

null));

// phase runner, isolated from calling process

fork begin

// spawn the phase runner task

phase_runner_proc = process::self();

uvm_phase::m_run_phases();

end

join_none

#0; // let the phase runner start

wait (m_phase_all_done == 1);3、uvm_phase::m_run_phases

m_phase_hopper是一个uvm_phase类型的mailbox,在m_run_phasez中,先将common domain的第一个phase(build_phase)put进入mailbox中。然后进入forever,不停的去get_phase,get成功后就去执行phase。在execute_phase中,会遍历所有uvm component tree上的所有组件,将所有组件的phase执行完毕。执行完毕后,退出execute_phase,将下一个类型的phase put进入mailbox。

先get_common_domain(),构建好整个UVM树。将他们依次放入m_phase_hopper(信箱)中,通过execute_phase来运转所有组件的phase。全部执行完毕,将下一种phase放入信箱,再执行。

task uvm_phase::m_run_phases();

uvm_root top = uvm_root::get();

// initiate by starting first phase in common domain

begin

uvm_phase ph = uvm_domain::get_common_domain();

void'(m_phase_hopper.try_put(ph));

end

forever begin

uvm_phase phase;

m_phase_hopper.get(phase);

fork

begin

phase.execute_phase();

end

join_none

#0; // let the process start running

end

endtaskuvm启动过程及phase机制实现原理介绍 - 百度文库 https://wenku.baidu.com/view/3f585d75ae02de80d4d8d15abe23482fb4da0266.html从源码角度来看UVM phase - 简书

https://wenku.baidu.com/view/3f585d75ae02de80d4d8d15abe23482fb4da0266.html从源码角度来看UVM phase - 简书 https://www.jianshu.com/p/ac81d851992d

https://www.jianshu.com/p/ac81d851992d

本文详细解析了UVM验证平台的启动过程,从顶级模块run_test开始,通过uvm_root::run_test引导uvm_phase机制。讲解了如何创建uvm_test_top实例,执行build_phase,并深入剖析了phase的获取、执行和信箱机制。

本文详细解析了UVM验证平台的启动过程,从顶级模块run_test开始,通过uvm_root::run_test引导uvm_phase机制。讲解了如何创建uvm_test_top实例,执行build_phase,并深入剖析了phase的获取、执行和信箱机制。

986

986

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?