在进行 AXI DMA 配置 时候代码一直卡在XAxiDma_CfgInitialize函数出不来,也没有打印报错。

/* Initialize the XAxiDma device.

*/

CfgPtr = XAxiDma_LookupConfig(DeviceId);

if (!CfgPtr) {

xil_printf("No config found for %d\r\n", DeviceId);

return XST_FAILURE;

}

xil_printf("XAxiDma_Setup0\r\n");

Status = XAxiDma_CfgInitialize(&AxiDma, CfgPtr);

if (Status != XST_SUCCESS) {

xil_printf("Initialization failed %d\r\n", Status);

return XST_FAILURE;

}

xil_printf("XAxiDma_Setup2\r\n");

...

}

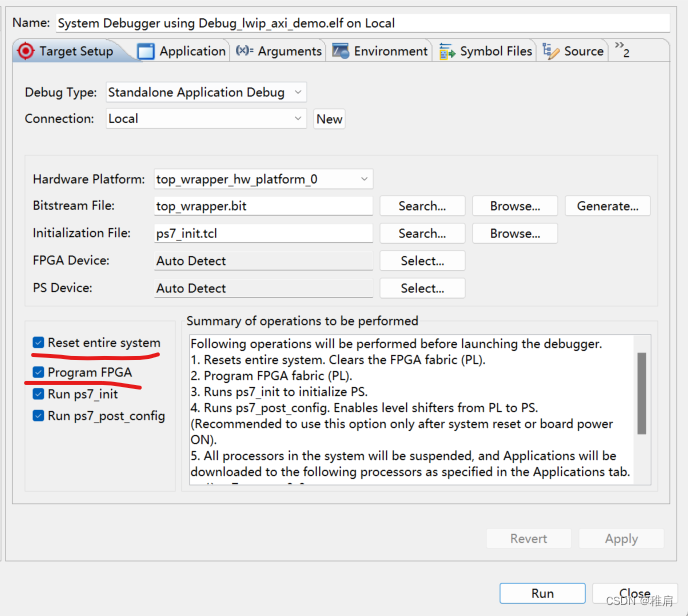

解决方法是,鼠标放在项目上右键打开Run as,打开Run Confiration查验下如下两项有没有勾选。

1862

1862

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?