在数字电路中,触发器是一种基本的时序逻辑单元,广泛应用于计数器、寄存器、存储器等复杂电路的设计中。它不仅能够存储二进制信息,还能通过输入信号的变化实现状态转换。本文将从触发器的基本概念、类型、工作原理及其实际应用等方面展开,帮助读者深入理解触发器的重要性。

目录

文章目录

1. 触发器的基本概念

触发器是一种具有记忆功能的数字电路单元,其输出状态不仅取决于当前输入信号,还与之前的状态有关。触发器通常有两个输出端:主输出(Q)和反相输出( Q ‾ \overline{Q} Q)。例如,在RS触发器中,当输入S=1、R=0时,输出Q被置为1;当输入S=0、R=1时,输出Q被置为0;当输入S=R=1时,输出Q保持不变;当输入S=R=0时,输出Q处于不确定状态。

2. 触发器的分类

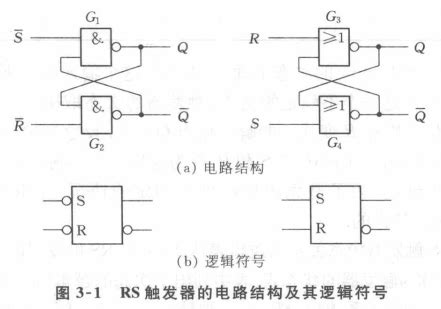

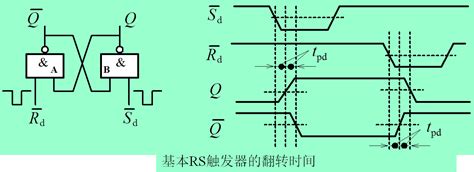

2.1 基本RS触发器

基本RS触发器由两个非门组成,其逻辑功能可以通过真值表来描述。这种触发器在数字电路中非常基础,但容易出现“不定状态”问题,即当输入S=R=1时,输出状态无法确定。

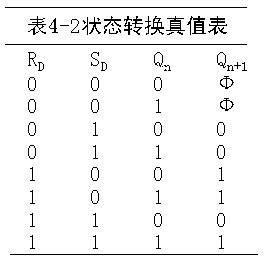

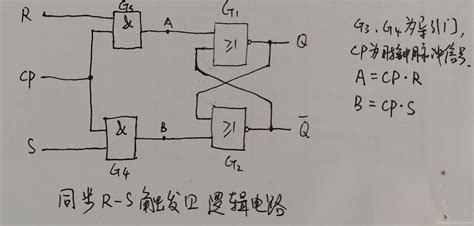

2.2 同步触发器

同步触发器通过增加时钟信号来控制状态转换,从而避免了不定状态的问题。例如,同步RS触发器在时钟脉冲的上升沿或下降沿根据输入信号更新输出状态。

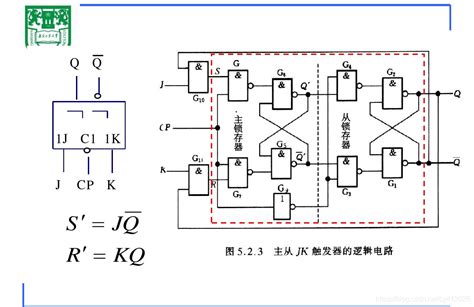

2.3 主从触发器

主从触发器由两个同步RS触发器组成,一个作为主触发器,另一个作为从触发器。主触发器在时钟信号的上升沿更新状态,而从触发器在下降沿更新状态。这种设计可以进一步提高电路的稳定性。

2.4 边沿触发器

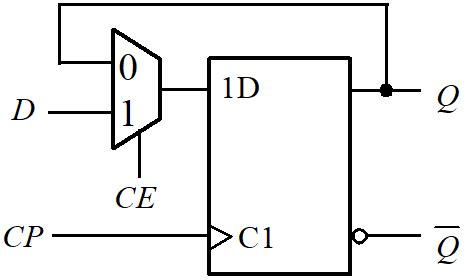

边沿触发器仅在时钟信号的上升沿或下降沿进行状态更新,避免了同时输入多个信号导致的冲突问题。例如,D触发器和JK触发器都属于边沿触发器。

3. 触发器的工作原理

3.1 RS触发器的工作机制

RS触发器通过两个非门实现记忆功能。当输入S=1、R=0时,输出Q被置为1;当输入S=0、R=1时,输出Q被置为0;当输入S=R=1时,输出Q保持不变;当输入S=R=0时,输出Q处于不确定状态。

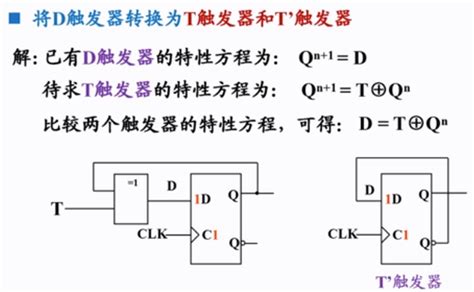

3.2 D触发器与T触发器的区别

D触发器是一种边沿触发器,其输出仅在时钟信号的上升沿或下降沿根据输入D更新。而T触发器则是在每个时钟周期内根据输入T翻转输出状态。

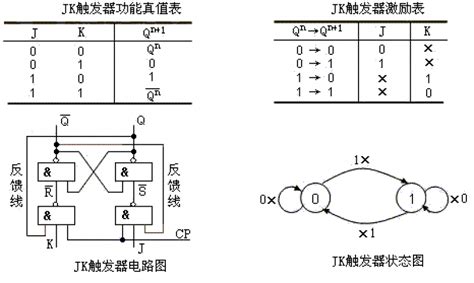

3.3 JK触发器的特点

JK触发器是一种具有主从结构的边沿触发器,其输出在时钟信号的上升沿根据输入J和K更新。当J=K=1时,输出Q会在每个时钟周期内翻转。

4. 触发器的实际应用

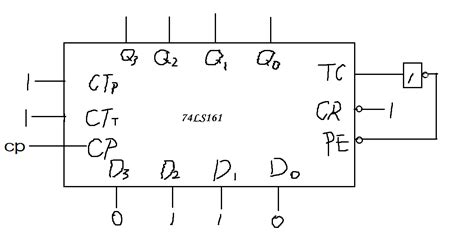

4.1 计数器设计

计数器是数字电路中最常见的应用之一,通过多个触发器级联实现不同进制的计数功能。例如,一个四位二进制计数器可以通过四个D触发器实现,每个触发器的输出作为下一个触发器的输入。

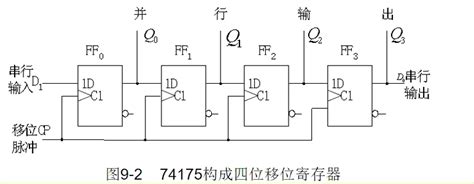

4.2 寄存器与存储器

寄存器用于存储数据,而存储器则用于存储程序或数据。例如,一个四位寄存器可以通过四个D触发器实现,每个触发器的输入由数据总线提供。

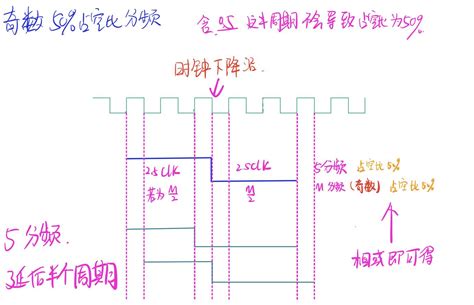

4.3 触发器在时钟信号生成中的作用

在数字系统中,触发器常用于生成稳定的时钟信号。例如,通过分频电路设计可以利用D触发器将高频信号转换为低频信号。

5. 触发器的优缺点分析

优点

- 记忆功能:触发器能够存储二进制信息。

- 灵活性:通过不同的组合方式可以实现多种逻辑功能。

- 稳定性:通过主从结构或边沿触发可以提高电路的稳定性。

缺点

- 不定状态:基本RS触发器在某些输入条件下可能出现不定状态。

- 复杂性:高级触发器(如JK触发器)的设计和分析较为复杂。

6. 总结与展望

触发器作为数字电路中的核心组件,其基本原理和应用范围广泛。从简单的RS触发器到复杂的JK触发器,每种类型的触发器都有其独特的应用场景。未来,随着集成电路技术的发展,触发器的设计将更加高效和可靠,为数字电路的发展提供更强大的支持。

关注不迷路,点赞走好运!!!

1106

1106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?