目录

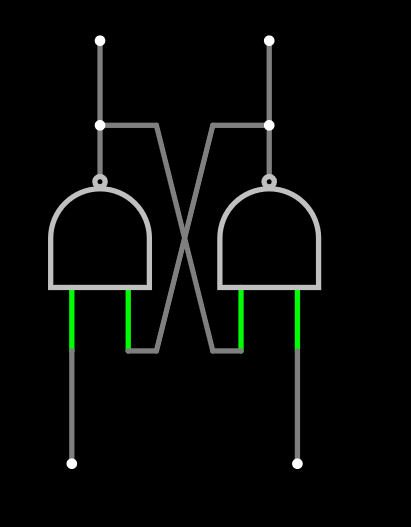

一、基本RS触发器

1.电路结构

或非门或与非门加入馈线组成

2.特性表

| R | S | ||

|---|---|---|---|

| 0 | 0 | 未定 | 未定 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 保持 | 保持 |

3.特性方程

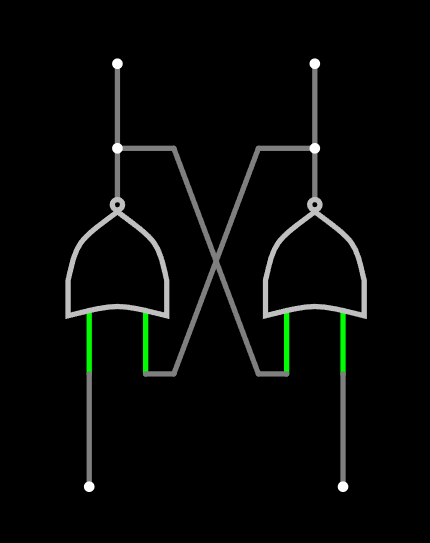

4.典型波形图示意

5.特性分析

基本RS触发器的动作特点是:在输入信号R,S的全部作用时间内,都能直接改变输出信号Q的状态。

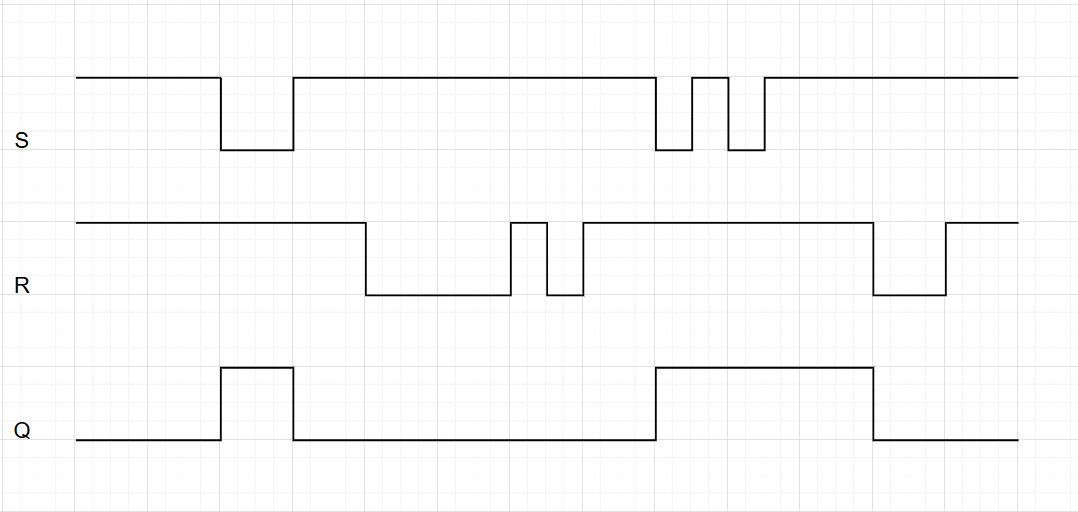

二、同步触发器(电平触发器)

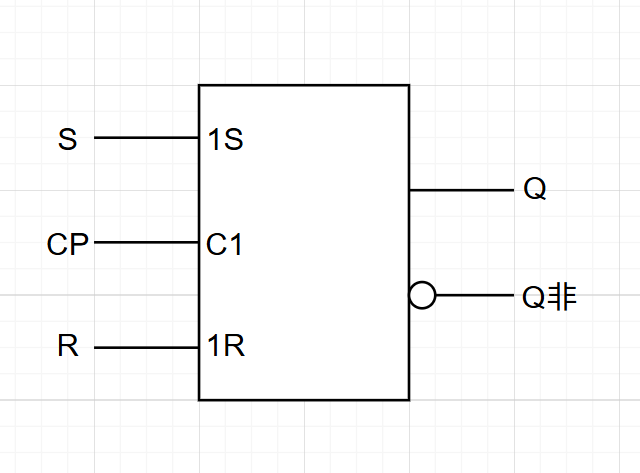

1.同步RS触发器

1.电路结构

2. 特性表

| S | R | 输出端 | S' | R' | 功能说明 |

| 0 | 0 | 1 | 1 | 保持 | |

| 1 | 0 | 0 | 1 | 置"1" | |

| 0 | 1 | 1 | 0 | 置"0" | |

| 1 | 1 | 不定 | 0 | 0 | 不定 |

3.特性方程

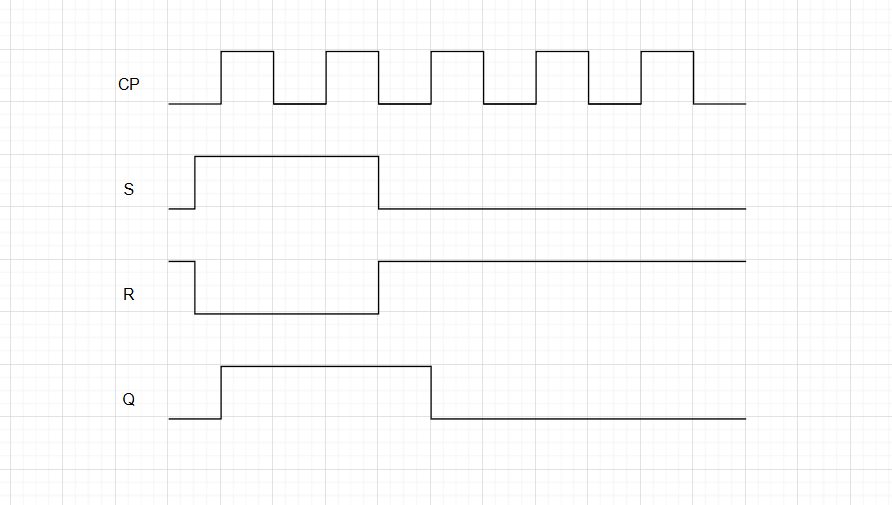

4.典型波形图示意

5.特性分析

动作特点:只有在时钟信号(CP,Clock Pulse)为有效电平(通常为高电平或低电平,取决于设计)时,输入信号(R、S)才能影响输出状态;无效电平时,触发器保持原状态不变。这种触发方式也称为电平触发

在CP有效期间,输入信号(R、S)的变化会直接反映到输出端(Q和Q‾Q),即存在"透明性"。若R、S信号在CP有效期间发生多次变化,输出可能随之多次翻转,导致抗干扰能力较差。

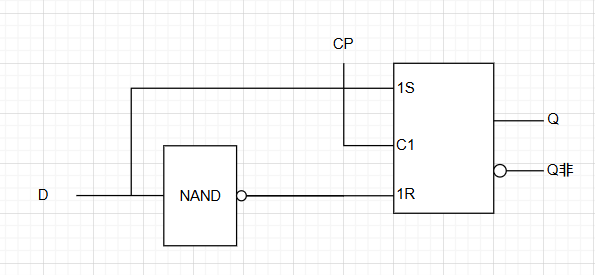

2.同步D触发器

1.电路结构

2.特性表

| CP | D | 功能 | |

|---|---|---|---|

| 1 | 0 | 0 | 置"0" |

| 1 | 1 | 1 | 置"1" |

| 0 | 保持 |

3.特性方程

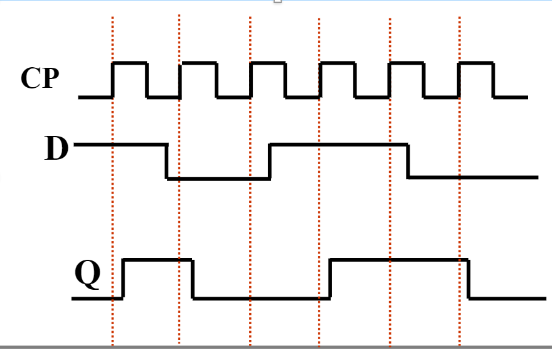

4.典型波形图

5.特性分析

CLK有效期间输入干扰会直接影响输出(抗噪能力弱)。

不适合高速场景(因透明性可能导致级联触发器竞争,与RS触发器一样无法克服空翻)

三、主从触发器(脉冲触发器)

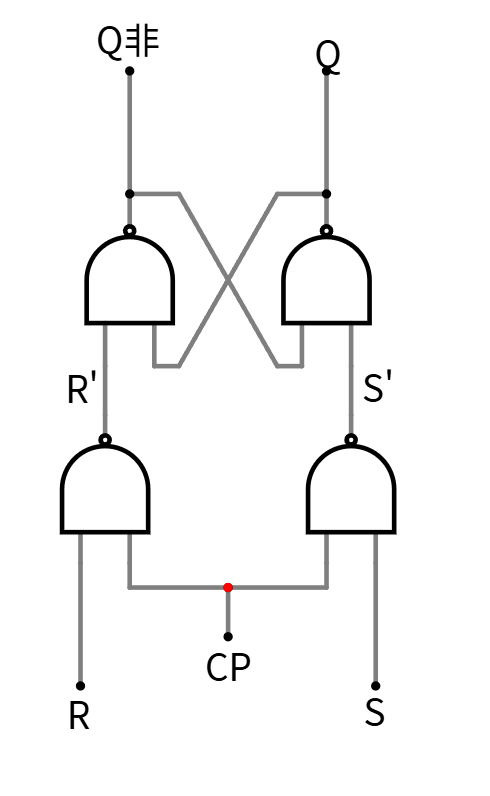

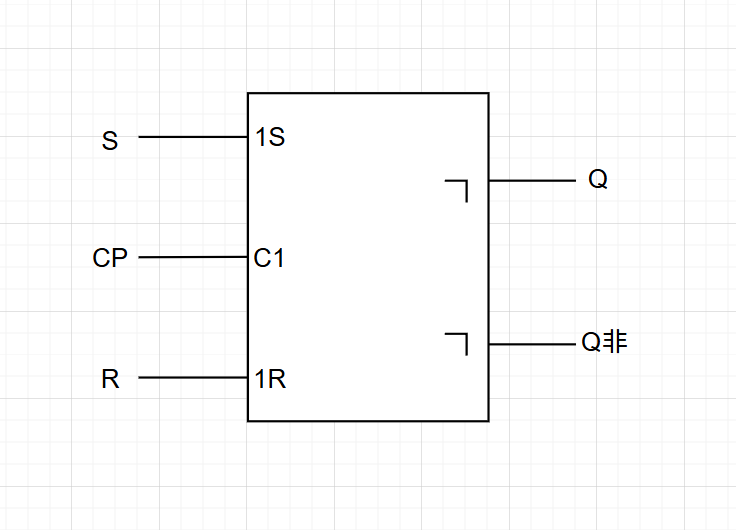

1.主从RS触发器

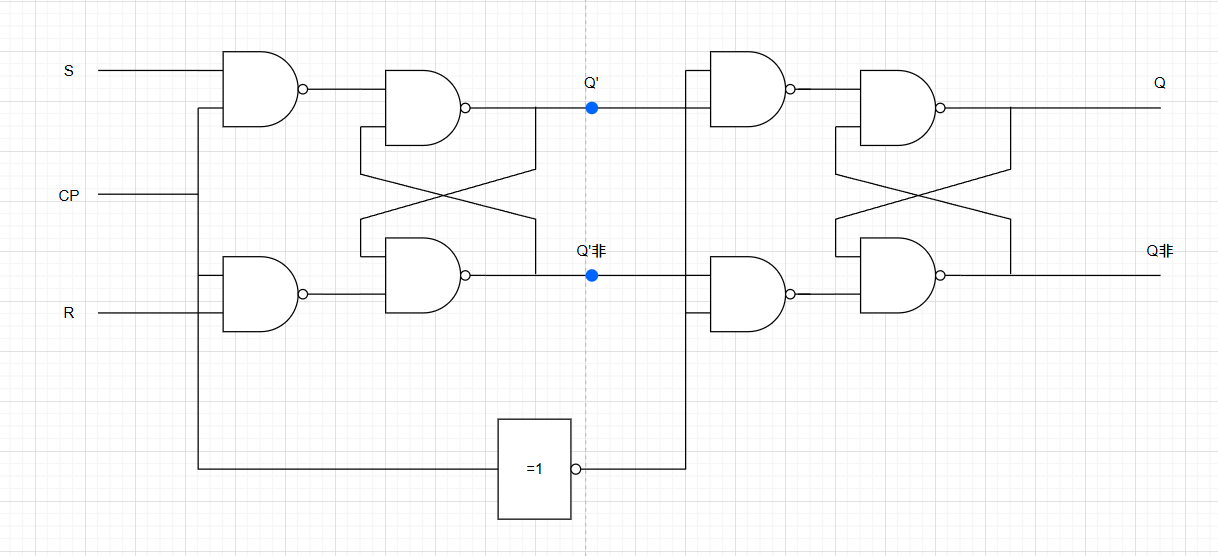

1.电路结构

2. 特性表

| CP | S | R | |

|---|---|---|---|

| 0 | 0 | ||

| 1 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 1 | 不定 |

注:该表仅适用于CP=1期间RS信号不变

3.特性方程

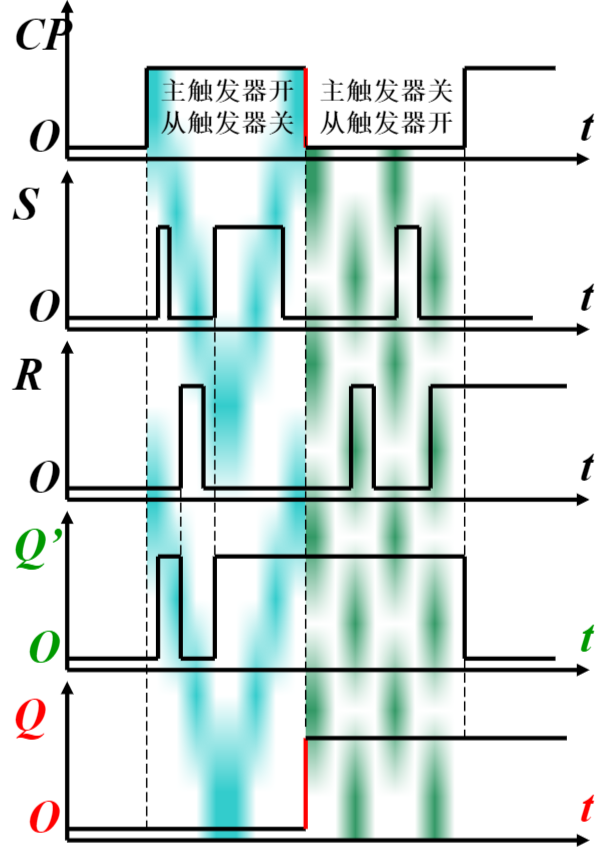

4.典型波形图

在CP=1期间RS发生变化,要先分析Q'点的状态在推出Q点状态。

5.特性分析

将多次空翻转换为一次空翻,较为有效的克服了干扰,但是未完全消除干扰现象。

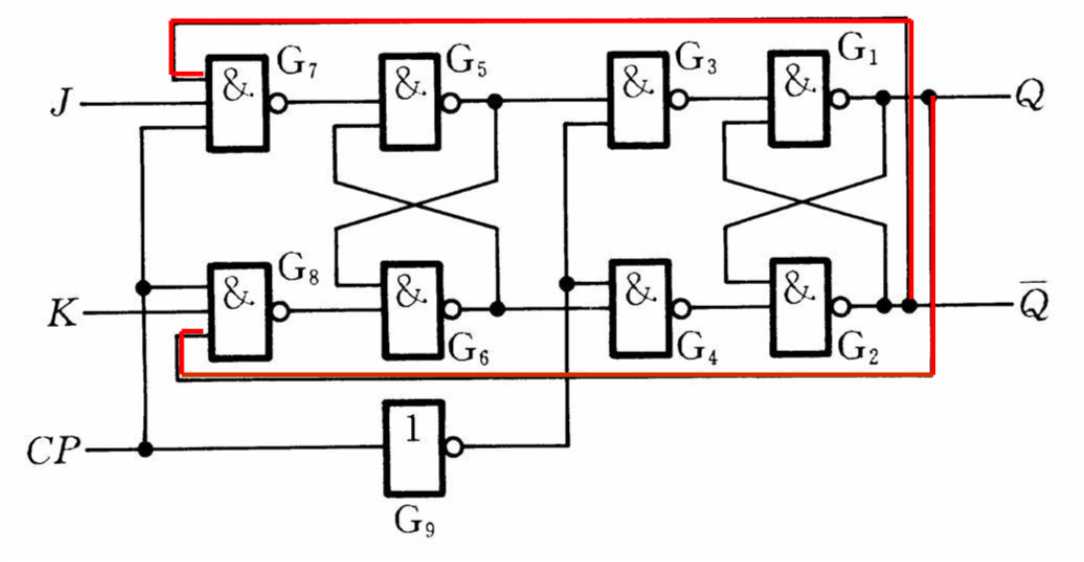

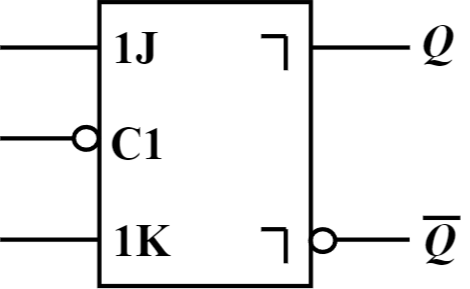

2.主从JK触发器

1.电路结构

2.特性表

| CP | J | K | |

|---|---|---|---|

| 0 | 0 | ||

| 0 | 1 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 翻转 |

3.状态方程

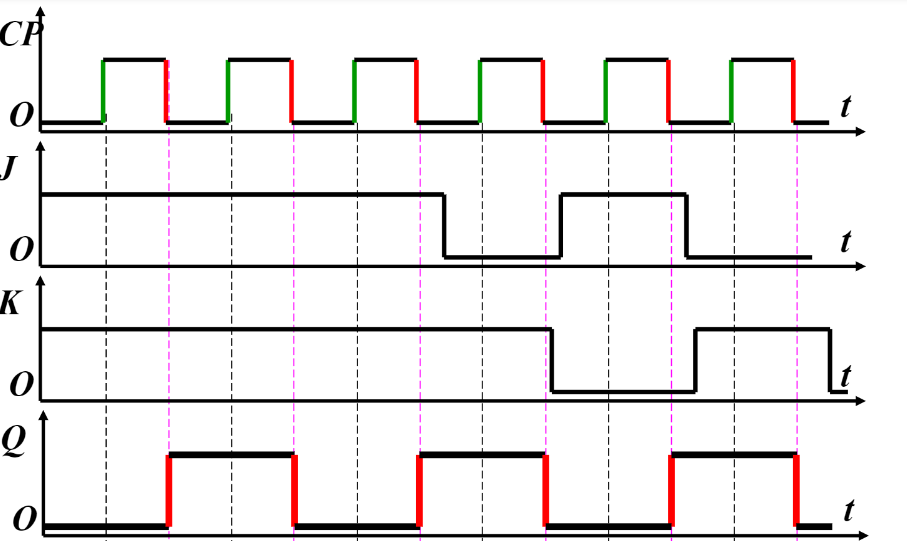

4.典型波形图

5.特性分析

1. 功能特性

-

无禁态问题:与RS触发器不同,J=K=1时触发器翻转,无输入约束。

-

抗干扰能力:输出仅在CLK下降沿更新,减少电平触发器的透明性风险。

-

一次变化现象:CLK=1期间,主触发器可能因J、K变化多次翻转,但最终仅下降沿时的状态被传递(需保证CLK=1期间J、K稳定)。

2. 时序特性

-

建立时间(tsutsu):J、K信号需在CLK下降沿前(CLK=1期间)保持稳定。

-

保持时间(thth):CLK下降沿后J、K需保持短暂稳定。

-

传输延迟:输出Q的变化相对于CLK下降沿存在延迟(tpdtpd)。

3. 优缺点

-

优点:

-

功能完备(支持保持、置位、复位、翻转)。

-

通过主从结构抑制空翻,适用于中低速时序电路。

-

-

缺点:

-

一次变化问题:CLK=1期间若J、K变化,可能导致主触发器误动作(需严格限制输入变化时间)。

-

速度受限:主从两级结构引入额外延迟,不如边沿触发器高速。

-

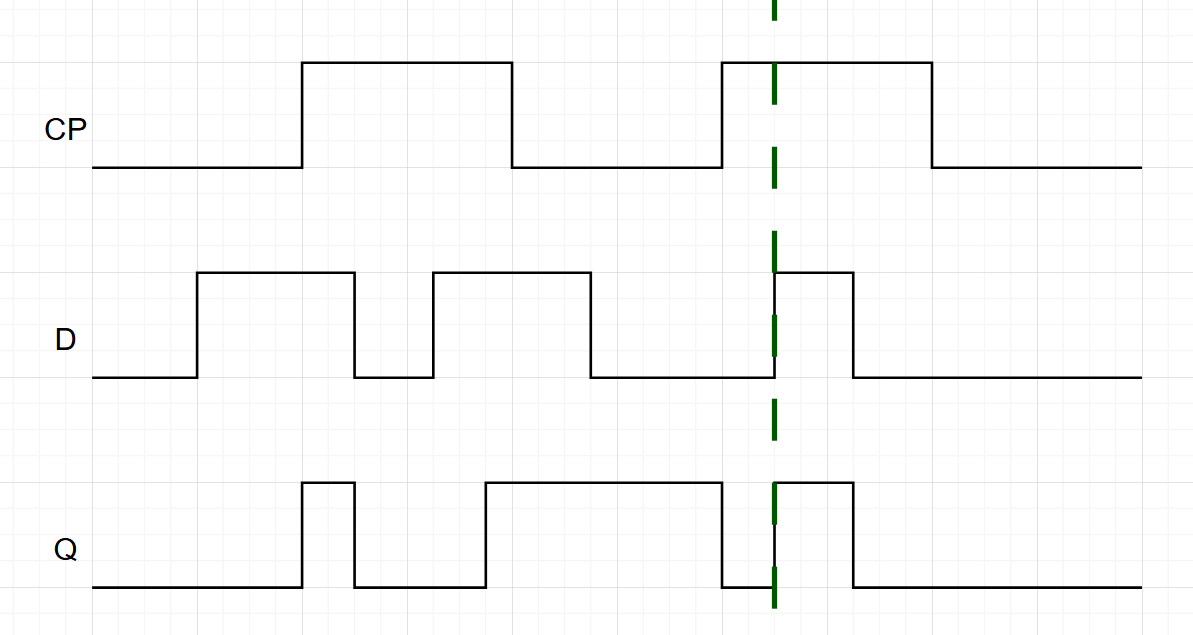

四、边沿触发器

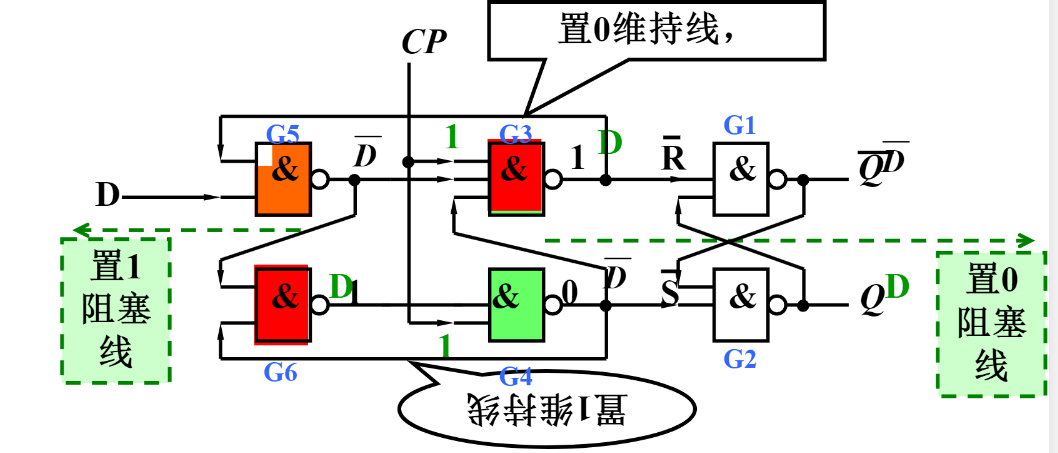

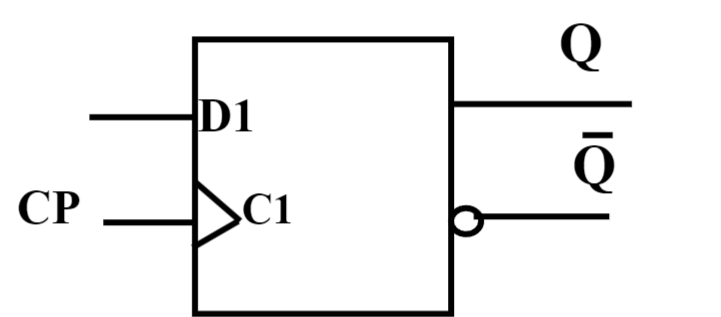

D边沿触发器

1.电路结构

2.特性表

| CP | D | ||

|---|---|---|---|

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 1 |

3.特性方程

4.典型波形图

5、特性分析

优点:

1.抗干扰能力极强(仅边沿瞬间采样)。

2.适合高速电路(无透明性,可级联)。

3.无禁态问题(D触发器仅单输入,简化控制逻辑)。

缺点:

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?