粗略阅读了本书的前4章节,简要做一些基础性的小结。

涉及ARM相关的几个章节,后续阅读的时候再做小结吧。

若希望详细了解相关内容,请阅读原著精彩内容!

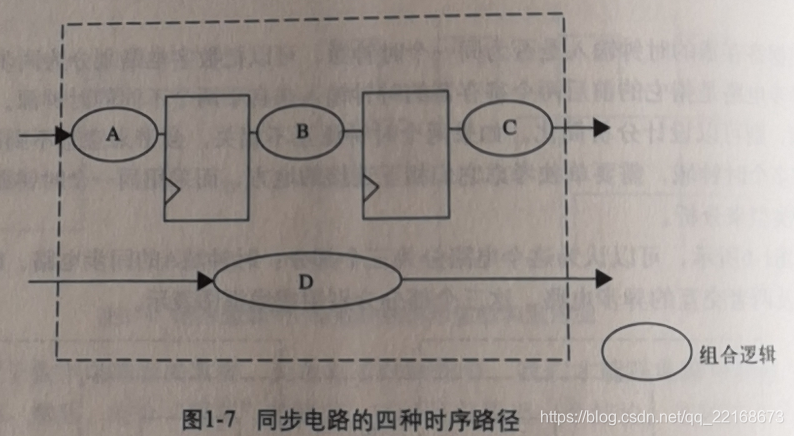

概念一:同步电路时序路径

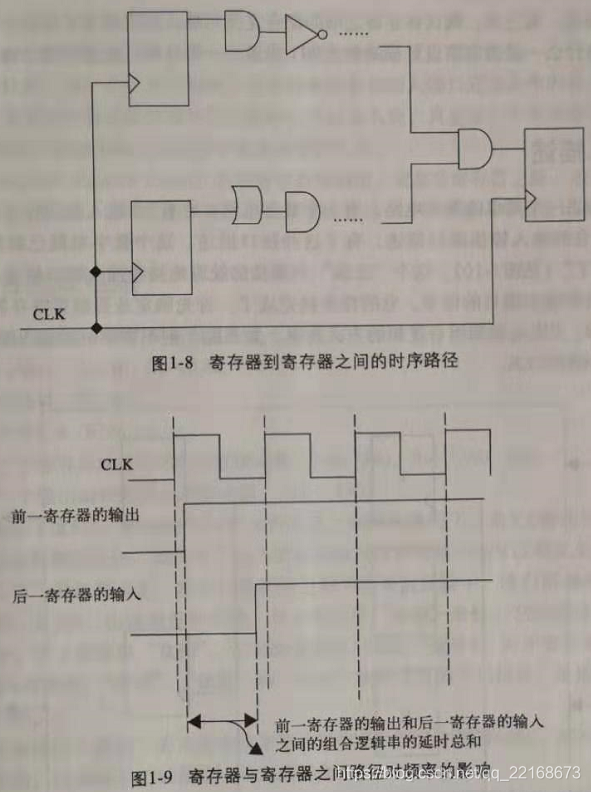

一般来说,寄存器到寄存器之间的组合逻辑消耗的时间决定了时钟的频率。

设计者必须对寄存器和寄存器之间的组合逻辑串保持敏感。通常是最长的组合逻辑串决定了时钟的频率。如果想要提高时钟频率,必须减少这个组合逻辑串的总延时。

概念二:

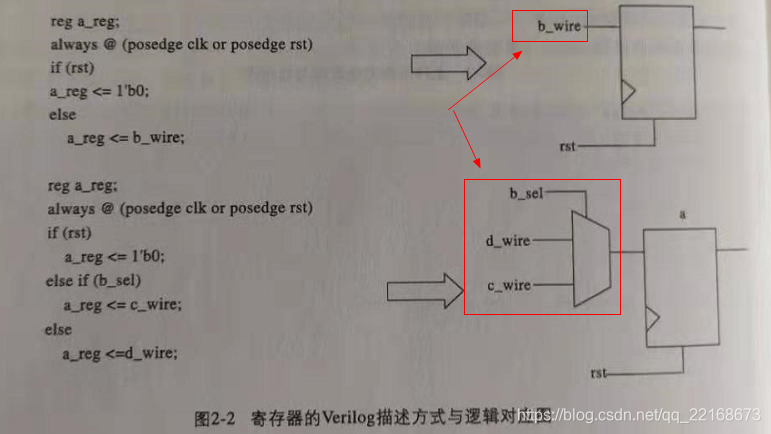

在使用always描述一个时序逻辑寄存器的时候,实践上是包含一部分组合逻辑。

如下图所示,在对一个寄存器进行有选择的赋值时,该寄存器的数据输入端就包含一个组合逻辑的选择器。

本文概述了ARM架构中同步电路时序路径的概念,强调了寄存器间组合逻辑延时对时钟频率的影响。指出设计者需关注最长组合逻辑路径以优化时钟频率,并解释了在使用always描述时序逻辑时隐含的组合逻辑。

本文概述了ARM架构中同步电路时序路径的概念,强调了寄存器间组合逻辑延时对时钟频率的影响。指出设计者需关注最长组合逻辑路径以优化时钟频率,并解释了在使用always描述时序逻辑时隐含的组合逻辑。

1985

1985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?