1、从Quartus启动ModelsimSE

Quartus软件设置步骤如下:

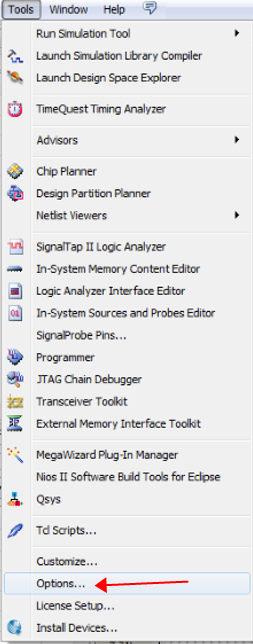

步骤1:Tools--Options--General--EDA Tool Options:指定modelsim.exe所在的文件路径。

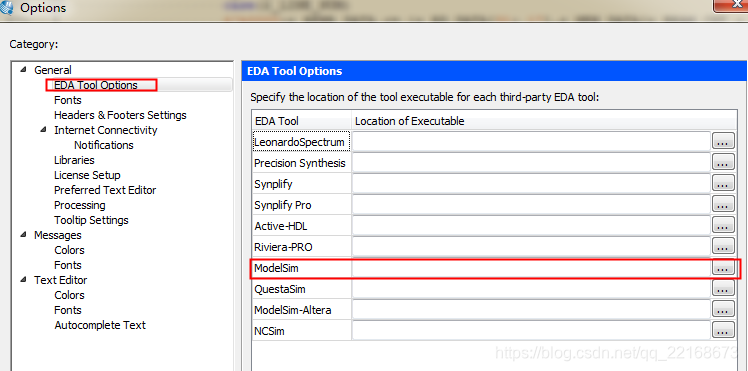

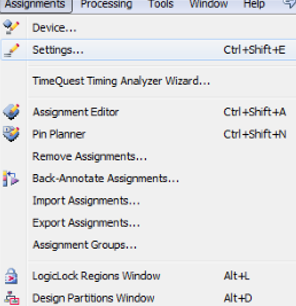

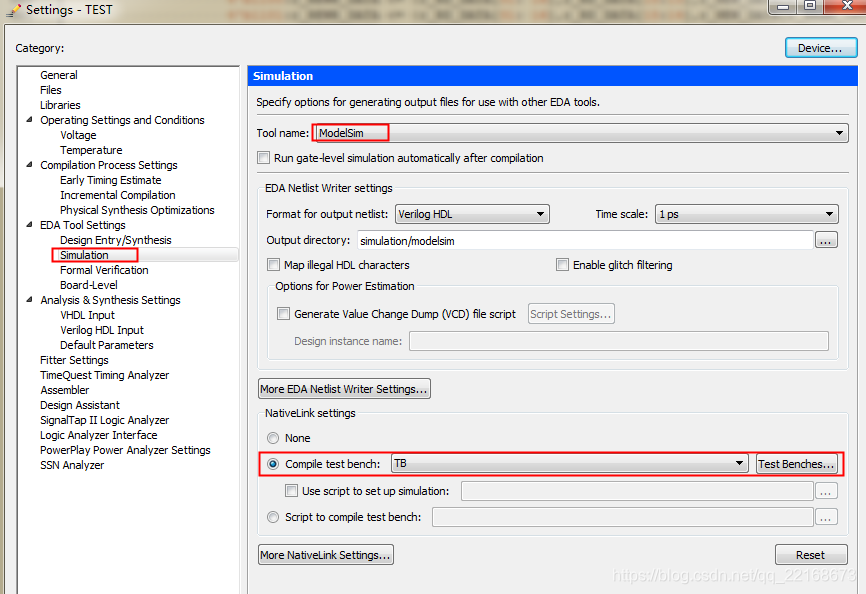

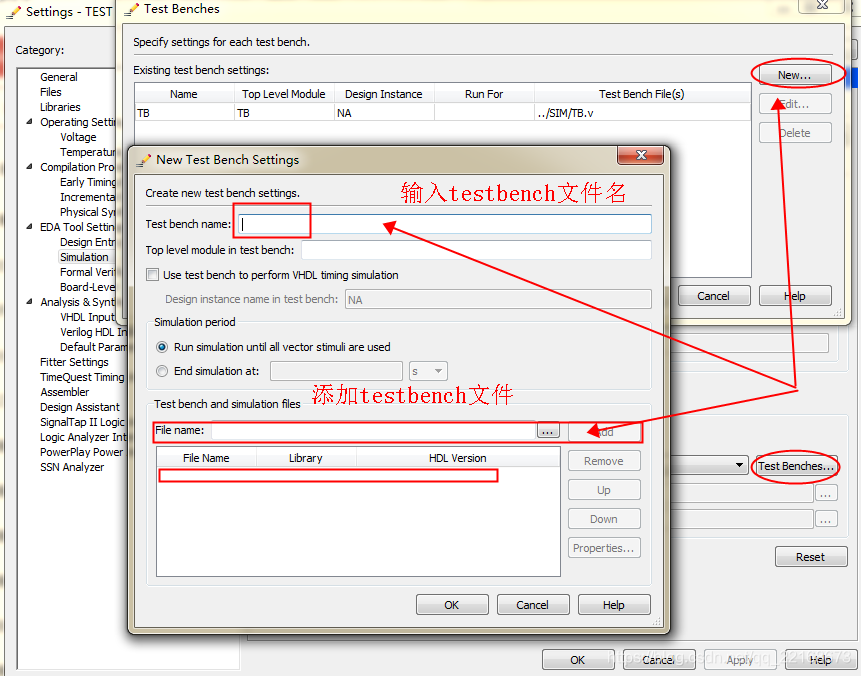

步骤2:Assignment--Settings--EDA Tool Settings--Simulation:指定仿真工具是modelsim、添加testbench文件

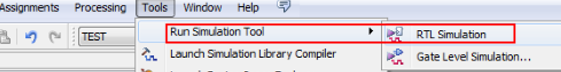

步骤3:启动仿真。Tools--Run Simulation tool--RTL Simulation。

2、单独ModelsimSE对Alter IP进行仿真

2.1编译Quatus仿真库

首先,去掉将modelsim\win64文件路径下modelsim.ini文件的只读属性。然后,执行下面步骤:

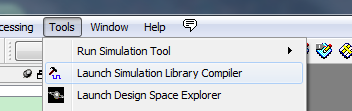

(1)打开quartus软件。选择Tools--Launch Simulation Library Compiler。

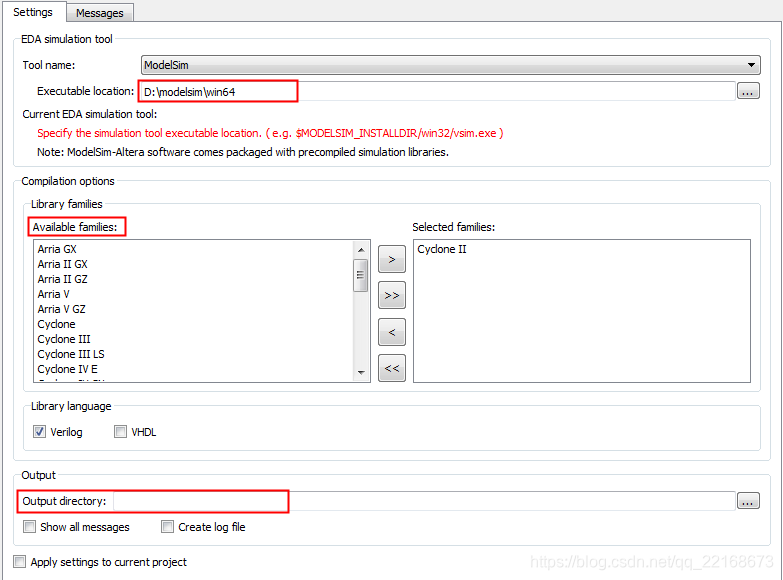

(2)设置仿真工具及其文件路径;选择需要的器件/语言;设置仿真库输出路径;开始编译。

(3)将modelsim\win64文件路径里的modelsim.ini文件,添加quartus仿真库文件路径。

举例:下图是在modelsim文件路径里的modelsim.ini文件中,添加Xilinx的仿真库(前提是你已经编译好Xilinx的仿真库)

secureip = D:\ISE\14.4\ISE_DS\ISE\verilog\mti_se\10.4\nt64/secureip

unisims_ver = D:\ISE\14.4\ISE_DS\ISE\verilog\mti_se\10.4\nt64/unisims_ver

unimacro_ver = D:\ISE\14.4\ISE_DS\ISE\verilog\mti_se\10.4\nt64/unimacro_ver

simprims_ver = D:\ISE\14.4\ISE_DS\ISE\verilog\mti_se\10.4\nt64/simprims_ver

xilinxcorelib_ver = D:\ISE\14.4\ISE_DS\ISE\verilog\mti_se\10.4\nt64/xilinxcorelib_ver

uni9000_ver = D:\ISE\14.4\ISE_DS\ISE\verilog\mti_se\10.4\nt64/uni9000_ver

unisim = D:\ISE\14.4\ISE_DS\ISE\vhdl\mti_se\10.4\nt64/unisim

unimacro = D:\ISE\14.4\ISE_DS\ISE\vhdl\mti_se\10.4\nt64/unimacro

simprim = D:\ISE\14.4\ISE_DS\ISE\vhdl\mti_se\10.4\nt64/simprim

xilinxcorelib = D:\ISE\14.4\ISE_DS\ISE\vhdl\mti_se\10.4\nt64/xilinxcorelib

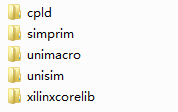

上面路径,对应的仿真库文件夹如下图所示。文件夹路径:...\...\nt64:

然后,在modelsim文件路径里的modelsim.ini文件中,添加Quartus的仿真库,如所示。

altera_lnsim_ver = D:\modelsim\Alter_lib\verilog_libs/altera_lnsim_ver

altera_mf_ver = D:\modelsim\Alter_lib\verilog_libs/altera_mf_ver

altera_ver = D:\modelsim\Alter_lib\verilog_libs/altera_ver

cycloneii_ver = D:\modelsim\Alter_lib\verilog_libs/cycloneii_ver

lpm_ver = D:\modelsim\Alter_lib\verilog_libs/lpm_ver

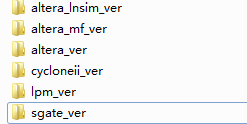

sgate_ver = D:\modelsim\Alter_lib\verilog_libs/sgate_ver 上面路径,对应Quartus仿真库文件夹如下图所示。

2.2 run_wave.do文件

此处与Xilinx仿真一致,可参考文章 : modelsim do文件简介

#================================================================

# Clear

#================================================================

# 退出当前仿真

quit -sim

# 清输出窗口

.main clear

#================================================================

# Create work library

#================================================================

# It will create a "work" folder in current folder

# 创建本地库

vlib work

# 将逻辑库名映射库路径

vmap work work

#================================================================

# Compile IPcore

#================================================================

# Add File path and Compile them

#vlog ../../xilinx_ip/*.V

#vlog ./*.V

#================================================================

# Compile RTL

#================================================================

# 编译当前目录下的所有v文件

vlog ./*.v

# 编译上一级目录下的所有v文件

#vlog ../*.V

#================================================================

# Start the emulator(启动仿真器)

#================================================================

#方式一:添加Xilinx仿真库

vsim -L xilinxcorelib -L simprim -L unimacro -L unisim -voptargs=+acc work.TB

#方式二:添加Xilinx仿真库

#vsim -novopt -t 1ps -c -L simprim -L unimacro -L unisim -l ./log/report.log -wav ./wave/tb.wlf -voptargs=+acc work.tb_top

#方式三:添加quartus仿真库

#vsim -novopt -t 1ps -c -L altera_lnsim_ver -L altera_mf_ver -L altera_ver -L cycloneii_ver -L lpm_ver -L sgate_ver -l ./log/report.log -wav ./wave/tb.wlf -voptargs=+acc work.tb_top

#================================================================

# Set the window types

#================================================================

view wave

view structure

view signals

#================================================================

# Add watch wave

#================================================================

add wave -noupdate -color green -format Logic -radix hexadecimal -group {TB} /TB/*

add wave -noupdate -color cyan -format Logic -radix binary -group {WAV} {sim:/tb/UUT[0]/NET/*}

#================================================================

# run

#================================================================

.main clear

run 10us

本文详细介绍如何使用Quartus和Modelsim进行FPGA设计的仿真,包括从Quartus启动ModelsimSE的步骤,以及如何在ModelsimSE中单独对Altera IP进行仿真。涵盖设置仿真工具路径、编译Quartus仿真库、添加仿真库文件路径、编写run_wave.do文件等内容。

本文详细介绍如何使用Quartus和Modelsim进行FPGA设计的仿真,包括从Quartus启动ModelsimSE的步骤,以及如何在ModelsimSE中单独对Altera IP进行仿真。涵盖设置仿真工具路径、编译Quartus仿真库、添加仿真库文件路径、编写run_wave.do文件等内容。

3606

3606

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?