1.安装准备

Synopsys VIP一般为.run文件形式,以AMBA VIP为例,VIP文件为vip_amba_svt_R-2020.12.run

VCS版本T-2022.06,有建议说VIP版本不能晚于VCS版本

2.安装步骤

(1) 新建路径/usr/Synopsys/vip_2020_12

(2) 在~/.bashrc文件中添加行,修改环境变量DESIGNWARE_HOME为步骤(1)新建路径

export DESIGNWARE_HOME=/usr/Synopsys/vip_2020_12(3) 安装VIP,运行./vip_amba_svt_R-2020.12.run,文件运行位置任意,指定好$DESIGNWARE_HOME即可

等待运行完成,在$DESIGNWARE_HOME/vip/svt/amba_svt/latest/doc路径下可以找到说明文档。

(4)生成VIP和VIP示例

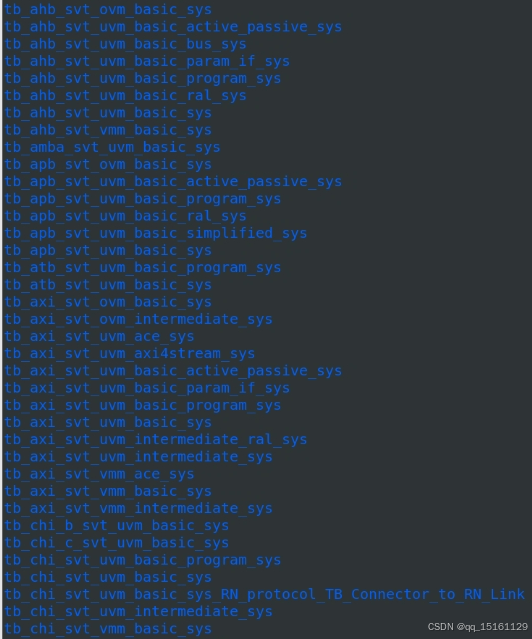

在$DESIGNWARE_HOME /vip/svt/amba_svt/latest/examples/sverilog路径下可以查看所有示例,可以看到有AXI、AHB、APB。Synopsys把ACE、AXI-Stream都包含在了AXI VIP里包括接口定义。

选择生成AXI示例,在终端输入

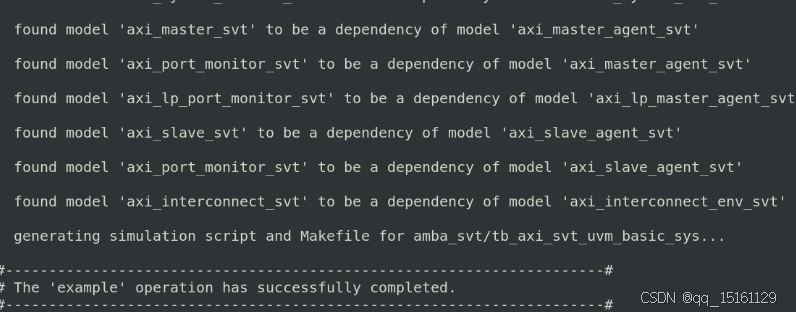

$DESIGNWARE_HOME/bin/dw_vip_setup -path ./ -e amba_svt/tb_axi_svt_uvm_basic_sys -svtb等待生成完成

其中./为生成文件路径,生成后包含5个文件夹,其中example为生成的示例,其他为生成的VIP,对于同一验证环境需要多个VIP,需要用dw_vip_setup –add的方式生成到同一目录下。

3.运行示例

进入示例目录

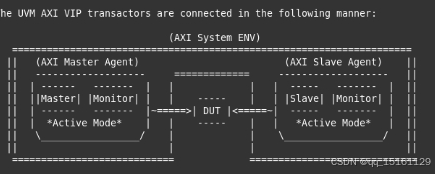

cd ./examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys可以在README中看到验证环境示意,验证环境包含1个master个1个slave,DUT查看代码为输出输入直连。

在终端执行Makefile命令,由于需要使用Verdi查看,所以修改WAVES为fsdb来dump Verdi波形,如果用DVE查看WAVES=1即可。在./tests目录可以看到一些case文件,这里选择directed_test

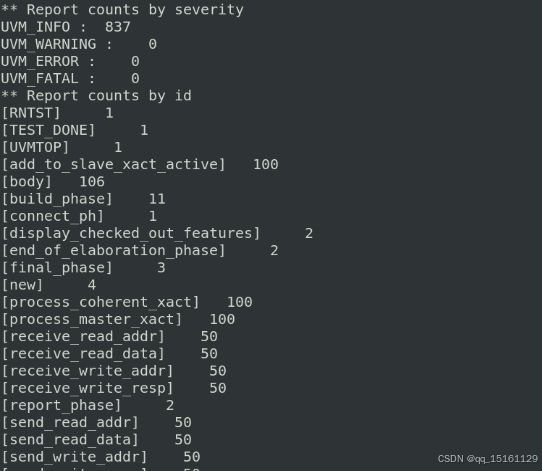

gmake USE_SIMULATOR=vcsvlog directed_test WAVES='fsdb'仿真完成,可以看到完成50包传输

如果是DVE可以直接使用目录下waves.tcl脚本。使用Verdi需要自己写指令,指令参照编译log中的文件列表

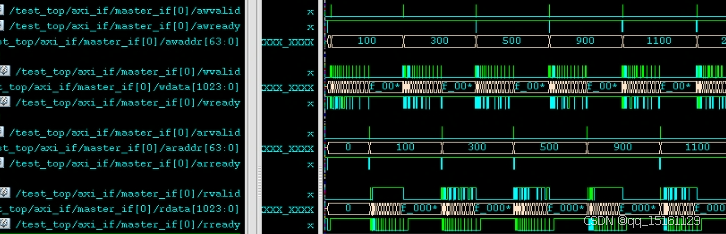

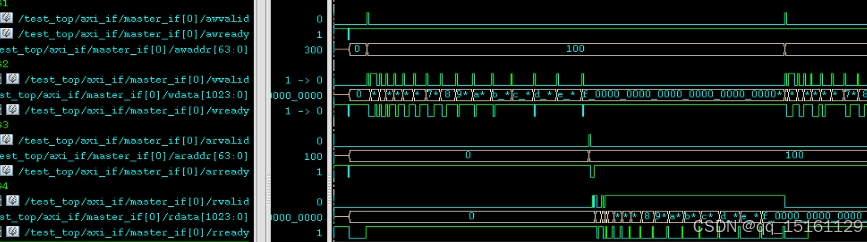

verdi -sverilog -ntb_opts uvm +incdir+../../../../src/sverilog/vcs +incdir+../../../../include/sverilog +incdir+../../../../src/verilog/vcs +incdir+../../../../include/verilog +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/../../env +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/../env +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/env +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/dut +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/hdl_interconnect +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/lib +incdir+../../../../examples/sverilog/amba_svt/tb_axi_svt_uvm_basic_sys/tests -f top_files -f hdl_files -ssf *.fsdb &可以看到,master不断发送地址bit增加的AXI写burst,数据为bit递增数,由于DUT直通,master读到的数据实际由slave返回,同样为递增数。

也可以在./env/axi_master_directed_sequence.sv查看地址、数据bit递增行为。

for(int i = 0; i < sequence_length; i++) begin

/** Set up the write transaction */

`uvm_create(write_tran)

write_tran.port_cfg = cfg;

write_tran.xact_type = svt_axi_transaction::WRITE;

write_tran.addr = 32'h0000_0100 | ('h100 << i);

write_tran.burst_type = svt_axi_transaction::INCR;

write_tran.burst_size = svt_axi_transaction::BURST_SIZE_32BIT;

write_tran.atomic_type = svt_axi_transaction::NORMAL;

write_tran.burst_length = 16;

write_tran.data = new[write_tran.burst_length];

write_tran.wstrb = new[write_tran.burst_length];

write_tran.data_user = new[write_tran.burst_length];

foreach (write_tran.data[i]) begin

write_tran.data[i] = i;

end

foreach(write_tran.wstrb[i]) begin

write_tran.wstrb[i] = 4'hf;

end

5836

5836

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?