https://github.com/zsylov/verliog-study/edit/master/2019.4.29%E8%BE%B9%E6%B2%BF%E6%A3%80%E6%B5%8B.md

1.复习verilog语法

====

* reg和wire的区别。

----

1.reg对应于过程赋值,如always,initial.

2.wire对应于连续赋值,如assign。其综合出来一般是一根导线。

* 阻塞与非阻塞的区别。

-----

1.阻塞赋值采用(=,组合逻辑电路)指在同一个always块中,其后面的赋值语句从概念上是在前一条赋值语句结束后开始赋值的。

非阻塞赋值采用(<=,时序逻辑电路),首先计算语句块内部所有右边表达式(RHS)的值,然后完成对左边寄存器变量的赋值操作。

* parameter与define的区别。

-----

1.语法不同,使用define定义的参数调用要加.

2.二者的作用域也不同,parameter 作用于声明的那个文件;define从编译器读到这条指令开始到编译结束都有效,或者遇到`undef命令使之失效。

*task与function的区别。

-----

function的定义:

function<返回值类型和位宽> <函数名>

<入口参量和类型声明>

<局部变量声明>

行为语句;

endfunction

task的定义

task<任务名>;

端口与类型说明;

变量声明;

语句1;

。。。

语句n;

endtask

task和function的不同点:

(1): function只能与主模块共用一个仿真时间单位,而task可以定义自己的仿真时间单位;

(2): function不能调用任务,而task可以调用函数;

(3): function至少需要一个输入变量,而task可以没有或者有很多个任意类型的变量;

(4): function返回一个值,而task则不返回值。

https://blog.youkuaiyun.com/duhanting/article/details/10326405

2.用verilog实现边沿检测电路:上升沿,下降沿,双沿(上升或下降沿)。

====

* 上升沿下降沿检测

```verilog

// Code your design here

`timescale 1ns/1ps

module edge_dect(

input Sys_clk,

input Sys_reset,

input data_in,

output L2H,

output H2L,

output both

);

reg data_in_r0;

reg data_in_r1;

always @ (posedge Sys_clk ,negedge Sys_reset )

if(!Sys_reset)

begin

data_in_r0<= 1'b0;

data_in_r1<= 1'b0;

end

else

begin

data_in_r0 <= data_in;

data_in_r1 <= data_in_r0;

end

assign L2H =~data_in_r1 & data_in_r0;

assign H2L =data_in_r1 & ~data_in_r0;

assign both = data_in_r1 ^ data_in_r0;

endmodule

```

testbench

```verilog

// Code your testbench here

// or browse Examples

`timescale 1ns/1ps

module test_edge();

reg Sys_clk;

reg Sys_reset;

reg data_in;

wire L2H,H2L,both;

initial

begin

$dumpfile("test_edge.vcd");

$dumpvars(1);

Sys_clk =0;

Sys_reset =0;

data_in = 0;

#100

Sys_reset =1;

#20

data_in = 0;

#20

data_in =1;

#60

data_in =0;

end

always #10 Sys_clk = ~Sys_clk;

edge_dect edge_tect_inst(

Sys_clk,

Sys_reset,

data_in,

L2H,

H2L,

both

);

endmodule

```

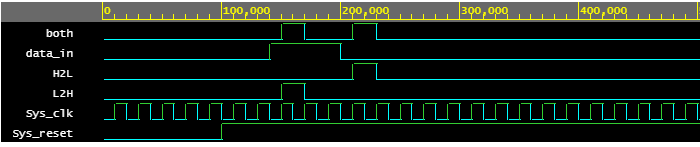

* 仿真结果

如图

3.记录一下第2题中用到的工具,包括工具版本,操作步骤或命令选项,遇到的错误,提示信息等。

====

* 仿真工具采用www.edaplayground.com,由于之前也是采用这个工具,现在再使用,没有啥大的问题,主要还是要注意vcd文件要自己添加。

本文详细介绍了Verilog语法中的reg与wire的区别、阻塞与非阻塞赋值、parameter与define的差异以及task与function的异同。重点讲解了如何用Verilog实现边沿检测电路,包括上升沿、下降沿和双沿检测,并提供了测试代码及仿真结果。通过实例展示了在edaplayground.com上的仿真流程。

本文详细介绍了Verilog语法中的reg与wire的区别、阻塞与非阻塞赋值、parameter与define的差异以及task与function的异同。重点讲解了如何用Verilog实现边沿检测电路,包括上升沿、下降沿和双沿检测,并提供了测试代码及仿真结果。通过实例展示了在edaplayground.com上的仿真流程。

2332

2332

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?