1.首先interface模块没有变化

interface cnt_if (input bit clk);

logic rstn;

logic load_en;

logic [3:0] load;

logic [3:0] count;

endinterface2.设计模块中使用interface的例化的接口而非端口

module counter_ud (cnt_if cnt_if0);

always @ (posedge cnt_if0.clk or negedge cnt_if0.rstn) begin

if (!cnt_if0.rstn)

cnt_if0.count <= 0;

else begin

if (cnt_if0.load_en)

cnt_if0.count <= cnt_if0.load;

else

cnt_if0.count <= cnt_if0.count + 1;

end

end

endmodule

3.testbench模块也引用interface例化接口

module test (cnt_if cnt_if0);

initial begin

$monitor("[%0t] load_en = %0d;load = %0d; count = %0d",$time,cnt_if0.load_en,cnt_if0.load,cnt_if0.count);

cnt_if0.rstn <= 0;

cnt_if0.load_en <= 1;

cnt_if0.load <= 0;

repeat (5) @(posedge cnt_if0.clk);

cnt_if0.rstn <= 1;

#(10);cnt_if0.load_en <=1;cnt_if0.load<=6;

#(10); cnt_if0.load_en <=1;cnt_if0.load<=8;

#(10); cnt_if0.load_en <=1;cnt_if0.load<=10;

#(10); cnt_if0.load_en <=0;cnt_if0.load<=10;

#(10); cnt_if0.load_en <=0;cnt_if0.load<=10;

repeat (2) @(posedge cnt_if0.clk);

$finish;

end

endmodule4.顶层模块

module top;

bit clk;

always #5 clk = ~clk; //时钟输入

cnt_if cnt_if0 (clk); //interface模块

counter_ud u0 (cnt_if0); //设计模块

test t1 (cnt_if0); //testbench模块

endmodule这就是使用接口的好处,简洁不易出错,便于修改。

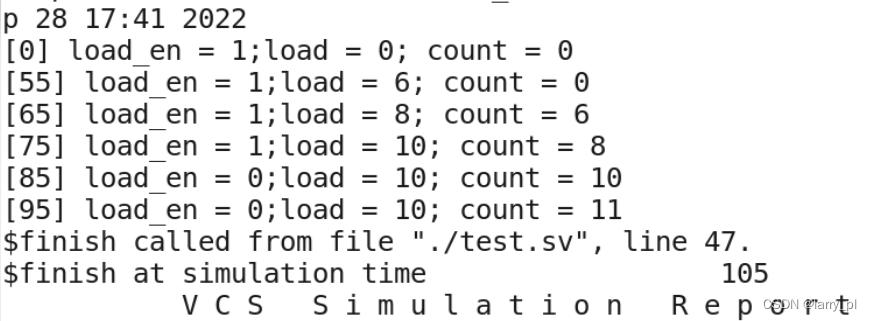

5.SimLog

919

919

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?