`timescale 1 ps/ 1 ps

module a_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk=0;

//reg [15:0] ind;

// wires

reg ind;

wire [7:0] q;

// assign statements (if any)

a i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.ind(ind),

.q(q)

);

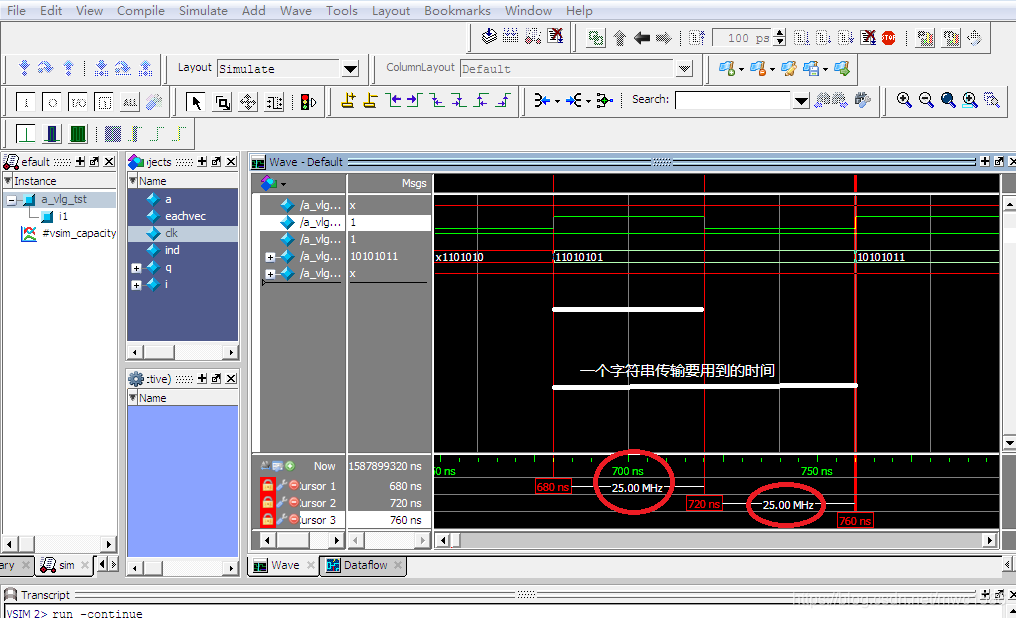

parameter a=40000; //定义时钟频率常量

always #a clk=~clk;

//reg [15:0]k=16'b1010;

integer i;initial

begin

// 1101_0101//

//注意时钟频率需要*2

//例如频率25MHz

#(a*2) ind = 1'b1; //注意时钟频率需要剩以@

#(a*2) ind = 1'b1;

#(a*2) ind = 1'b0;

#(a*2) ind = 1'b1;

#(a*2) ind = 1'b0;

#(a*2) ind = 1'b1;

#(a*2) ind = 1'b0;

#(a*2) ind = 1'b1;

//ind=k;

// --> end

$display("Running testbench");

end

always

// optional sensitivity list

// @(event1 or event2 or .... eventn)

begin

// code executes for every event on sensitivity list

// insert code here --> begin

@eachvec;

// --> end

end

endmodule

这篇博客介绍了如何使用Verilog进行时序测试向量的生成和仿真。通过定义参数、时钟周期以及状态变化,模拟了一个数字逻辑模块的输入输出行为。在测试过程中,关注了时钟频率的正确设置,并展示了如何通过`always`块来控制信号的变化。此外,还讨论了测试向量的重要性以及如何利用它们来验证设计的正确性。

这篇博客介绍了如何使用Verilog进行时序测试向量的生成和仿真。通过定义参数、时钟周期以及状态变化,模拟了一个数字逻辑模块的输入输出行为。在测试过程中,关注了时钟频率的正确设置,并展示了如何通过`always`块来控制信号的变化。此外,还讨论了测试向量的重要性以及如何利用它们来验证设计的正确性。

1922

1922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?