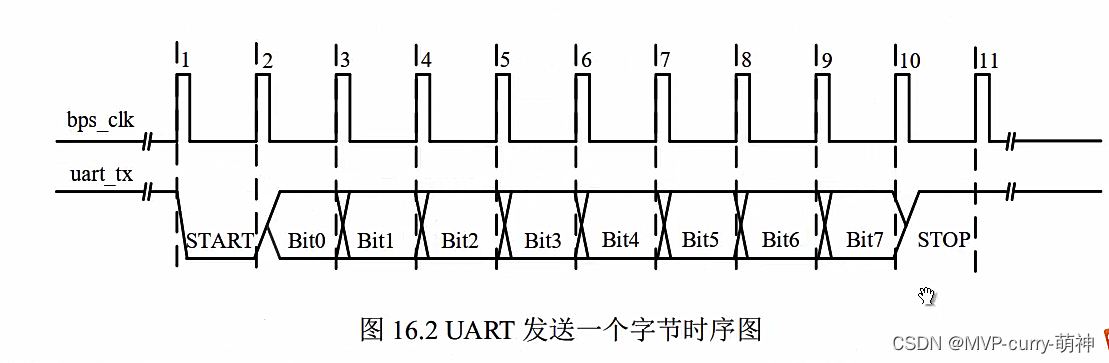

Uart接收端的verilog编写与发送端差不多,其本质区别在于:发送端是将并行输入的数据串行输出,而接收端则是将串行输入的数据并行输出,原理很简单。

问:要接受数据,首先就是判断何时开始接收数据?

答:通过检测起始位的下降沿,一旦检测到下降沿的产生,即为数据的接受开始。

ps:需要检测边沿的理解

为了确保接受过程中数据的正确性和稳定性:

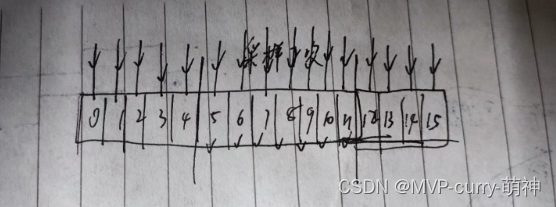

1.为了边沿的影响,所以每一个bit数据采样取中间值 。(在接收单个bit时,将其分为16段,分别取每一个bit的中间段,在通过比较其七小段所加之和与4的大小,来判断接受数据为0或者1)

2.采样取中间值最为稳妥,所以对与每一个bit的16个小段也均取中间点。

`timescale 1ns / 1ps

module uart_rx_byte(

clk ,

rst ,

baud_set,

uart_rx ,

data ,

rx_done

);

input clk ;

input rst ;

input[2:0] baud_set ;

input uart_rx ;

output[7:0] data ;

output rx_done ;

reg[21:0] counter ;

reg[15:0] baud_dr ;

reg[16:0] div16_cnt;

reg[9:0] t160_cnt ;

reg[1:0] r_uart_rx;

reg rx_en ;

reg[2:0] Data[7:0];

reg[2:0] start_d ;

reg[2:0] stop_d ;

reg[7:0] data ;

reg rx_done ;

wire nedge ;

wire bps_clk16;

assign nedge = (r_uart_rx == 2'b10) ? 1 : 0; //起始位下降沿

always@(posedge clk ,negedge rst)begin

if(!rst)

r_uart_rx <=2'b00;

else

r_ua

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

27万+

27万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?