在《浅谈FPGA时序设计》一文中,我笼统的阐述了一下我对FPGA时序设计的理解,这里我分享一个实际工程中遇到的FPGA时序设计的例子。

项目大致情况是用1块FPGA690T和1块DSP6678完成多波段图像目标识别。多波段图像由两路SRIO 1X(简称A路和B路)输入,其中B路是备份,只有在A路失效时,B路才会启动。FPGA需要完成图像的空域和部分时域处理(空域处理是指只处理当前图像,时域处理是指同时处理当前和历史帧图像),将结果和图像通过SRIO 4X发送给DSP。DSP完成最终目标跟踪,然后将结果通过SRIO 1X发送出去。

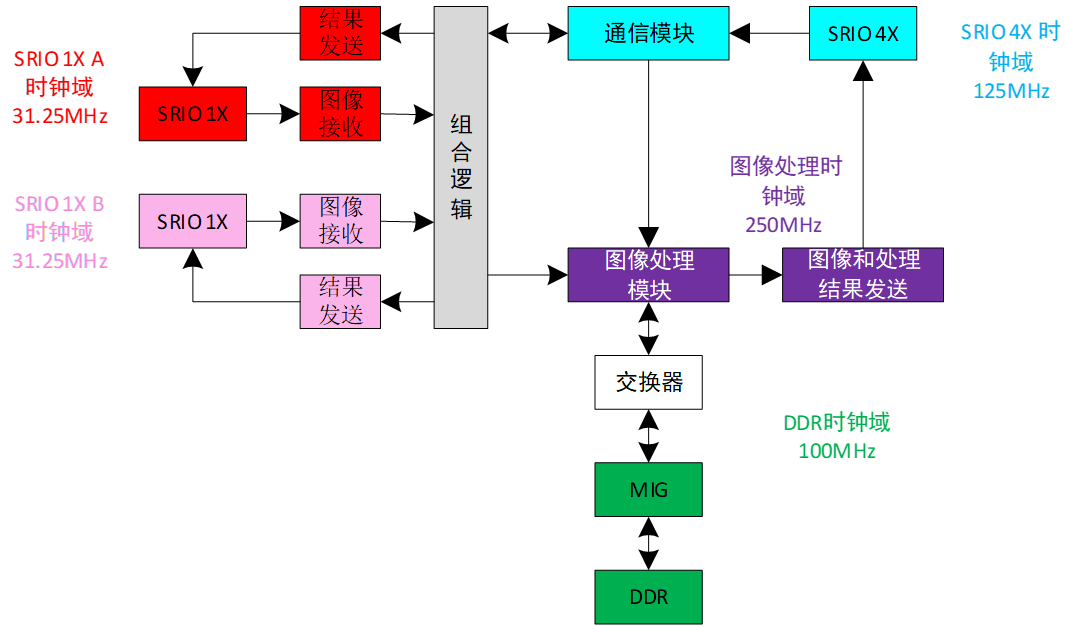

这是最初的FPGA时序分配框图。因为接口频率不高,在资源充足的情况下,这样的设计也没什么大的问题。但实际情况是,因为图像处理设计复杂度较高,导致资源暂用率接近80%。在这种情况下,相互交织的时序关系和组合逻辑的使用就会影响FPGA设计的功能和性能了。

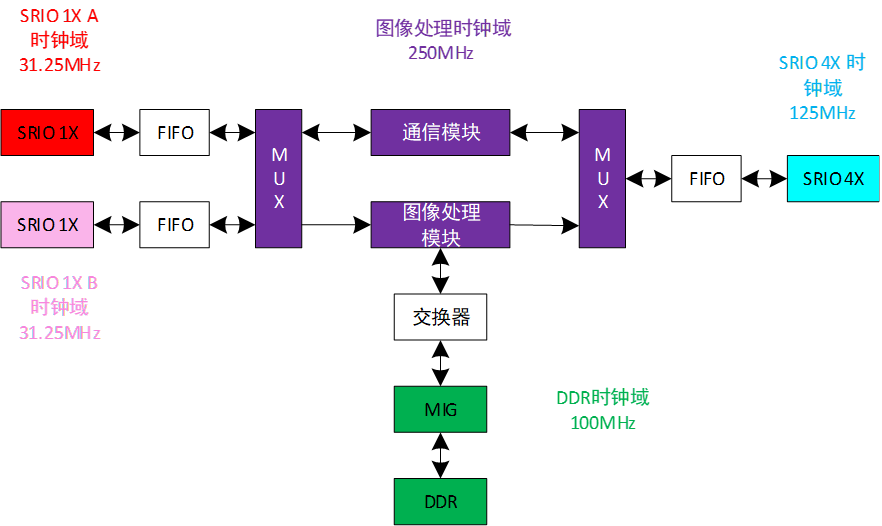

经过分析,我对FPGA的时序进行了重新设计。项目中,FPGA有4个独立的时钟域:2个SRIO 1X、1个SRIO 4X和DDR3时钟域。首先,我选择DDR3的衍生时钟作为主时钟域,用作图像处理。因为衍生时钟和MIG的接口时钟都是由MIG提供,属于同源时钟,使用Xilinx自带的AXI-Interconnector核就可以解决跨时钟域的问题。然后,在SRIO的接口处安置AXIS-FIFO核,用AXIS-FIFO核实现SRIO和衍生时钟的跨时钟处理。这样设计,使得接口时序和图像处理时序分离,时钟分割清晰,减少了组合逻辑,就算图像处理模块需要反复迭代或者修改时钟频率,也不会影响其与接口模块的时序关系。

429

429

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?