在这篇文章中,大家能了解到扇出(fanout)太大是影响FPGA布局布线时序违例的一个主要原因,但只要设计时注意了,这个问题也很好解决。

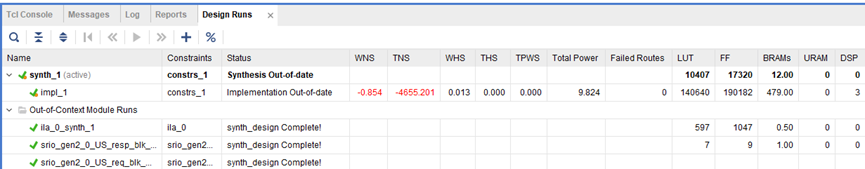

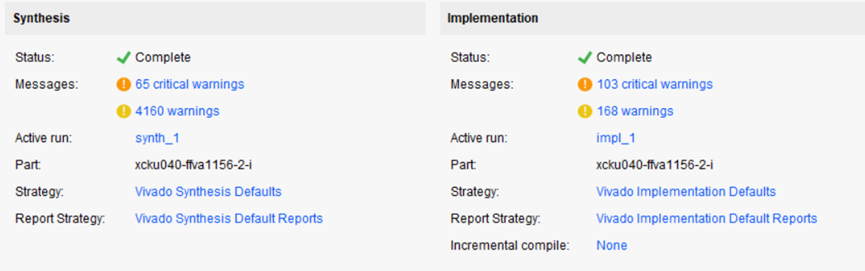

最近我小徒弟又忙起了一个同样光纤项目,不同的是光纤的路数从上个项目的4路上级到了15路。汲取了上个项目时序违例的经验教训,做好了设计的跨时钟域处理,但布局布线后,还是发现时序违例报了-4655.201 ns,就又屁颠屁颠的跑过来,让我帮忙解决。

时序违例报错如下图所示:

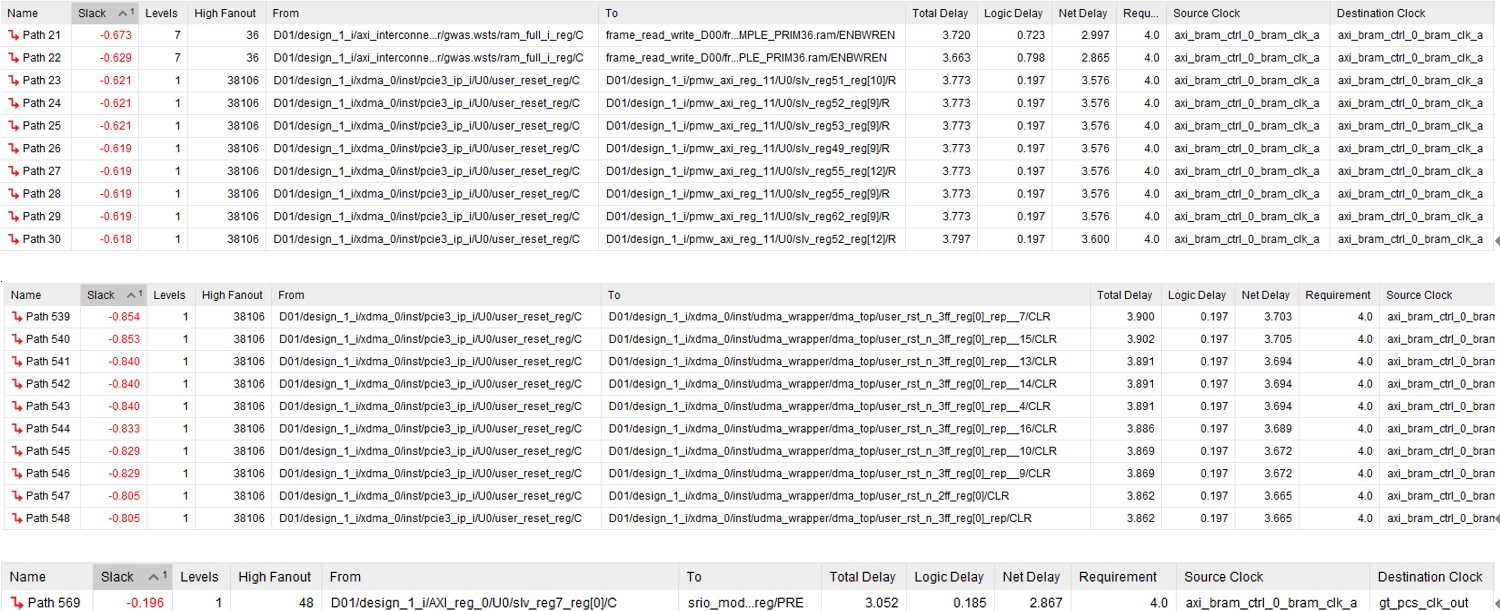

从时序违例的报错分析,这次是报了XDMA复位(resetn)信号的时序违例,仔细一看,原来是复位(resetn)信号的扇出(fanout)太大了,布局布线困难,才导致了时序违例。

扇出(fanout)太大是影响FPGA布局布线时序违例的一个主要原因,那么先解决它。扇出太大的问题比较好解决,把扇出大的信号强制复制减少单个信号扇出数,或者在编译时设置限制单个信号的最大扇出数就可以了。

针对这个工程,我把XDMA核的ARESETN信号复制了16份,并用KEEP属性防止被综合工具综合,再将复制的信号平均的连接到原来连接ARESETN信号的模块。然后布局布线,发现时序违例解决了,本来path21和path22的时序违例也不存在了,应该是布局布线顺利后,综合时给path21和path22通道的时序违例让了道,使得这两条通路也顺利布局布线下去了。

1841

1841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?