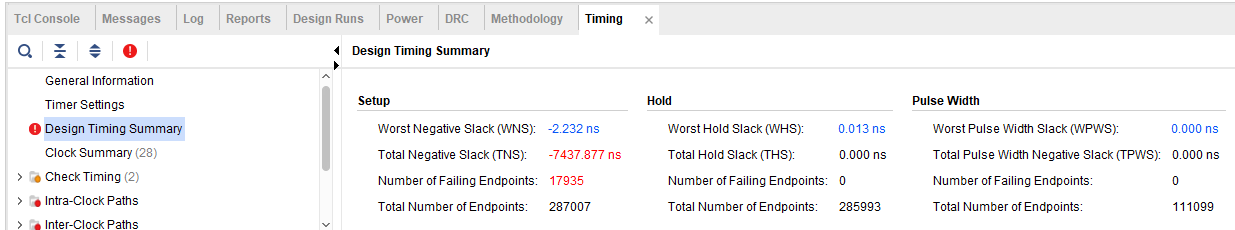

最近我小徒弟在忙一个项目,布局布线后,发现时序违例报了-7437.877 ns,就屁颠屁颠的跑过来,让我帮忙解决。

我让他先把设计的功能框图画出来,然后把各模块的时钟域标注好,如下图。粉色是SRIO时钟域;绿色是MIG时钟域;蓝色是PCIe时钟域;灰色是从SRIO时钟域到MIG时钟域的跨时钟模块。

设计的功能大致是1)SRIO接收图像,写入DDR,然后通知上位机,通过PCIe读走;2)上位机通过PCIe将图像写入DDR,SRIO从DDR读取图像,然后发送出去。

时序违例分析:

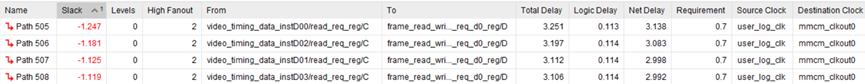

第一个时钟违例,是跨时钟域违例,是从SRIO时钟域到MIG时钟域的read_req(读申请)违例。

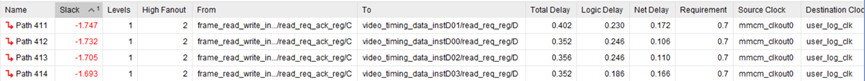

第二个时钟违例,是跨时钟域违例,是从MIG时钟域到SRIO时钟域的read_req_ack(读申请应答)违例。

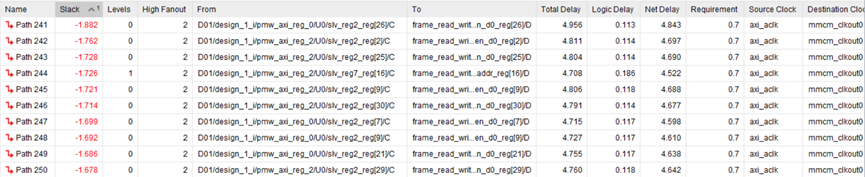

第三个时钟违例,是跨时钟域违例,从PCIe时钟域到SRIO时钟域的寄存器违例。

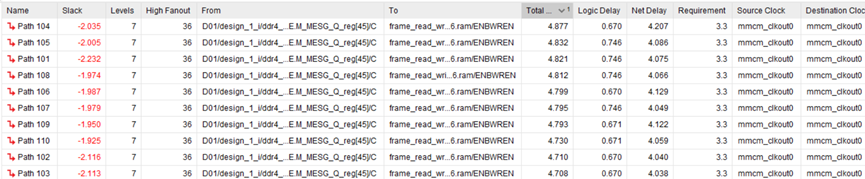

第四个时钟违例,是MIG本身时钟域违例,缓存写使能违例。

解决办法:

分析时钟违例的情况,决定先解决跨时钟域的问题。因为srio_sender_receiver模块需要向frame_read_write模块发送读写请求,frame_read_write模块又需要向srio_sender_receiver模块反馈应答,PCIe寄存器模块需要通过寄存器向srio_sender_receiver模块和frame_read_write模块分配DDR读写地址和读写长度等信息。所以,我认为需要把这几个模块都统一到一个时钟域内。按我的要求,在SRIO和srio_sender_receiver模块之间添加AXIS-FIFO,直接用FIFO完成跨时钟域的问题。SRIO属于SRIO时钟域,过了FIFO后都使用PCIe时钟。MIG的Inter-connector只有Master端使用MIG时钟,其他的Slave端都使用PCIe时钟。因为Inter-connector自带了FIFO,可以完成跨时钟处理。新的时钟域安排如下图所示。

修改完后,重新布局布线,发现时钟违例都解决了。分析认为,解决了跨时钟域的问题,在布局布线的过程中,也方便了第四个时钟违例(MIG本身时钟域违例)的布局布线,从而消除了原有的MIG本身时钟域违例问题。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?