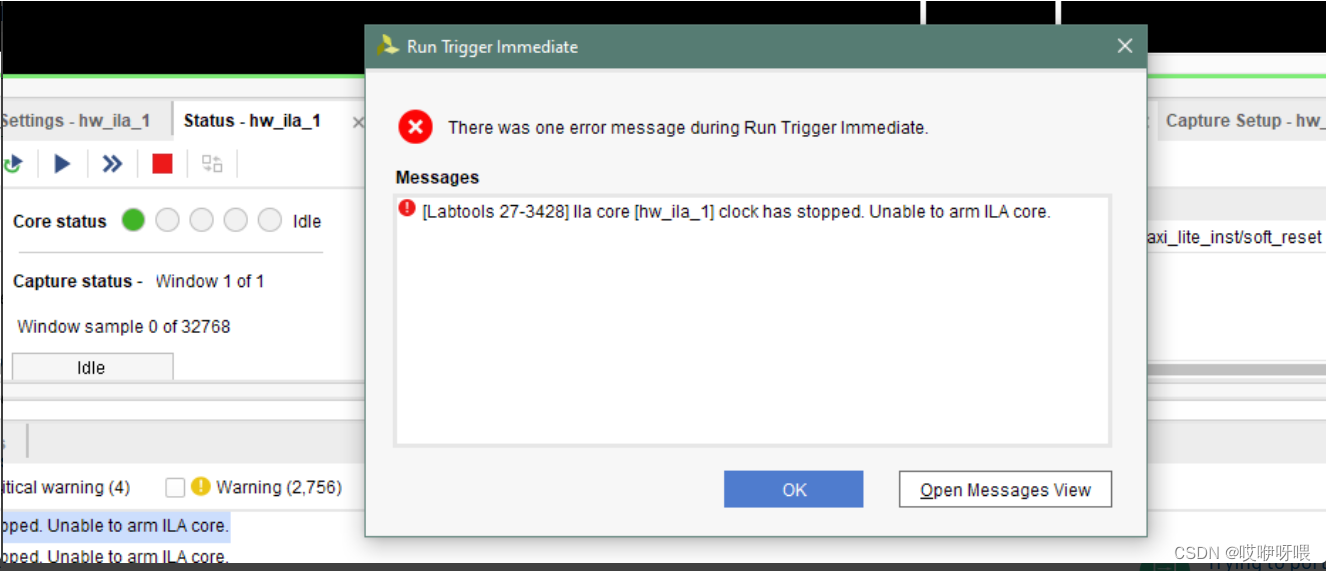

现象:

在调试JESD204B时,为了观察204B的输出信号,采用204B输出的时钟作为ILA的抓数时钟,结果提示ila core clock has stopped. unable to arm ila

分析:

1. 先确定204B的core时钟是否输出,将core时钟进行LED灯的驱动,LED正常闪动,这说明core时钟是出来了的。

2. ILA用其他时钟进行抓数,能够正常抓数。

3. core时钟输出加入BUFG,提示出错,因为JESD204B中已经加入BUFG了。

解决:

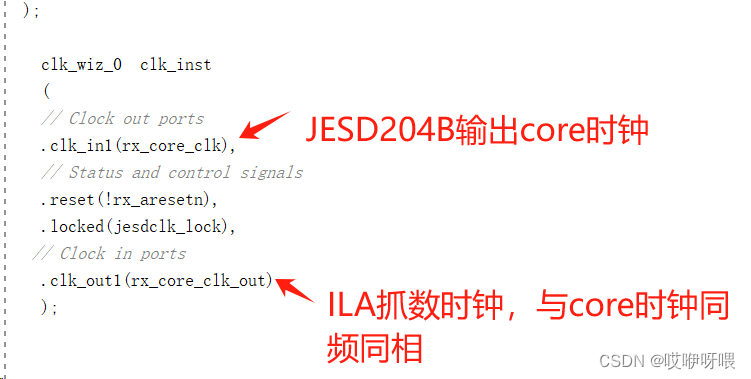

既然JESD204B直接输出的core时钟不能作为ILA的抓数时钟,直接添加一个clock wiz,core时钟作为输入,输出一个和他同频同向作为ILA的时钟,ILA能够运行,测试结果正常!!!!

3326

3326

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?