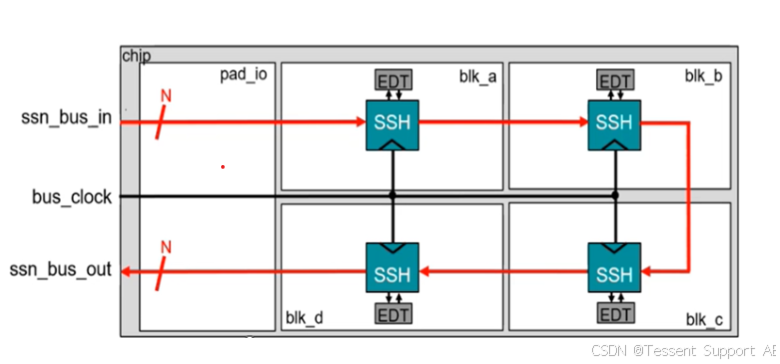

For an SSN design, only the SSN bus data in, SSN bus data out, SSN bus clock, and the TAP pins are needed for ATPG, since the SSN is programmed using IJTAG.

A wide high-speed SSN data bus requires physical resources since the default SSN bus clock frequency is 400 Mhz.

Correctly sizing EDT with SSN is very important since it can reduce the scan data volume per core up to 2.5X compared to a non-SSN design.

SSN bus width: The general recommendation for the is to reuse the same number of GPIO used for EDT channels (scan in/out) without SSN.

The SSN data_in and data_out ports should be symmetrical.

To determine the number of EDT channels: Tessent can help determine the number of EDT channels where test coverage loss is negligible.

For non-identical cores: Use symmetr

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1409

1409

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?