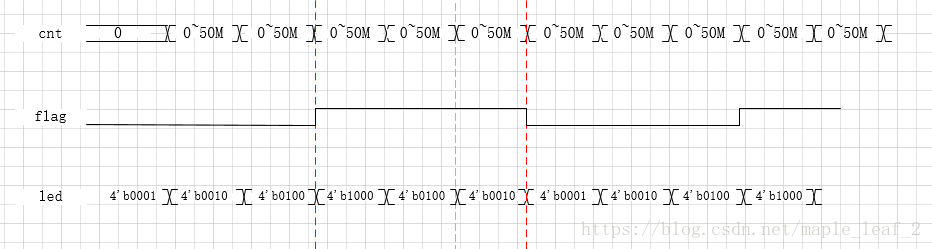

描述:如图定义一个1s的计数器,每隔1s让高电平左移或者右移

定义一个flag信号:

当led==4’b1000时,置为高电平,位拼接让led右移

当led==4’b0001时,置为低电平,位拼接让led左移

module liushui_flag(

input wire sclk ,

input wire rst_n ,

output reg [3:0] led

);

reg [25:0] cnt ;

parameter max = 49_999_999 ;

always@(posedge sclk or negedge rst_n)

if(!rst_n)

cnt <= 0 ;

else

该博客介绍了如何使用Verilog在FPGA中设计一个1秒计数器,通过位拼接控制LED灯进行左移和右移。当LED状态为4'b1000时,标志位设为高,使得LED右移;当LED状态为4'b0001时,标志位设为低,LED左移,形成往返流水效果。

该博客介绍了如何使用Verilog在FPGA中设计一个1秒计数器,通过位拼接控制LED灯进行左移和右移。当LED状态为4'b1000时,标志位设为高,使得LED右移;当LED状态为4'b0001时,标志位设为低,LED左移,形成往返流水效果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5086

5086

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?