目录

前言

时钟信号对于整个芯片的功能有着至关重要的作用,一旦芯片级的时钟信号质量不高,会导致许多不受控的异常bug。

本人目前还尚未接触芯片级时钟设计的工作,所写也均是从网上浏览得到的,会在每个部分标记出出处以及网站。做这篇文章的目的也是为了记录下所浏览到的知识。

1. 时钟的概念与性质

时钟信号,是数字电路的心脏,控制着整个数字电路的状态切换。时钟信号本质仍然是数字信号,即在逻辑0与逻辑1之前不断周期切换。

时钟信号本身指标有幅值、周期、占空比、上升沿时间以及下降沿时间。不过时钟/时钟树还会关注一些关键指标:

- 时钟偏移(clock skew):同一个时钟信号在到达分支的寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。

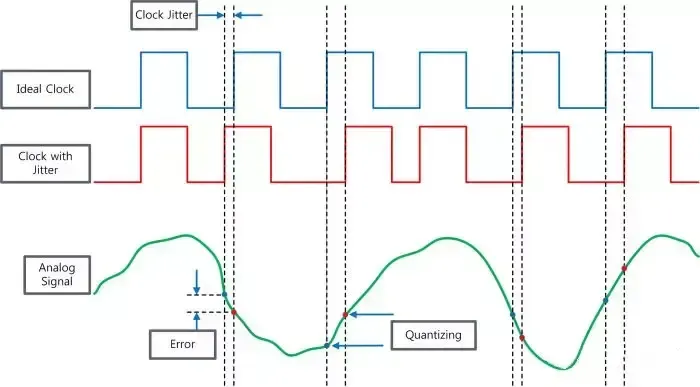

- 时钟抖动(clock jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动。如下图所示:

(图片来源于电子产品的心脏-时钟 - 时钟信号的关键指标 - 知乎)

jitter与时钟频率无直接关系,其可分为随即抖动(Random Jitter,简称Rj)和固有抖动(Deterministic jitter)。

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。

- 时钟转换时间(clock transition):时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间。对于理想的时钟,时钟转换时间为0,反映到图像上则是边沿为直上直下的。但在实际情况下,时钟高低电平是逐渐过渡过去的,过渡所需的时间即时钟转换时间。

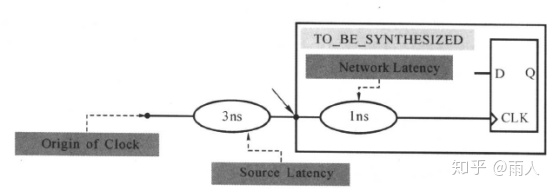

- 时钟延时(clock latency) :时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency),如下图所示:

(图片来源于数字IC设计:时钟信号知识点全解析 - 知乎)

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。

时钟网络延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

上述内容主要来源于:

2. 时钟源

芯片中的时钟信号源主要有三种方案:

- 外部直接输入时钟信号

- 外部晶振+内部时钟发生器(OSC)

- 外部晶振+内部时钟发生器(OSC)+内部PLL产生高频时钟+内部分频器得到各种频率的时钟

从结构复杂度逐渐提升中可以看出,上述三种方案对应芯片的复杂度也是逐渐提升。当芯片逻辑门规模比较小,如一些小规模的ASIC,可能可以考虑第一种时钟方案。而目前SoC芯片主要都采用第三种时钟方案。这个方案的整体思路是先从晶振,时钟发生器产生一个24MHz,再经过PLL产生倍频时钟(高频时钟),最后再经过分频电路产生各种频点的时钟供给各个功能模块。

3. 时钟管理模块

一颗SoC芯片,并不是仅仅只需要得到时钟信号就足够。对于SoC内部各个单元各个模块、所需的时钟需求也并不相同。因此在时钟设计中,时钟管理也是重要的一环。

在SoC中,需要的时钟管理功能主要有三个方向:时钟门控、时钟分频以及时钟切换。

3.1. 时钟门控

时钟门控相关的文章有:

不只是模块级的时钟输入端会放置ICG,在模块内部的寄存器(位宽较大)也可以由DC插入ICG来实现低功耗。

3.2. 时钟分频

时钟分频主要分为奇偶分频(整数分频)以及小数分频,这部分内容我在之前的文章已经分析学习过。[SugerTangYL] 时钟管理(分频器、倍频器、锁相环)Verilog_verilog倍频_SugerTangYL的博客-优快云博客

文章介绍了时钟信号的重要性,包括其概念、关键性质如时钟偏移和抖动,以及时钟源的类型。时钟管理涉及门控、分频和切换,对于SoC芯片设计至关重要。通常,复杂的SoC芯片会使用外部晶振结合内部PLL和分频器来生成所需的各种时钟频率。

文章介绍了时钟信号的重要性,包括其概念、关键性质如时钟偏移和抖动,以及时钟源的类型。时钟管理涉及门控、分频和切换,对于SoC芯片设计至关重要。通常,复杂的SoC芯片会使用外部晶振结合内部PLL和分频器来生成所需的各种时钟频率。

803

803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?