目录

前言

第二个案例来了!做一个函数信号发生器,实现产生四种波形(正弦波、方波、三角波、反三角),输出频率可变以及幅值可变。

一、设计思路

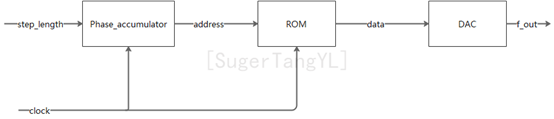

在数字电路中实现函数信号发生器,直接数字式频率合成(DDS)是最常见的方法。DDS的主要模型如下:

由相位累加器、ROM查找表和数模转换器组成,核心为相位累加器和ROM查找表。

对于一段正弦信号来说,其幅度值是非线性的,但是其相位的值却是线性增加的。因此DDS的核心便是通过固定步长产生均匀相位,然后将相位作为地址码去查找该相位的幅度值,从而得到波形。

二、完整代码

module DDS(data,clk,reset);

output [7:0] data;//幅值数据

input clk

本文介绍了一个使用Verilog实现的DDS(直接数字频率合成)函数信号发生器,可以产生四种基本波形:正弦波、方波、三角波和反三角波。设计中利用相位累加器和ROM查找表产生不同频率和幅值的波形,并通过PLL将50M时钟倍频至300M以提高频率上限。代码中还详细解释了相位累加器的工作原理以及如何通过IP核调用来简化设计。

本文介绍了一个使用Verilog实现的DDS(直接数字频率合成)函数信号发生器,可以产生四种基本波形:正弦波、方波、三角波和反三角波。设计中利用相位累加器和ROM查找表产生不同频率和幅值的波形,并通过PLL将50M时钟倍频至300M以提高频率上限。代码中还详细解释了相位累加器的工作原理以及如何通过IP核调用来简化设计。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1010

1010

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?