目录

前言

刚学完APB3.0协议,速速写个文章记录下~可能会写得比较慢,刚上班还有好多东西要学

一、APB概述

APB(Advanced Peripheral Bus,高级外设总线)是AMBA总线协议之一,是一种简单的非流水线协议,可实现Master对Slave状态寄存器(存储空间)进行读写通信,不支持Burst传输。相比于AHB等其他AMBA协议,APB有如下特点:

- 低带宽,低功耗,设计精简

- 主要用于低速IP接口

APB协议要求所有的信号翻转都要发生在时钟上升沿,这样可以便于设计。除此以外,APB协议也有以下特点(其他AMBA Protocol也是如此):

- 与工艺无关

- 没有定义电气特性

- 仅在时钟周期级定义时序

因此对于不同工艺下的APB总线,其模块设计大致相当。具体的时序参数得根据工艺和工作频率来确定。

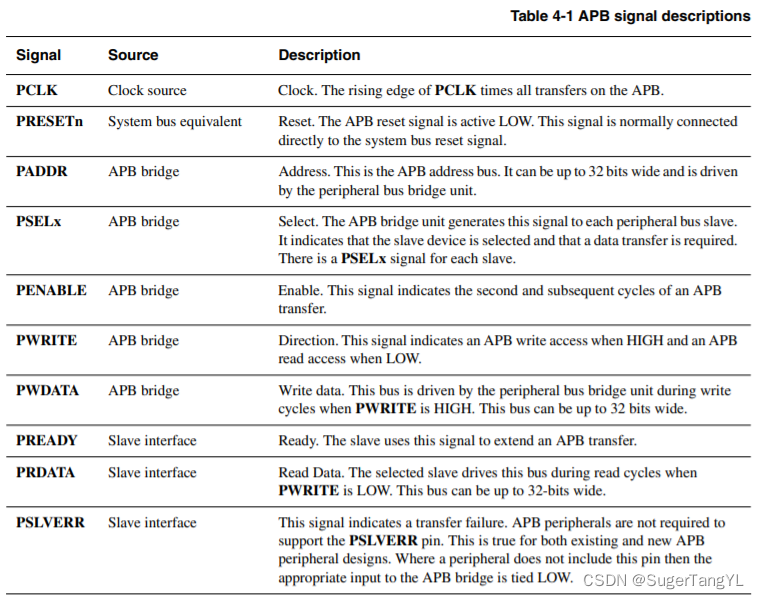

二、信号列表

APB协议的信号以P开头,加以功能来命名。如APB的Address信号,就命名为"PADDR"。下面这个信号列表来源于《 AMBA 3 APB Protocol 》。

下面简单描述一下各信号功能:

- PCLK:APB的时钟,来源于时钟源。

- PRESETn:APB的复位信号,来源于系统复位,n表示低电平有效。

- PADDR:APB的地址数据,最高支持32位,由APB Master输出给Slave。目前APB的主设备大多都是AHB-APB Bridge,因此默认APB的Master是APB Bridge。

- PSELx:片选信号,来源于APB Master,x表示有多个片选信号,在此认为每个Slave都会有一个PSEL信号。当APB Master想要访问某个Slave时,将对应片选信号拉高即可。

- PENABLE:使能信号,来源于APB Master。

- PWRITE:读写控制信号,来源于APB Master,“1”表示写操作,“0”表示读操作。

- PWDATA:APB的Write Data,来源于APB Master,最高支持32位。

- PREADY:Slave对Master访问的响应信号,“1”表示已经准备好了,“0”表示还没准备好。

- PRDATA:Master读取出的数据,来源于Slave,最高支持32位。

- PSLVERR:Slave对Master访问的错误回复信号(Error Respond),“1”表示读写出现了错误,“0”表示没有发生错误,该信号只在最后时刻才认为有效。

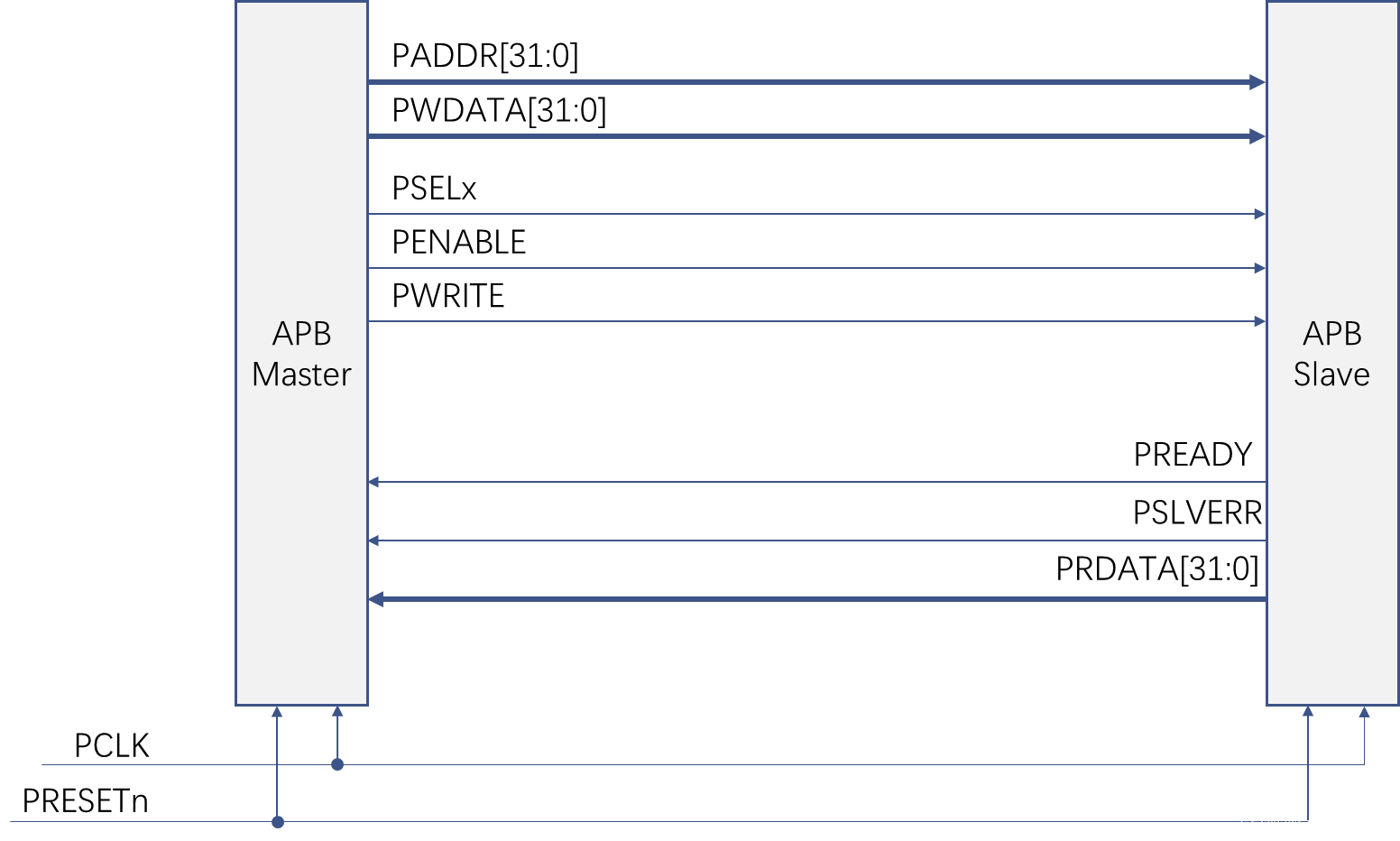

三、APB Interface

(一)一主一从

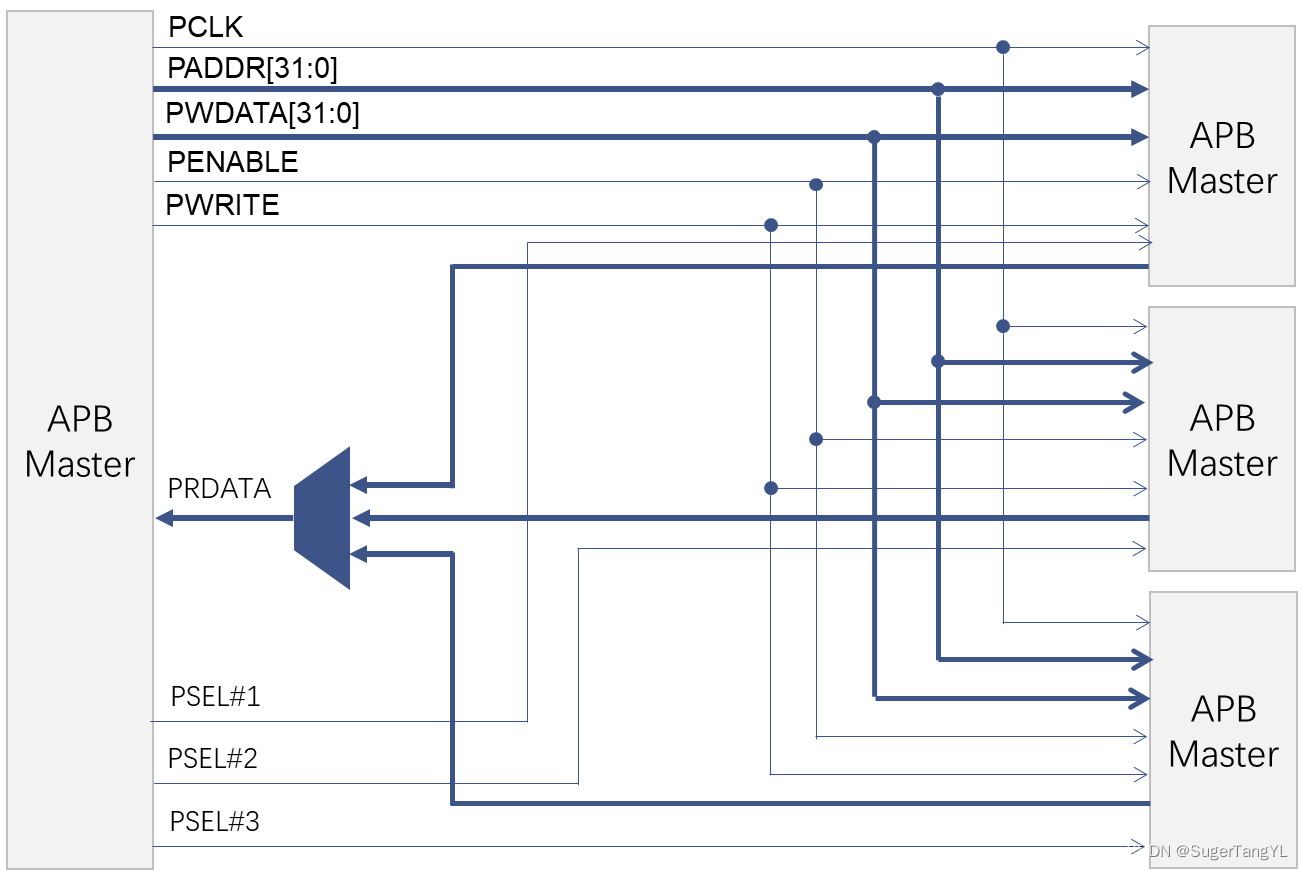

(二)一主多从

一主多从中的MUX也可以换成三态门总线的形式。

四、读写时序

APB总线的读写操作均存在无等待、有等待和出错的情况。一般情况下读写存储器是无等待的情况,比如读状态寄存器、写配置寄存器等;有些时候,读写一些缓存数据的时候,可能缓存正在对外发送/接收数据,因此需要等待才能完成正确的读写;而如果需要写入的存储单元是Read-Only Memory,则需要向Master报错。

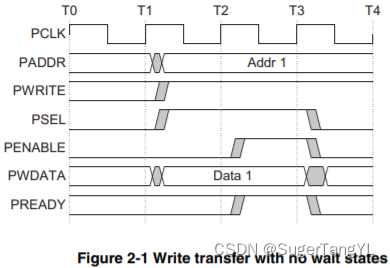

(一)无等待写操作

在T1时刻,时钟上升沿触发,[ APB Master ]将地址、写数据、读写控制信号以及片选信号驱动起来,即PADDR、PWDATA、PWRITE、PSEL,可从时序图中看到各个信号的变化情况。PSEL为"1"时有效,PWRITE为"1"时表示当前是写操作,"0"时表示当前是读操作。

在T2时刻,又一个时钟上升沿触发,[ APB Master ]将使能信号有效,即PENABLE置为"1"。而[ APB Slave ]则将响应信号置"1",即PREADY拉高,PREADY为"1"时表示slave已经准备好接受读写了,为"0"则表示slave还没有准备好,需要Master等待。

在T3上升沿时,PSEL、PENABLE与PREADY均为有效(高电平),此时完成读写操作,将数据写入存储单元或读取对应地址的数据。在这个时刻,Master将PSEL与PENABLE置为"0",从而将Bus总线释放掉。为了降低功耗,可以使得其他信号保持不变,比如PADDR、PWRITE、PWDATA,当下一次传输时再更新其值,从而避免不必要的信号翻转。

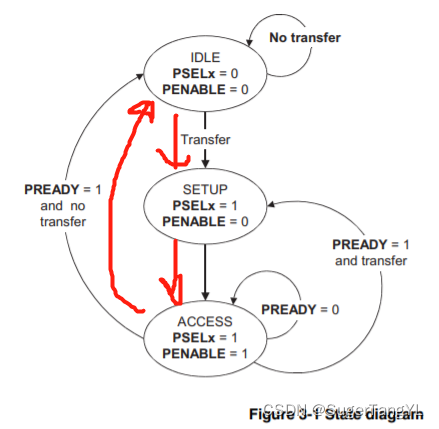

经上述过程,单次APB传输就完成了。协议中对Master做出了状态转移图,包含三个状态:IDLE、SETUP、ACCESS。上面时序图的T0-T1与T3-T4都是IDLE状态、T1-T2是SETUP状态、T2-T3是ACCESS状态。

本次无等待写操作只出现了红色箭头的状态转移,其他转移情况将从下述各情况了解。

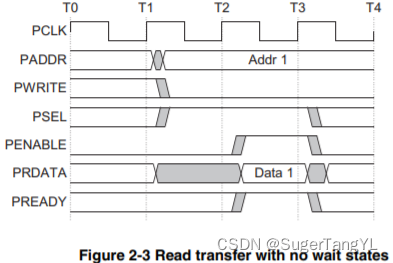

(二)无等待读操作

无等待读操作的许多信号变化与无等待写操作相同,读者可参照写操作的分析方式。两者区别在于,读操作时PWRITE为"0",且此时是从Slave中读出数据PRDATA。对于PRDATA,协议只要求Slave要在完成读操作前(T3时刻对应的上升沿前)将数据加载至Bus上。下面的有等待读操作也是如此,但建议读取的数据仅在时钟沿时条件触发,也就是读写均需要时钟边沿触发的存储器模型,这样会少掉许多无效的翻转。

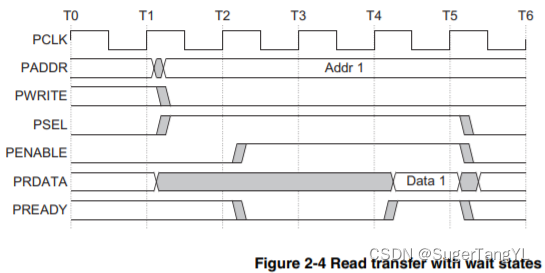

(三)有等待读操作

T0-T1时刻,Master处于IDLE状态。当T1上升沿到来时,Master进入SETUP状态,信号变化与上述相同。T2时Master进入ACCESS状态,将PENABLE使能信号驱动到"1",而Slave则需要根据自身状态做出应答,如果准备好则将PREADY置为"1",此时与无等待传输相同。若Slave此时并没有准备好,则需要将PREADY置为"0",以此告知Master。于是在T3时刻,Master发现PREADY不为"1",就保持各个输出信号不变,等到PREADY等于"1"(Slave已经准备好了),在时钟上升沿完成读操作,然后将控制信号拉低。

如无等待读操作中描述的一样,有等待读操作的读取数据[PRDATA]选择满足条件后再根据时钟沿读出。

注意,协议说明可以插入任意个等待周期,不过在AHB协议是有规定最多等16个时钟周期,具体功能大家可以在协议基础上自行添加咯。

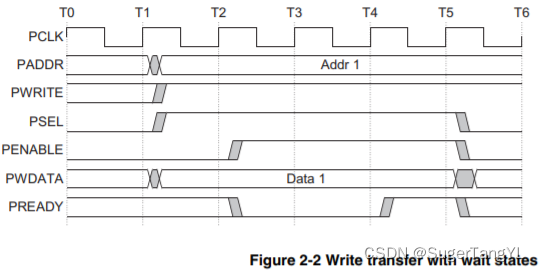

(四)有等待写操作

写操作的等待情况与上面一样,Slave拉低PREADY信号即可实现延迟等待操作。

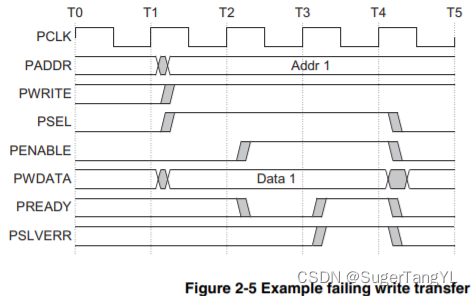

(五)有错误写操作

APB3.0还增加了一个PSLVERR信号,用以指示读写发生了错误。具体时序如上,T3时刻之前均是上面所讲过的状态。如果本次写操作存在错误(如写地址为只读存储器地址),Slave则需要与PREADY同时给出PSLVERR信号,这样在T4时刻,Master发现PSEL、PENABLE、PREADY与PSLVERR均为"1",便知道本次写操作出错。

PSLVERR信号仅在要完成读写操作的那个时钟沿才被考虑(认为它有效),也就是说读写操作的时候也是需要同时判断是否出错滴。

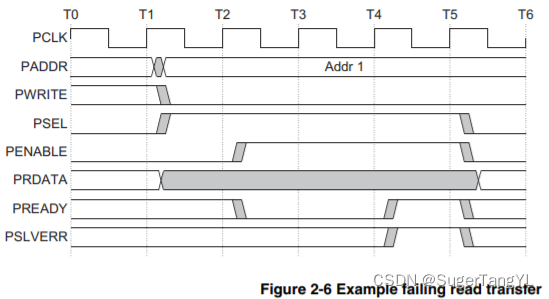

(六)有错误读操作

读操作的报错时序与写操作的一样,也是在PREADY信号驱动的同时,驱动PSLVERR。

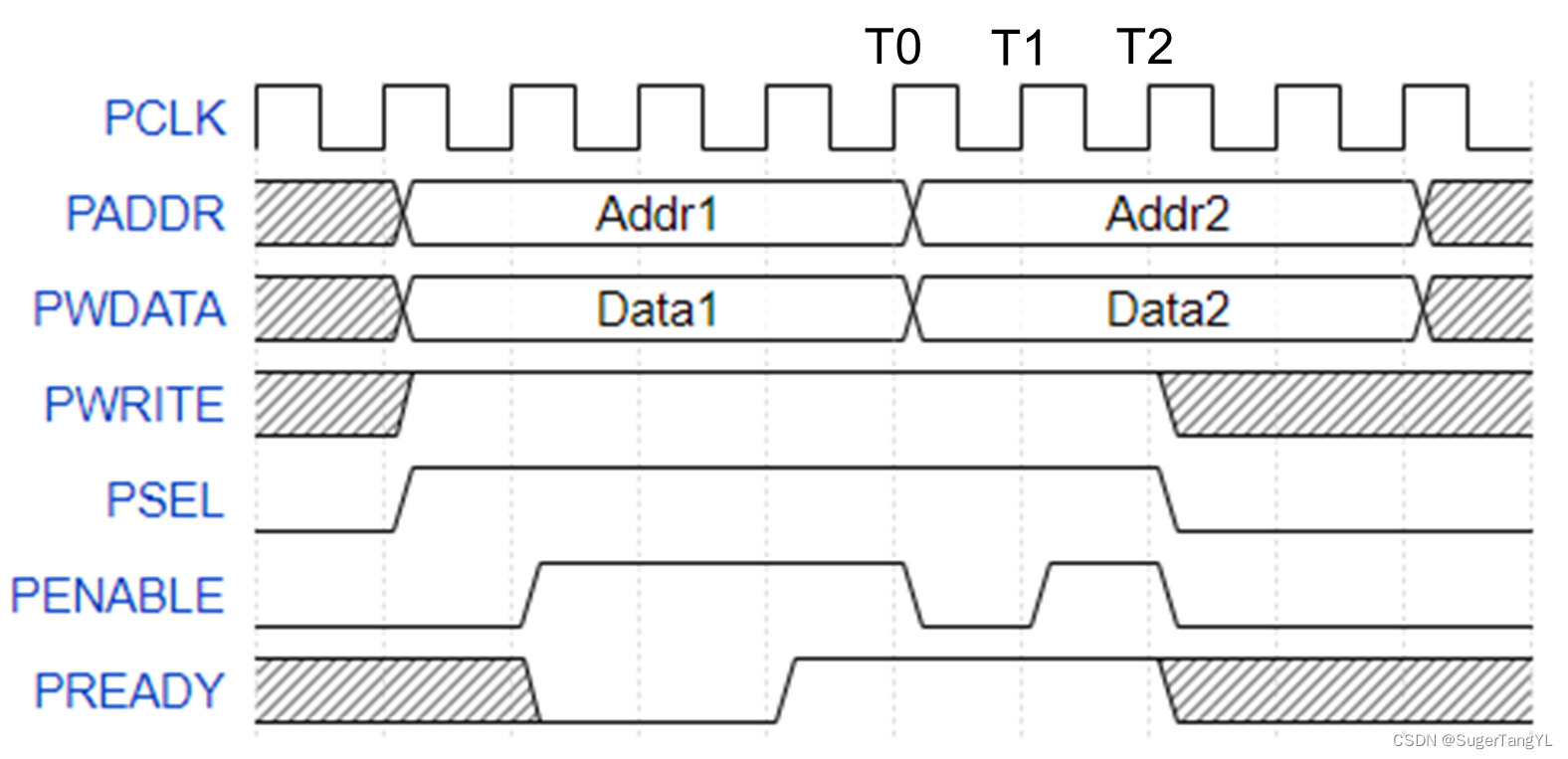

(七)连续操作

协议里有提到连续读写操作的事,上面是我理解的连续读写时序图。可看到在T0时刻完成了Data1的写入,Master并没有将PSEL置为"0"(即Master没有变为IDLE状态),而是仅仅只将PENABLE置为"0"了,即Master变为SETUP状态。然后T1时刻Master又进入ACCESS状态,将PENABLE使能信号置为"1",然后在T2时刻完成Data2的写入。如果连续次数更多,则可看到PENABLE信号"1""0""1""0"的翻转(如果没有需要等待的情况的话)。

结尾语:过了一周,确实已经忘了还需要讲什么了,暂时就这些吧。

本文介绍了APB3.0协议的基本概念,包括信号列表、一主一从与一主多从接口配置以及读写时序。APB作为低带宽、低功耗的总线,适用于低速外设接口。详细阐述了无等待和有等待的读写操作,以及错误处理时序,帮助理解APB协议的工作原理。

本文介绍了APB3.0协议的基本概念,包括信号列表、一主一从与一主多从接口配置以及读写时序。APB作为低带宽、低功耗的总线,适用于低速外设接口。详细阐述了无等待和有等待的读写操作,以及错误处理时序,帮助理解APB协议的工作原理。

https://web.eecs.umich.edu/~prabal/teaching/eecs373-f12/readings/ARM_AMBA3_APB.pdf#:~:text=1.1%20About%20the%20AMBA%203%20APB%20The%20APB,bus%20interface.%20The%20APB%20has%20unpipelined%20protocol.%20

https://web.eecs.umich.edu/~prabal/teaching/eecs373-f12/readings/ARM_AMBA3_APB.pdf#:~:text=1.1%20About%20the%20AMBA%203%20APB%20The%20APB,bus%20interface.%20The%20APB%20has%20unpipelined%20protocol.%20

2万+

2万+