目录

前言

来分享第一个案例了!简易电子时钟的Verilog设计,电子时钟应该算是走嵌入式和FPGA开发的敲门砖了叭(也可能是流水灯)。本次设计实现的平台是Altera的DE2开发板。

一、简易电子时钟的功能要求

一个简易的电子时钟应该包含以下功能:

- 正常显示时分秒

- 可调节时间

在此基础上也还可以继续扩展功能,本次由于刚入门,便只实现了基本功能。

二、设计思路&整体框架

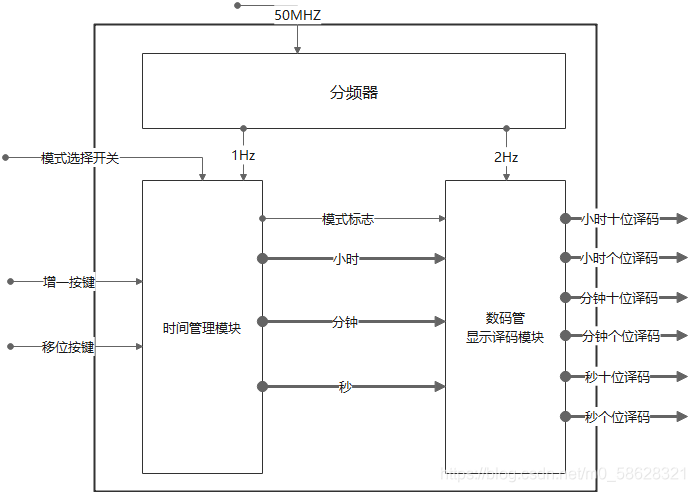

要正常计时,我们需要一个1Hz的信号。在Verilog中采用分频器对基准时钟进行分频,使用这个1Hz信号进行计数,便可以产生时分秒。再将时分秒用数码管显示出来,第一个功能成功实现;在第一个基础上,设置一个拨码开关,用以区分正常模式和调时模式。当电子时钟处于调时模式时,最低位数码管闪烁,按下增1按键时数字加1;按下移位按键时闪烁位向高位移动。当模式调回正常模式时,从修改后的时间开始计时。

综上,需要一个分频器、一个时间管理模块、需要六个数码管显示译码器。整体框图如下:

对于分频器这一ip,之后会出文详述,此处使用的是占空比50%的偶分频。数码管显示译码模块属于较为简单的模块,读者在看其Verilog代码时很容易便理解。

三、完整代码

本文详细介绍了使用Verilog语言设计简易电子时钟的过程,包括功能要求、设计思路、整体框架和部分代码展示。通过分频器产生1Hz信号,结合时间管理模块和数码管显示译码,实现时分秒的正常显示及调时功能。此外,还讨论了如何通过拨码开关切换正常模式和调时模式,并提供了关键代码段。

本文详细介绍了使用Verilog语言设计简易电子时钟的过程,包括功能要求、设计思路、整体框架和部分代码展示。通过分频器产生1Hz信号,结合时间管理模块和数码管显示译码,实现时分秒的正常显示及调时功能。此外,还讨论了如何通过拨码开关切换正常模式和调时模式,并提供了关键代码段。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8262

8262

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?